利用現場可編程門陣列技術設計自動鈴聲系統

[摘要]隨著數字電子技術和集成電子電路技術的飛速發展,掌握EDA技術、學會用VHDL語言設計設計電子電路是每個硬件設計工程師必須掌握的一項基本技能。用VHDL語言、MAX+plusII開發平臺設計一個自動鈴聲系統,底層采用VHDL語言、頂層采用原理圖輸入的方法,在開發平臺上進行編譯、功能仿真、時序仿真,最后下載到FPGA開發板上進行實際調試。

[關鍵詞]EDA VHDL FPGA 鈴聲系統

中圖分類號:TP2文獻標識碼:A 文章編號:1671-7597(2009)0110036-02

一、引言

隨著大規模集成電路技術和計算機技術的不斷發展,在涉及通信、國防、航天、醫學、工業自動化、計算機應用、儀器儀表等領域的電子系統設計工作中,EDA(Electronic Design Automation,電子設計自動化)技術的含量正以驚人的速度上升,電子類高新技術項目的開發也更加依賴于EDA技術的應用。因此,本文使用VHDL(Very high speed integrated circuit Hardware Description Language,甚高速集成電路硬件描述語言)進行程序編制,設計實現自動鈴聲系統,采用EDA設計軟件MAX+plus II進行編譯、仿真、綜合,然后下載到FPGA上進行實際驗證。

二、功能分析

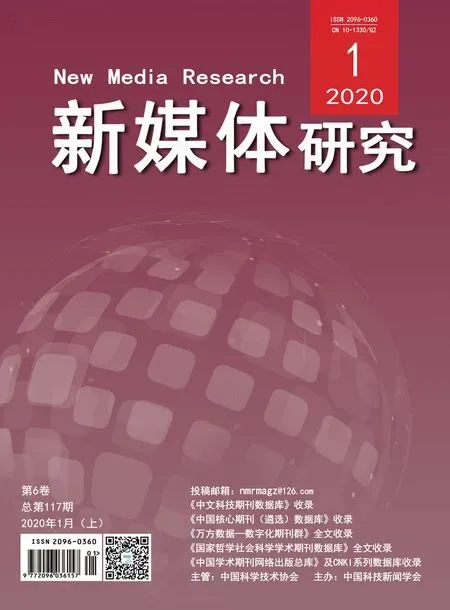

系統應該具有基本計時、能設置當前時間、能調整起床鈴時間、熄燈鈴時間、能調整打鈴時間長短和間歇時間長短等五項基本功能。為了能夠同時查看當前年月日星期以及能夠采用24小時制,在設計中加入年、月日的調整及與時間同步走時、切換12/24時制等三個功能。星期是與某一年月日相對應的固定參數,在年月日調整時設為不可見。于是八個功能組成八種狀態,那么采用狀態機進行各個狀態的切換是最方便的。

本系統具有八個狀態共八個參數,需要根據各個狀態出現的順序和打鈴信號燈的亮、滅情況進行相應顯示,那么可以設計“顯示控制及打鈴控制模塊”來統一進行操作。

另外如果實驗室開發板上沒有按鍵消抖電路,那么有必要再加上軟件消抖程序。于是本系統的原理框圖如圖1所示。

三、硬件設計

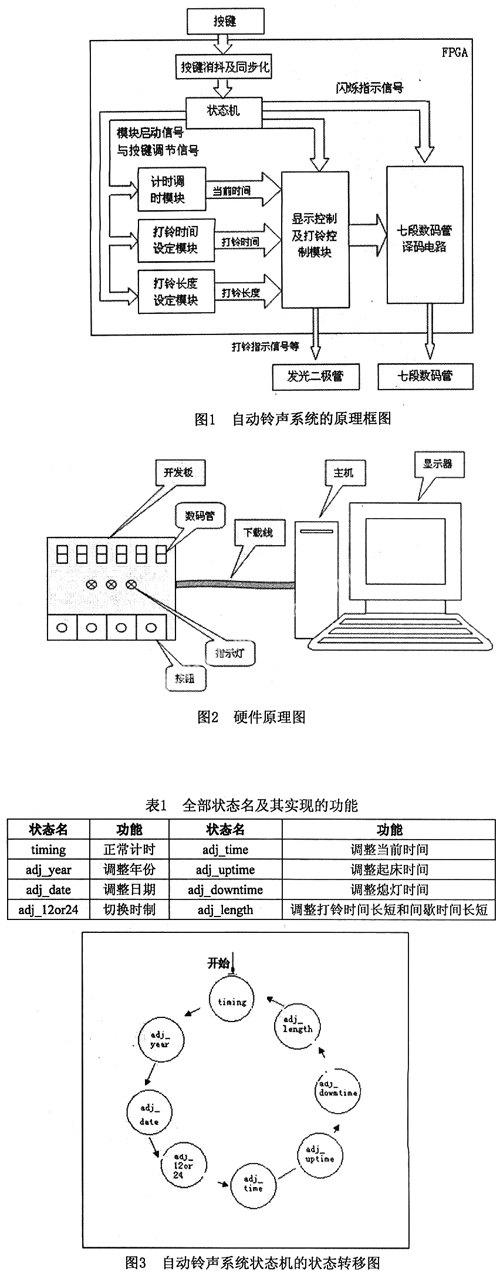

本設計采用的開發板是SpartanII開發系統。其原理圖比較簡單,如圖2所示。

(一)狀態機的設計原理

狀態機的具體實現如前所述,8個功能模式對應8種狀態,因此設定的狀態如表1所示。

那么這8種狀態的轉移圖容易得到如圖3所示。圖中默認處于正常計時狀態timing,當按鍵changemode有效按一下就從timing開始轉到箭頭所指的狀態adj_year。以此類推。狀態機通過讀入按鍵值進行狀態切換并執行某些特定操作,所以這里應用Mealy型狀態機。在這里將使用三個按鍵來執行相關切換。

(二)主要模塊設計

1.計數器的設計

這里涉及3個參量即年、月日、時間的變化,因此可設置3個調整使能信號en1(調“年”使能)、en2(調“月日”使能)和en3(調“時間”使能),分別對應狀態機的輸出信號mode的mode[0]、mode[2]和mode[4]。

2.響鈴時間設定

利用接口電路實現時間設定并進行仿真。

3.顯示控制及打鈴控制模塊

該模塊集中了前面幾個模塊的輸出信號根據狀態機所給出的狀態分別進行顯示。

4.按鍵消抖及同步化輔助模塊

鍵盤的按鍵閉合與釋放瞬間,輸入端信號會有毛刺。如果不進行消抖處理,系統會將這些毛刺誤以為是用戶的另一次輸入,導致系統的誤操作。因為人按鍵的時間大約為10ms,不可能有更快的按鍵動作發生。這里將10ms作為分界,把小于10ms的按鍵動作視為抖動,而時間長達10ms及以上的視為有效按鍵。

四、結論

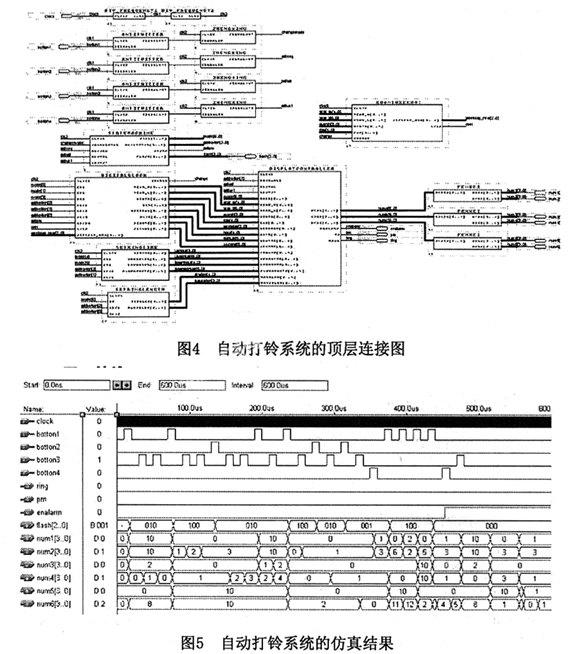

綜上所述,最終的電路連接圖如圖4所示,根據對它進行的仿真,如圖5所示,說明該系統能夠正確實現其功能。本文增加了“年月日星期”的切換顯示,并且其值可調,使得自動打鈴系統已經不是單純的計時器,而是一本“日歷”,這樣在功能擴展時可以做到:如果周末休息不需要上下課打鈴,只需在“顯示控制及打鈴控制模塊”里加上當星期weekday<=5時才執行下面的打鈴功能。如果有條件可以考慮使用液晶顯示屏進行多個參數“同時”顯示,而鈴聲可使用專用芯片的真人發聲或音樂提示,提高系統的人性化特征。同時要考慮其成本也會相應增加,這是在進行產業化設計中必須考慮的問題。

參考文獻:

[1]侯伯亨、顧新,VHDL硬件描述語言與數字邏輯電路設計(修訂版),西安電子科技大學出版社,2004.

[2]張展、王亞洲,基于EDA技術的自動打鈴器設計,電子世界,2003,(04).

作者簡介:

羅華陽,男,湖南邵東人,湖南鐵路科技職業技術學院,講師,研究方向:自動控制與通信技術。