基于DDS技術的多路同步信號源的設計

孫永亮 張忠友

摘 要:多路同步數字調相信號源一般采用單片機和多片專用DDS芯片配合實現。該技術同步實現復雜,成本高。給出了一種基于FPGA的多路同步信號源的設計方法,通過VHDL語言硬件編程實現了基于單片FPGA的多路同步信號,數字調相快速準確。利用QuartusⅡ進行綜合和仿真驗證了該設計的正確性,該設計具有調相方便、速度快、成本低等優點。

關鍵詞:DDS;多路同步;VHDL;FPGA

中圖分類號:TN911文獻標識碼:B

文章編號:1004-373X(2009)05-020-03

Design of Synchronized and Continuously Tunable Multi-routing

Signal Source Based on DDS Technology

SUN Yongliang,ZHANG Zhongyou

(College of Science,Air Force Engineering University,Xi′an,710051,China)

Abstract:The synchronized and continuously tunable multi-routing signal sources are generally based on combination of a Micro Control Unit (MCU) and multiple specialized DDS chips.However,the realization of synchronization is difficult due to technology complications and high cost.In this paper,a design for a synchronized multi-routing signal source based on a single FPGA micro unit by VHDL hardware programming is proposed.It has good synchronization between multi-routing signals,and is continuously tunable and cost-efficient.This design is verified by integration and simulation through Quartus II.Experiments show that this design is simple and highly applicable.

Keywords:DDS;synchronization of multi-routing signals;VHDL;FPGA

0 引 言

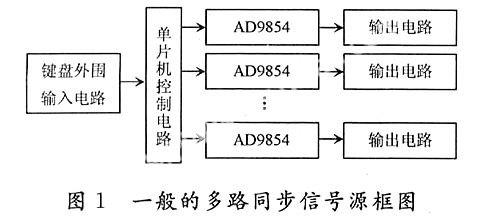

實現信號源的多路同步輸出,在雷達、通信等多領域有著重要的應用。為了實現此功能,大多數設計是利用多個專用DDS芯片外圍借助單片機幫助,實現多信號同步輸出,如圖1所示。

系統工作時,根據鍵盤輸入,單片機輸出頻率控制字和相位控制字以及波形選擇字,控制專用DDS芯片AD9854產生特定頻率和相位的波形,經濾波放大后輸出要求的模擬波形。為輸出頻率相同,相位相關的多路同步信號,控制數據由鍵盤輸入,單片機向各專用DDS芯片輸出相同的頻率控制字和不同的相位控制字指令,控制各專用DDS芯片輸出指定的頻率和相位的波形。這樣就從整體上實現了頻率和相位的連續可調及同步。

AD9854是美國AD公司的DDS系列產品,性能良好,頻率可調范圍寬。在這樣的設計中,利用AD公司的AD9854芯片,盡管有頻率可調范圍寬,波形豐富,實現調副、調頻容易等特點,但是由于是采用分立的專用DDS芯片,各芯片參數很難做到完全相同,參數的差異會造成輸出信號頻率和相位不同。因此,盡管各DDS芯片采用同一頻率字,各個輸出信號頻率也難以完全相同。同樣,由于參數的不一致,波形之間的相位也難以準確調整到位,更重要的是各個信號頻率差異的累積效應可能會導致同步失敗。另外,專用DDS 芯片價格昂貴,設計成本也較高。

基于以上原因,這里給出一種基于單片FPGA的多路同步信號源的設計方案,這種方案具有實現簡單、同步性好等優點,且成本較低。

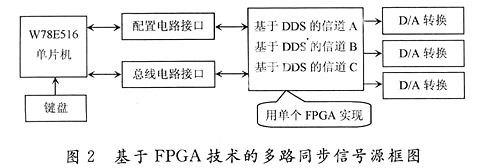

1 基于FPGA技術的多路同步信號源的設計模型

基于FPGA技術的多路同步信號源的整體框圖如圖2所示。

在本框圖中,以三路輸出為例,在一個FPGA芯片中,實現了三路基于DDS的信號通道,完成傳統上三個專用DDS芯片AD9854完成的功能,實現三路波形的數字輸出,在數字信號輸出后進行D/A轉換,實現三路信號的模擬輸出。三個DDS信道頻率取自同一個累加器輸出的地址值,進行查表,同時相位的加法實現也是針對同一個累加器輸出的地址,消除了分立專用DDS芯片計算的誤差。由于在一塊芯片中實現,所以各DDS信道的參數一致性好,分立專用DDS芯片的外部連線帶來的延時誤差也被降到最低。因此,通過以上措施,可以大大改善信號的一致性,可實現精準的相位連續調節。

單片機及總線配置電路通過鍵盤實現人機接口。通過4×4矩陣式鍵盤可以將頻率選擇、初始相位選擇等數據輸入單片機并經單片機處理后送FPGA,實現DDS的調整。

FPGA是完成DDS多信號產生的核心部件,完成DDS多路同步信號的產生。

2 基于DDS技術的多路同步信號輸出的FPGA核心設計

2.1 一般DDS的工作原理

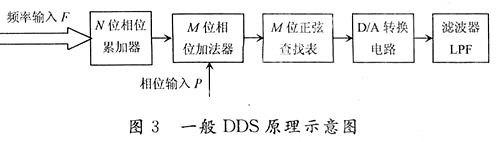

DDS(Direct Digital Synthesizer)是從相位概念出發直接合成所需的波形的一種頻率合成技術。一個DDS信號發生器是由:相位累加器、波形數ROM 表、D/A轉換器以及模擬低通濾波器LPF組成,原理框圖如圖3所示。DDS技術的核心是相位累加器,相位累加器在穩定時鐘信號的控制下產生讀取數據的地址值,隨后通過查表變換,地址值被轉化為信號波形的數字幅度序列,再由數/模變換器(D/A)將代表波形幅度的數字序列轉化為模擬電壓,最后經由低通濾波器將D/A輸出的階梯狀波形平滑為所需的連續波形。相位累加器在時鐘F<sub>c</sub>的控制下以步長F作累加,輸出的值與相位控制字P相加后形成查表的地址值,對波形ROM進行尋址。波形ROM的輸出值即是幅度值,經過D/A變換后形成階梯狀的波形,最后通過低通濾波平滑成所需的波形。合成信號的波形取決于ROM表中的幅度序列,通過修改數據可以產生任意波形,如果要產生多種波形,只需把所需的多種波形數據存放到波形ROM表中。

一般DDS的原理示意圖如圖3所示。

2.2 同步多路輸出DDS的工作原理

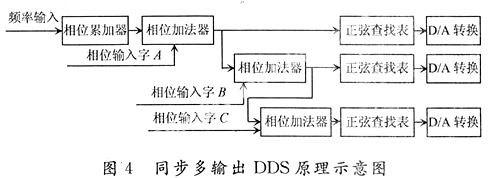

同步多路輸出DDS工作原理示意圖如圖4所示。

由方框圖可以看出,從同一個相位累加器輸出的地址值在進行查表之前,根據需要有不同的相位字進行加法運算,再根據新的地址進行查表,從而形成波形之間需要的相位值。由于各個輸出信號是在DDS內對同一個累加器輸出的地址進行相位的加法,參數一致,相位的可調性非常好。頻率取自同一頻率字,各個信號存在固定的同步同頻特性,因此輸出的信號源同步性能優越,完全滿足設計要求。

2.3 相位累加器的設計

相位累加器是DDS設計的核心部件。本設計相位累加器由32位加法器與32位寄存器級聯構成。累加器將加法器在上一個時鐘作用后所產生的相位數據反饋到加法器的輸入端;使加法器在下一個時鐘作用下繼續與頻率控制字(K)進行相加,實現相位累加,當相位累加器累加結果等于或大于232時就會產生一次溢出,回到初始狀態,完成一個周期性的波形輸出。本設計累加器用VHDL語言[quartus6.0]設計實現如下:

32位累加器模塊實現:

library ieee;--32位累加器

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity adder32b is

port(a:in std_logic_vector(31 downto 0);

b:in std_logic_vector(31 downto 0);

clk0:in std_logic;

s:out std_logic_vector(31 downto 0) );

end adder32b;

architecture behav of adder32b is

begin

process(clk0)

begin

if clk0'event and clk0= '1' then

s<=a+b;

else null;

end if;

end process;

end behav;

2.4 波形存儲器的設計

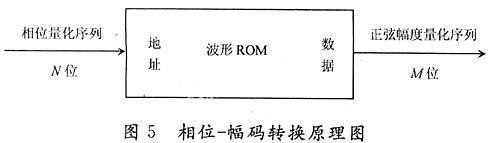

用相位累加器輸出的數據作為波形存儲器的取樣地址,進行波形的相位-幅碼轉換,即可在給定的時間上確定輸出的波形的抽樣幅碼。本設計利用FPGA資源,構造一個10位的ROM進行數據的存儲和轉換。

ROM可利用Quartus的插件管理程序Megawizard plug_in manager容易獲得,這里給出正弦波形數據生成的C程序,來生成ROM存儲的數據。要想生成其他波形的數據,只需要簡單修改其中的波形表達式即可。

#include″stdio.h″

#include″math.h″

#define N 256/*N is the DEPTH of the table(數據個數也就是一個周期采樣點數)*/

#define P 10 /*P is the Precision of data in the table(數據精度也就是一個數據的位數)*/

void main()

{FILE *fp;

double y,bias,amp;

int n;

if((fp=fopen(″sindata.c″,″w″))==NULL)

{printf(″cannot open this file\n″);

exit(0);

}

fprintf(fp,″WIDTH=10;\n″);

fprintf(fp,″DEPTH=256;\n″);

fprintf(fp,″ADDRESS_RADIX=DEC;\n″);

fprintf(fp,″DATA_RADIX=DEC;\n″);

fprintf(fp,″CONTENT BEGIN\n″);

bias = amp = pow(2,P-1)+0.5;

for(n=0;n<=N-1;n++)

{y=bias+amp*sin(n*3.1415936535/(N/2));

if(fmod(n,10)==0)

{fprintf(fp,″\n″);}

fprintf(fp,″%4d:%4.0f;\n″,n,y);

}

fprintf(fp,″END;″);

fclose(fp);

}

3 仿真與調試

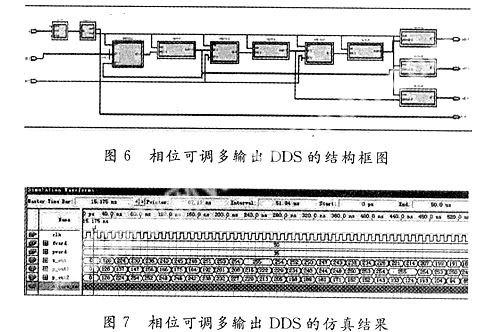

本設計在Quartus Ⅱ中進行分析和綜合后,得到該相位可調多輸出DDS的結構如圖6所示。

在Quartus Ⅱ中,輸入控制信號:F<sub>c</sub>=100 MHz,fword=50,pword=35,進行仿真,其仿真結果如圖7所示。在Quartus中生成的仿真數據經過驗證完全正確,得到了同頻和可調相的三個正弦波的幅值數據序列,完全滿足設計要求。

4 結 語

本設計運用VHDL硬件編程語言和DDS技術,結合FPGA高速器件,實現了多路信號的同步輸出,很好地解決了要求信號之間同頻率可調,相位連續可調的問題,且具有易于程控、相位連續、輸出頻率穩定度高、分辨率高等優點,并且采用一個FPGA塊就解決了傳統上需要三個DDS才能解決的問題,也大大降低了設計成本。

參考文獻

[1]潘松,黃繼業.EDA技術與VHDL.2版.北京:清華大學出版社,2007.

[2]陸春妹.基于DDS技術的數字信號發生器的設計.蘇州市職業大學學報,2007,18(2):55-57.

[3]Phillip E Allen,Douglas R Holberg.CMOS Analog Circuit Design.Beijing:Publishing House of Electronics Industry,2005.

[4]王玉珍,李袁柳.直接數字式合成技術之研究[J].宇航計測技術,2004,24(3):7-11.

[5]姜田華.實現直接數字頻率合成器的三種技術方案[J].電子技術應用,2007,30(3):1-3.

[6]石偉,宋躍,李琳.基于FPGA的DDS調頻信號的研究與實現[J].微計算機信息,2005,21(5):179-180.

[7]唐東峰,王福昌.DDS+PLL系統的頻譜分析[J].通信技術,2007(2):56-57.

[8]屈新建,常義林.基于DDS+PLL頻率合成源的設計[J].現代電子技術,2005,28(3):115-117.

[9]郝新紅,崔占忠.虛擬儀器技術在無線電引信射頻干擾試驗系統中的應用[J].探測與控制學報,2004,26(4):49-51.

[10]張駿凌,張玉興.直接數字頻率合成器中的相位噪聲分析[J].電子科技大學學報,2007,28(1):24-27.

作者簡介

孫永亮 男,1970年出生,河南西平人,碩士研究生。主要研究方向為電子設計自動化及信號處理。