基于I2C總線的音頻處理芯片設計

陶霞菲

(浙江建設職業技術學院,浙江 杭州 311231)

隨著音響的普及,越來越多的智能型音頻處理芯片被使用。這種智能型芯片大都是通過總線方式來實現控制的。本文設計了一種基于I2C總線的音頻處理芯片,通過I2C來控制音量、音調、平衡度和響度。

1 芯片功能與原理

1.1 芯片功能

該芯片具有音量、音調(低音、高音)、平衡度(左、右)和響度(前、后)控制的音頻處理電路,適用高品質的汽車收、放音機和高保真的音響系統中;提供了輸入增益選擇和外部響度控制功能;所有的控制均通過可與微機連接的串行I2C總線來操作;通過外接阻容網絡和內部運放的配合,可設置各種交流幅頻特性。具有以下主要特點:

(1)含有輸入多路選擇器:3路立體聲信號輸入;輸入增益可設置為與各種信源進行最值匹配。

(2)四聲道衰減器:4個聲道可獨立控制,對平衡度和響度進行每級1.25 dB的衰減和提升,獨立的靜音控制功能。

(3)所有的功能均通過串行I2C總線控制。

(4)有響度控制功能。

(5)音量控制每級 1.25 dB。

(6)高音和低音控制。

(7)輸入端與輸出端可與外部均衡器和噪聲抑制電路匹配。

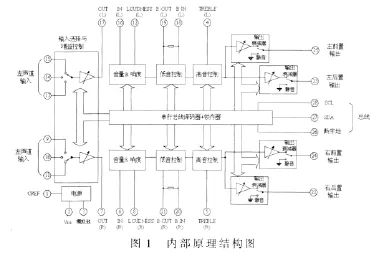

1.2 芯片內部原理結構

內部原理結構圖如圖1所示。

1.2.1 時序

(1)I2C總線接口[1-2]

微處理器與芯片之間的相互數據傳送與交換通過2線的I2C總線實現。該總線界面含有數據(SDA)和時鐘(SCL)2個端子,此2端子都必須接上拉電阻至正電源。

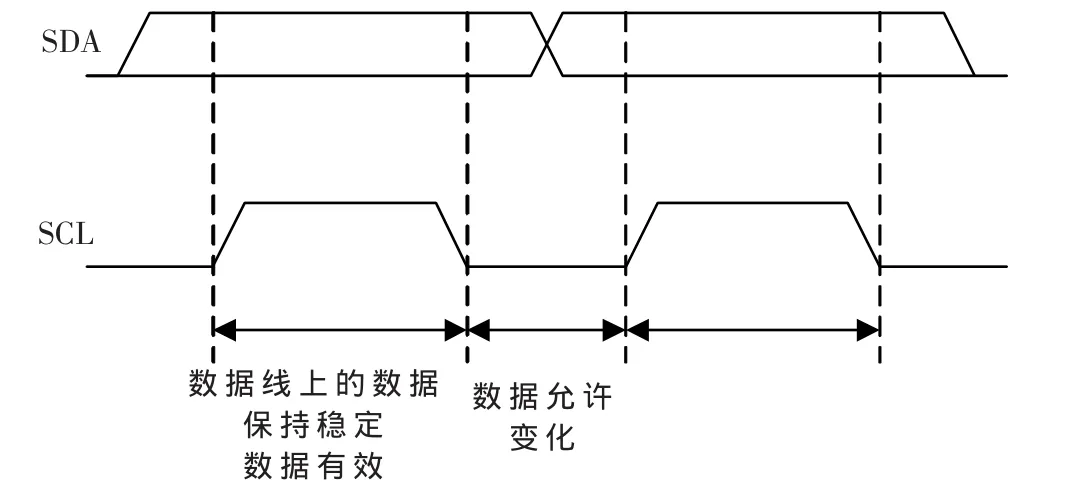

(2)數據的有效傳送

如圖2所示,SCL時鐘線為高電平時,SDA數據線上的數據必須保持穩定,只有在時鐘線為低電平時,數據才允許變化。

圖2 SDA與SCL之間關系

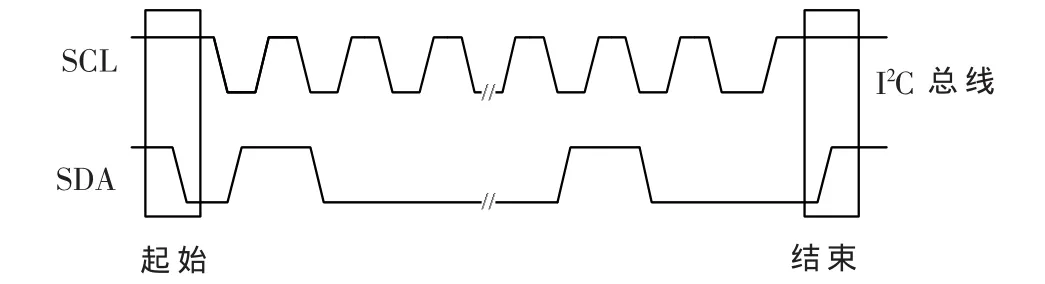

(3)起始和結束狀態

如圖3所示,起始狀態的標志是SCL為高電平時,SDA由高電平向低電平轉換;結束狀態的標志是SCL為高電平時,SDA由低電平向高電平轉換。

圖3 起始與結束時的狀態

(4)字節的構成

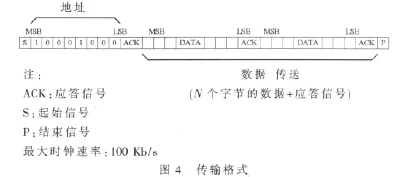

通過SDA數據線傳送的每個字節必須是8位,每1個字節之后必須緊跟1個應答位。字節的最高位最先傳送。

(5)應答信號

主控制器(單片機)在應答時鐘脈沖期間將SDA數據限制為高阻態的高電平。被控制器件在應答時,必須在應答時鐘脈沖期間將SDA數據線拉為低電平,并在此脈沖期間一直保持為低電平。

已進行地址編碼的音頻處理器在收到每1個控制字節信號時,都必須給出應答信號;否則,SDA數據線在應答時鐘脈沖期間將維持在高電平,這時,主控制器將會發出停止信號以中斷信號的傳送。

1.2.2 接口協議

(1)傳輸起始條件。

(2)地址碼。電路在每次收到1個字節的傳送信號后,必須給出1個應答信號。

(3)數據信號的順序(N個字節的數據+應答信號)

(4)傳輸結束條件。起始狀態的標志是SCL為高電平時,SDA由高電平向低電平轉換;結束狀態的標志是SCL為高電平時,SDA由低電平向高電平轉換。

(5)傳輸格式如圖4所示。

1.2.3 音量控制

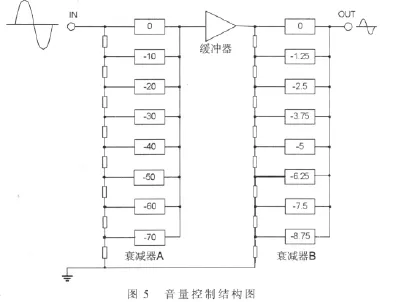

音量大小根據需要通過音量控制電路隨時調節,其線路結構如圖5所示,是由2個衰減器單元和緩沖器組成。衰減器單元包括電阻和模擬開關[3]。衰減器A在0~70 dB范圍內每級衰減10 dB。衰減器B在0~8.75 dB范圍內每級衰減1.25 dB。合計衰減量為0~78.75 dB,每級1.25 dB。

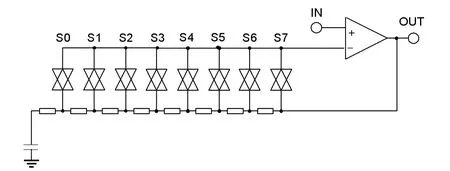

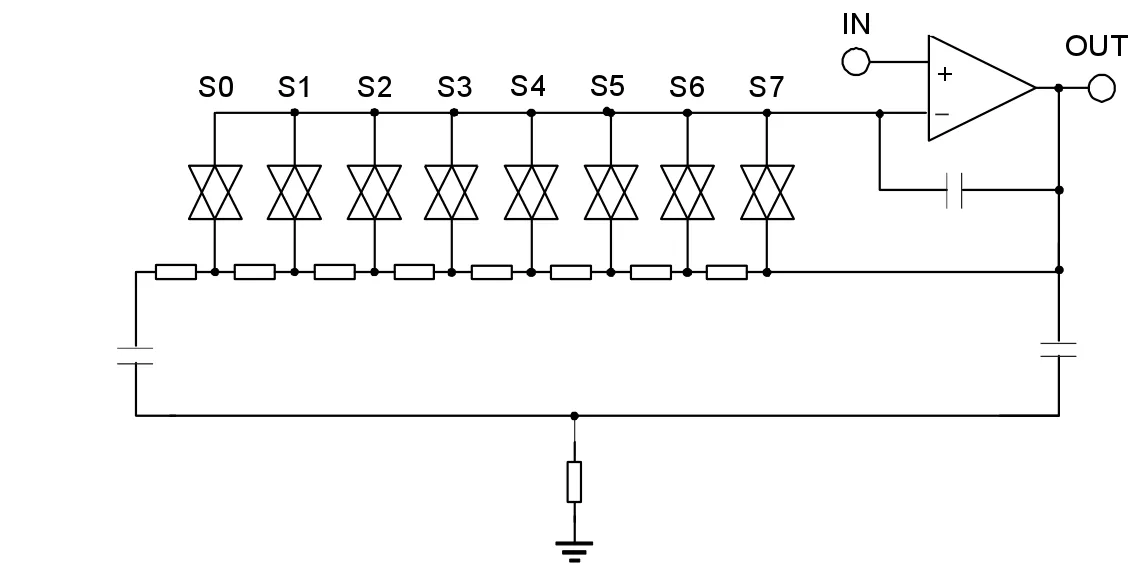

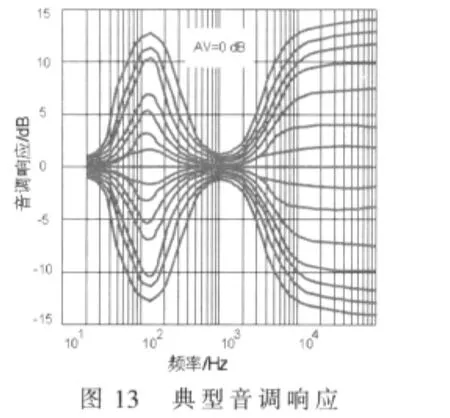

1.2.4 音調控制

音調是指具有特定且通常是穩定高音的信號(聲調高低的程度)。它主要取決于頻率和聲音強度。頻率高的聲音人耳的反應是音調高,而頻率低的聲音人耳的反應是音調低。

音調控制[4]包括高音音調控制和低音音調控制兩部分。音調控制實際上是高、低通線路,通過調節頻率特性曲線就可以達到調節音調的目的。

高、低音音調控制結構分別如圖6、圖7所示。

1.2.5 響度控制

響度控制的作用是低音量時提升高頻和低頻聲。由于人耳在低音量時對高頻聲、特別是低頻聲的聽覺靈敏度差,在小音量下,對低音和高音的聽音靈敏度遠比中音低,這樣便感覺樂曲低音不豐富,高音不明亮,相對會感到中音的輸出大,這對必須在小音量下聽音來說很不理想。要求在低音量時對高頻和低頻進行聽覺補償,即要求對低頻有較大提升,對高頻也有一定量的提升。可以引入響度補償電路,該電路能在小音量時提升低音、高音的音量,響度補償也稱等響度控制。

等響度控制如圖8所示,等響度抽頭連接在第8級處。等響度可以通過控制I2C總線設置是否打開以及等響度的程度來控制。

圖6 高音音調控制結構圖

圖7 低音音調控制結構圖

圖8 等響度控制結構圖

1.3 應用線路

總體應用線路圖如圖9所示。該芯片廣泛應用于汽車音響、CD、VCD 等有音源的處理系統中。可接3個音源設備,輸出4個通道。

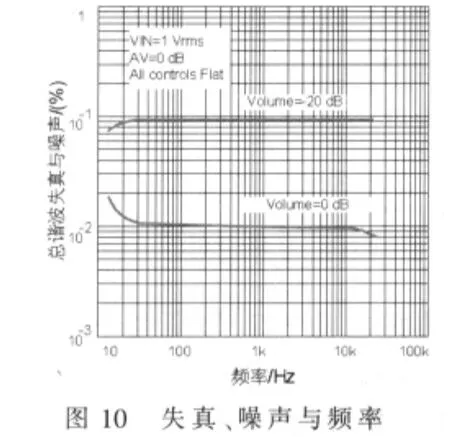

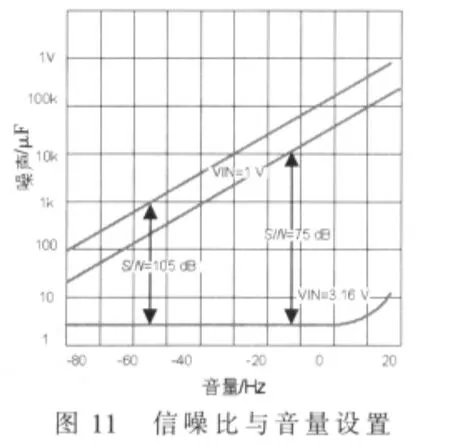

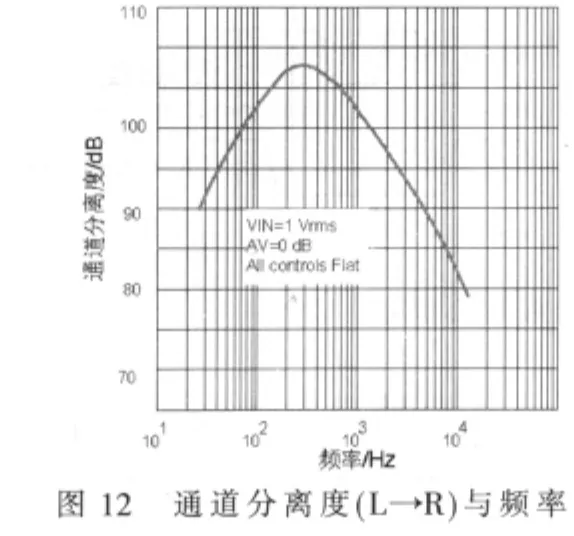

2 測試結果

該芯片采用CMOS工藝,經過流片、測試。測試結果分別如圖 10~圖 13所示。從圖中可以得出,總諧波失真小、信噪比高、噪聲低、分離度高。

本文介紹的基于I2C總線的音頻處理芯片,該芯片具有音量、音調(低音、高音)、平衡度(左、右)和響度(前、后)控制。 所有的控制均通過可與微機連接的串行I2C總線來操作。測試結果表明,采用該芯片組成的系統具有總諧波失真小、信噪比高、噪聲低、通道分離度高等特點。

[1]Philips Semiconductors.The I2C-bus specification[S].Philips semiconductors standard version 2.1.January,2000.

[2]Two-wire bus-system comprising a clock wire anda data wireforinter-connecting anumberofstations[P].US Patent Number:4689740.

[3]ALLEN P E,HOLBERG D R.CMOS analog circuit design[M].Oxford University Press, Inc., 2002.

[4]RAZAVI B.Design of analog CMOS integrated circuits[M].The MeGraw-Hill Compannies,Inc.2001.