帶有外同步輸入的圖像處理和實時顯示系統

王慧中,吳永欣,茹運蕊,褚成琴,栗武華

(中國電子科技集團公司第27研究所,河南 鄭州 450047)

1 引言

近年來,隨著多媒體技術的迅速發展和普及,數字圖像處理技術的應用越來越廣泛,在航空航天遙感、生物醫學、軍事和公共安全、工業生產和管理、多媒體應用等各個領域都得到了廣泛的應用[1]。

筆者介紹的圖像處理和實時顯示系統以TI公司C6000系列的高速DSP和Xilinx公司的Spartan 2E系列的現場可編程門陣列(FPGA)為核心構建而成[2]。其中,DSP主要用來完成解壓縮、數字圖像疊加、視頻合成等復雜的數字圖像處理工作,而FPGA主要用來完成視頻時序控制和外圍設備的硬件邏輯控制等工作。文中重點內容為該系統的軟硬件設計以及關鍵環節的解決方案。

2 系統原理及工作過程

由于數字圖像的信息量大,而且該系統的設計對實時性要求較高,因此系統設計采用高速DSP作為數字圖像處理的核心單元。同時,為了實現外部時鐘信號對視頻輸出的控制,該系統的設計選擇采用內嵌大容量RAM的FPGA來實現視頻時序的產生及控制。整個系統設計采用DSP+FPGA結構來實現。系統的原理框圖如圖1所示。

圖1 系統原理框圖

該系統的工作過程如下:DSP通過EMIF接口從Flash中讀取欲處理的圖像數據,以EDMA方式寫入SDRAM,DSP對SDRAM中的原始圖像數據進行解壓、濾波、復合等數字圖像處理,并將處理后的數據轉換為符合CCIR-6564∶2∶2 格式的 8 bit數字視頻流,處理后的數據仍放到SDRAM中。DSP在響應FPGA視頻時序產生模塊生成的行中斷信號后,由EDMA控制器以PDT傳輸的方式寫入FPGA內建的顯示行FIFO,在顯示同步時序的控制下,從顯示行FIFO輸出到視頻編碼器中,生成復合視頻,送顯示。

3 系統軟硬件設計

3.1 硬件設計

本系統主處理器采用了TMS320DM642,它是TI公司推出的專用于數字媒體應用的高性能64位定點DSP,工作頻率最高為720 MHz,處理性能可達5760 MI/s(兆指令每秒)[3]。TMS320DM642片內集成了大容量的存儲器,片內采用二級存儲器結構。此外,還提供豐富的外圍設備接口,包括外部存儲器接口(EMIF)、GPIO接口、I2C總線控制器、中斷控制器等[4]。

由于本系統的視頻輸出受外部時鐘的控制,因此,未采用TMS320DM642的VP口,而是由可編程邏輯器件FPGA生成視頻顯示的同步時序信號。本系統的硬件設計框圖如圖2所示。

圖2 系統硬件設計框圖

1)數字圖像存儲單元

TMS320DM642的外部存儲器接口(EMIF)支持各種外部器件的無縫接口[5],包括流水線式同步猝發SRAM(SBSRAM),同步 DRAM(SDRAM),包括 SRAM,ROM 和FIFO等在內的異步器件,以及外部共享存儲器等[6]。

本系統設計中,在CE1子空間外擴了8M×8 bit的非易失性存儲器(Flash),用來存儲DSP的配置程序和原始數據,由于TMS320DM642的外部地址總線只有20根,所以CE1子空間的最大尋址范圍為1M×8 bit,為了尋址到Flash的所有地址空間,系統設計中采用了分頁技術來實現對Flash的訪問。在CE2子空間外擴了SDRAM組成大容量高速幀存儲器和行緩沖,系統對SDRAM中2塊不同幀存儲區域輪流進行讀寫操作,大大提高了通信速度和數據吞吐量[7]。系統對幀存1和幀存2的輪流讀寫是通過乒乓傳輸結構來實現的,乒乓傳輸結構可有效保證數據傳輸的連續性。

2)FPGA邏輯控制單元

本系統中視頻時序控制信號的產生是由FPGA實現的,FPGA內部邏輯設計采用模塊化設計[8],以原理圖或VHDL語言生產各功能模塊:主要包括水平像素計算模塊、垂直行計數模塊、同步信號發生模塊、FIFO讀控制和復位信號產生模塊以及DSP中斷信號產生模塊。采用ISE軟件進行編譯仿真,各底層模塊均采用計數器實現,能夠精確產生各種信號。除此之外,可與外部時鐘保持良好的一致性,在每一場的起始重新與外部系統時鐘同步一次。

FPGA內部形成的的延遲鎖相環用來調整視頻同步信號時序和視頻編碼芯片的像素時鐘之間的相位差。此外,由于視頻編碼模塊和幀存儲器之間的時鐘頻率不同,設計中采用FPGA中內嵌的BlockRam構造了異步FI?FO,用來做時鐘域之間的隔離,協調數據傳輸速度。

3)視頻編碼單元

考慮到系統的工作環境和應用領域,視頻編碼模塊的設計采用了ADI公司的專用視頻編碼器ADV7171,可在-40℃~+85℃溫度下正常工作。ADV7171兼容全球各種視頻標準,對芯片的初始化可通過I2C總線完成。I2C總線只有串行數據線(SDATA)和串行時鐘線(SCLOCK),總線上的每個設備都有一個由軟件設定的唯一地址。I2C總線的數據讀寫格式如圖3所示。

圖3 I2C總線數據讀寫格式

DSP通過內部集成的I2C總線接口實現對視頻編碼器ADV7171內部寄存器的讀寫訪問操作,完成對視頻制式選擇、同步信號模式選擇等工作。專用視頻編碼器的使用,不僅提高了系統的可靠性,增強了系統功能,還縮短了開發周期,降低了成本。這些優越性是使用普通D/A所不具有的。

3.2 軟件設計

本系統的軟件設計采用“C語言+線性匯編”的模式在CCS2.2編譯環境下編寫,系統的軟件設計包括頂層應用程序和設備驅動程序兩部分。頂層應用程序主要完成對系統流程的控制、底層設備的管理和初始化,設備驅動程序主要用于實現對底層設備(如Flash,SDRAM和視頻編碼器等)的讀寫操作和控制。系統的軟件設計框架如圖4所示。

1)設備驅動程序的開發

圖4 系統軟件設計框圖

該系統的設備驅動程序主要包括定時器、通用目的輸入輸出(GPIO)、中斷控制器等片上外設的配置和管理,外部擴展存儲器(SDRAM,Flash和FIFO等)的讀寫操作和管理,以及視頻編碼芯片的配置和控制。片內外設的驅動程序主要通過芯片支持庫(CSL)提供的API函數來完成對片內外設寄存器的設置,從而實現對片內外設的配置和管理,外部存儲器(SDRAM,Flash以及FIFO)的讀寫操作和管理是外部存儲器接口(EMIF)寄存器、增強的直接存儲器訪問(EDMA)控制寄存器以及中斷控制寄存器的配置來完成的,而對視頻編碼芯片的管理和控制則是通過DSP片內集成的I2C模塊對視頻編碼芯片相關寄存器的配置來實現的。

2)應用程序的開發

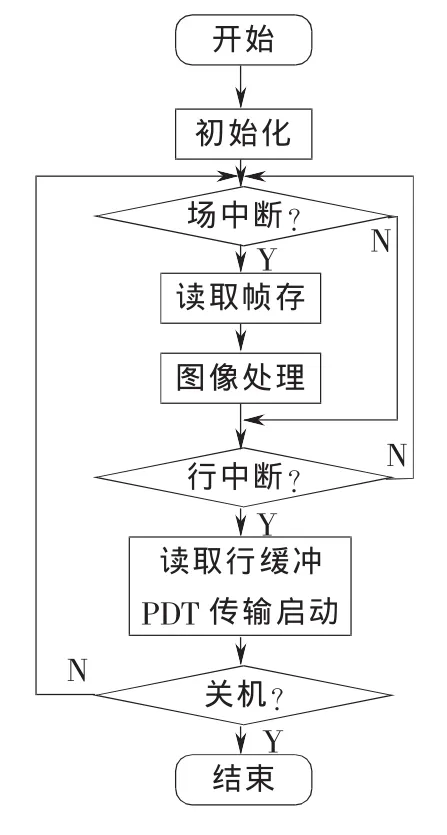

該系統的頂層應用管理程序的設計采用了模塊化結構,根據工程應用的具體要求,主要劃分為初始化模塊、圖像處理模塊、中斷管理模塊和外部存儲器模塊等幾個部分,模塊化的設計結構使得程序更加易于調試和修改,應用程序的軟件設計流程如圖5所示。

圖5 應用程序設計流程圖

4 小結

本文給出了基于DSP和FPGA結構的帶有外同步輸入的圖像處理和實時顯示系統的設計方案,已成功地應用于工程實踐中。由于本設計中采用FPGA來產生和控制視頻時序信號,可在不改變硬件電路的情況下,只通過重寫FPGA來滿足不同視頻制式的時序要求,大大提高了電路的適應性和靈活性。此外,由于在本設計中,每場起始時均與外部50 Hz時鐘重新同步一次,因此,本設計可適用于對同步要求較高的場合。

[1]何斌,馬天予.Visual C++數字圖像處理[M].2版.北京:人民郵電出版社,2002.

[2]盛磊,徐科軍.基于DSP和FPGA的實時視頻處理平臺的設計與實現[J].電氣測量及儀器,2006,36(3):304-309.

[3]TI.TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor[EB/OL].[2009-12-12].http∶//focus.ti.com/lit/ds/sprs200m/sprs200m.pdf.

[4]江思敏,劉暢.TMS320C6000 DSP應用開發教程[M].北京:機械工業出版設,2005.

[5]TI.TMS320C6000 DSP external memory interface(EMIF)reference guide[EB/OL].[2009-12-12].http∶//wisconsin.cern.ch/ROD/ti_documents/EMIF%20Reference%20Guide-%20spru266b.pdf.

[6]美國德州儀器公司,TMS320C6000系列DSP的CPU與外設[M].北京:清華大學出版社,2007.

[7]王建華,劉纏牢,陳大川,等.基于DSP+FDGA技術的實時視頻采集系統的設計[J].國外電子測量技術,2007,26(9):42-48.

[8]史彩娟,李文元,張培芳.基于CPLD的電視信號發生器的設計與實現[J].電子測量技術,2006,29(3):76-78.