基于FPGA分布式算法的濾波器設計

桂 婧 田森平

(華南理工大學自動化學院)

基于FPGA分布式算法的濾波器設計

桂 婧 田森平

(華南理工大學自動化學院)

研究基于分布式算法的數字濾波器設計方法,介紹了能高效實現固定常數乘法的分布式算法原理,并將分布式算法應用于FIR低通濾波器設計,實現了16階濾波器的設計和調試.采用了EP3C25F324C8來完成濾波器的設計,其中采用串行加法器將數據進行預相加,將16階降為8階,降低了資源占用率并提升了處理速度。使用Matlab編程8階固定常數系數對應256個值的查找表直接導入到FPGA的ROM中,設計方法具有兼容性,可設計更高階次的濾波器。通過功能仿真證明,方法可行高效。

FIR濾波器; FPGA;分布式算法;查找表

1 引言

在信號處理過程中,如對信號的過濾、檢測、預測等,都需要用到濾波器。模擬濾波器是以電容,電阻,預算放大器等模擬元件為基礎構成的具有選頻作用的電路。但模擬元件所固有的一些缺陷,如元件對溫度變化、老化的敏感、現代壓微米設計帶來的噪聲等,取而代之的是采用數字方式實現的濾波器[1]。隨著數字信號處理技術的不斷發展,采樣速率也不斷提高。DSP(數字信號處理)芯片和集成濾波芯片由于運算速度、階數和字長的限制已經不具備實現FIR(有限沖激響應數字濾波器)濾波器的能力[2]。而FPGA(現場可編程門陣列集成電路)在對數據進行實時處理方面具有巨大的優勢同時兼具一定的靈活性,因此非常適合用來實現數字濾波器的設計。在基于FPGA的數字濾波器的設計中,分布式算法是常用的算法之一,然而當濾波器階數高于4階時,分布式算法中的LUT(查找表)通常采用拆分為多個4輸入查找表的方法來實現[5],對于16階以下的查找表此種方法并非高效。

本文將介紹基于Altera公司的EP3C25F324C8NES系列FPGA的FIR濾波器設計,在對分布式算法理論研究的基礎上,采用串行加法器將數據進行預相加,將16階降為8階,降低了資源占用率并提升了處理速度。使用Matlab編程8階固定常數系數對應256個值的查找表直接導入到FPGA的ROM中,避免使用拆分查找表的方式,設計方法具有兼容性,可設計更高階次的濾波器,并完成了濾波器的結構設計和軟件編程和功能仿真。

2 算法描述

2.1 FIR的基本概念

數字濾波器是數字信號處理中使用最廣泛的一種方法,實現方法主要有IIR(無限沖激響應數字濾波器)和FIR(有限沖激響應數字濾波器)兩種[3],其中IIR濾波器需要執行無限數量卷積,能得到較好的幅度特性,其相位特性是非線性的;而FIR濾波器值由有限個采樣值組成,具有嚴格的線性相位特性。由于在數據通訊、語音信號處理、圖像處理等傳輸過程中不能有明顯的相位失真,而FIR濾波器在滿足一定對稱條件下可以實現IIR濾波器難以實現的線性相位,因而得到廣泛應用。

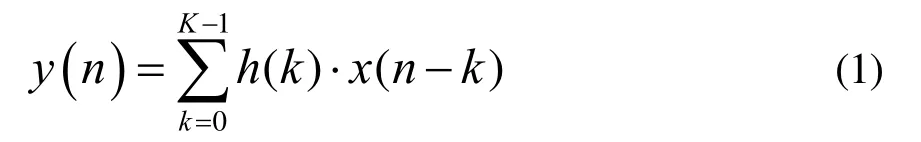

FIR濾波器的數學表達式可用K階內積來表示:

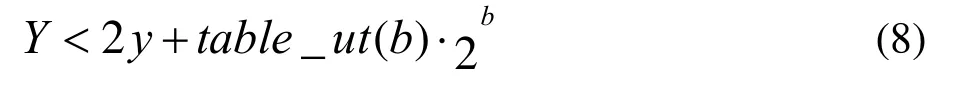

其中K 表示FIR濾波器的抽頭數;h( k)表示第k級抽頭系數(單位脈沖響應);x( n-k)表示延時k個抽頭的輸入信號。

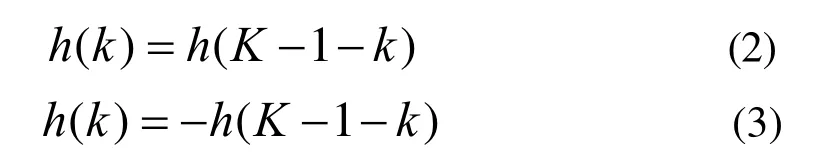

濾波器的單位脈沖響應均為實數,在幅度上只要滿足下列兩個條件之一,就能構成線性相位濾波器。第一類線性相位的幅度條件為偶對稱如(2)式,第二類線性相位的幅度條件為奇對稱如(3)式[4]。

FIR濾波器最基本的結構是直接型,由一個”抽頭延遲線”的加法器和乘法器的集合構成,每個乘法器的操作數就是一個FIR系數。對每次采樣y( n)都要進行K 次連續的乘法和(K-1)次加法操作,能夠提供這種算法性能的高性能硬件平臺對大多數信號處理設計者來說都有很大的吸引力。

2.2 分布式算法

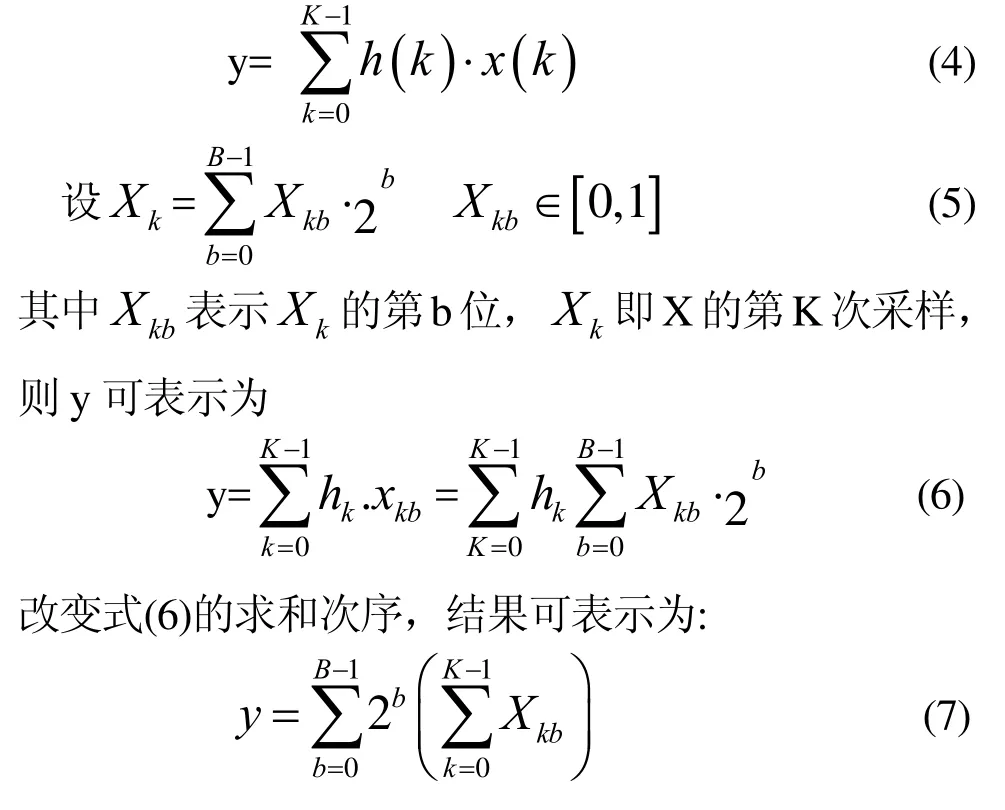

分布式算法是一項重要的FPGA技術,被廣泛運用于計算機的乘法運算中。該算法將乘法運算轉換成加法以及移位運算,能夠高速完成大量的乘法運算,極大地提高了芯片的使用效率。考慮一個內積運算[5]:

圖1 分布式算法原理圖

可以看出,分布式算法是一種以實現乘加運算為目的的運算方法,與傳統的乘累加運算不同在于執行部分積運算的先后順序不同,這個過程可用圖1的結構來實現。該算法可以利用一個查找表(LUT)實現映射,即用一個2k字寬(即2k行),預先編好程序的LUT接受一個K位輸入向量Xb=[X0b,…,X(k-1)b]的映射,經查找表的查找后直接輸出部分積算法中的乘以位權2b可以通過圖中的寄存器和累加器完成。這個過程可以用遞歸表達式表示成式(8),在執行了B次查找和B次累加后輸出結果。

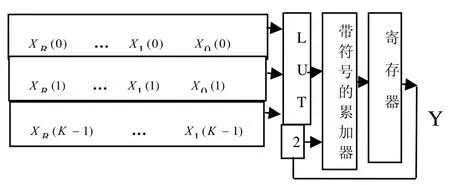

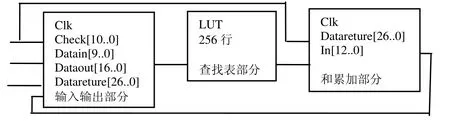

3 分布式算法在FPGA上的實現

在FPGA上實現分布式算法,可將程序劃出為輸入輸出、查找表、和累加3個部分,如圖2所示。

圖2 系統原理圖

3.1 濾波器系數確定

濾波器系數的確定是利用MATLA B中的Simulink組件中信號處理模塊的濾波器設計工具箱FDATOOL來計算。選定所需的各項參數后便可生成所需的系數。由于得到的系數均為介于[-1,1]區間的浮點數,而FPGA上只能進行定點數乘法,故將其量化為整數。

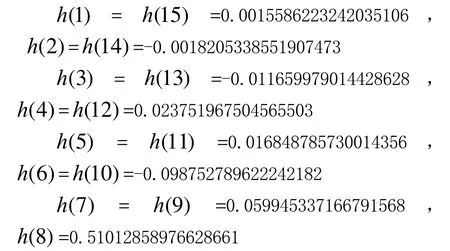

以設計一個16階的低通濾波器為例,各項技術指標為:16階低通濾波器、采樣頻率10M、截止頻率3M、最小阻帶衰減50DB、采用窗函數法、kaiser窗、beta=5、Scale Passband。

利用MATLAB中simulink的濾波器設計工具箱,可得濾波器的系數為:

將其同乘以1024便得到運算所需的系數。

3.2 輸入輸出部分

這部分的功能是對輸入的模擬信號進行采集、處理,為后續數據處理做好準備,同時它還負責接收經過運算處理后的數據,并通過D/A轉換芯片將其恢復為模擬信號。信號從這里流入,也從這里流出。除此之外它還負責產生整個系統所需的時序信號。

通過對晶振信號上升沿的計數,實現對采樣速率的控制。按照所設計濾波器的階數,建立相應于階數的數據緩沖區。若所設計的為16階濾波器,將采樣得到的10位串行數據依次存入緩沖區,存滿后則按照先進先出的流水線原則繼續存入數據,緩沖區中始終有不斷更新的16個數據。得到數據后,再依次將16個10位數據的每一位取出,組成16個10位的數據。如前所述,然后依次將每個10位的數據傳給查找表部分,同時輸出同步信號。

3.3 查找表部分(7)中可以看出,由于相加的和還要乘以不同的系數(2b),所以和累加部分與輸入輸出部分之間還有一條同步信號,用于確定二次冪加權的冪次。

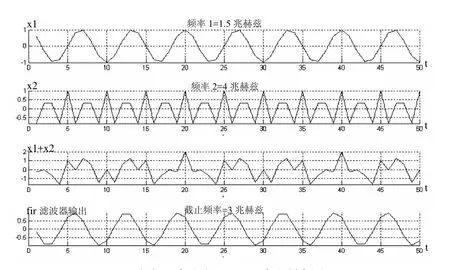

由于對系數進行了量化,即擴大了若干倍,如果直接將濾波的結果傳回輸入輸出部分進行D/A轉換,某些數據可能會超出范圍,從而使信號產生失真。為此須對得到的結果進行移位縮小,使系統的輸出波形避免失真。圖3為此濾波器的應用效果圖。

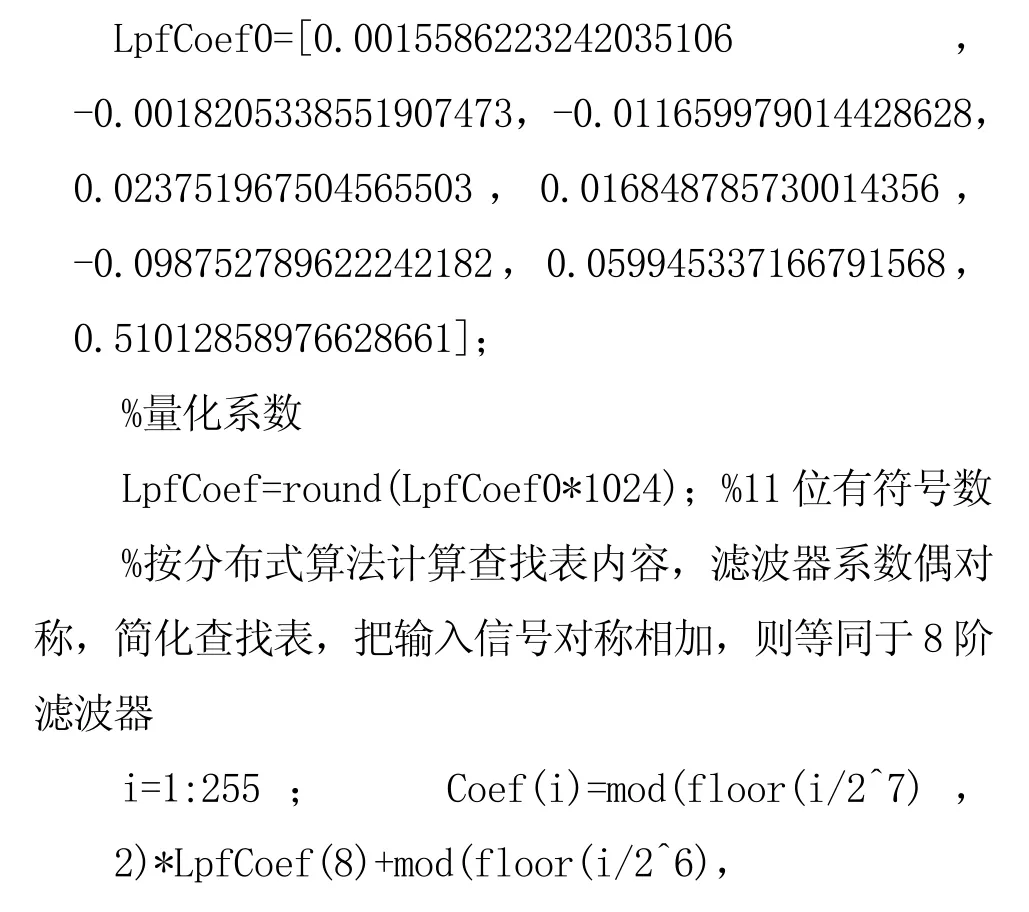

這部分的作用為接收經上一部分處理后的數據,利用查詢方式找出每一個數據對應的值,然后將值傳給下一級進行和累加。本部分用MATLAB編程然后直接導入FPGA的ROM中。部分代碼如下:

%%產生分布式算法查找表內容

%利用matlab FDAtools設計濾波器,性能指標:16階低通濾波器、采樣頻率10M、截止頻率3M、最小阻帶衰減50DB、采用窗函數法、kaiser窗、beta=5、ScalePassband、系數偶對稱、保留8個。如下:

這部分電路功能相對簡單,所需延時較短,所以沒有信號設計專門的同步信號,而是將13位數據信號作為觸發信號,即只要數據線上數據發生變化則立即完成查表操作。

3.4 和累加部分

查找表部分的輸出數據在這部分進行相加,從式

圖3 低通濾波器應用效果

4 結論

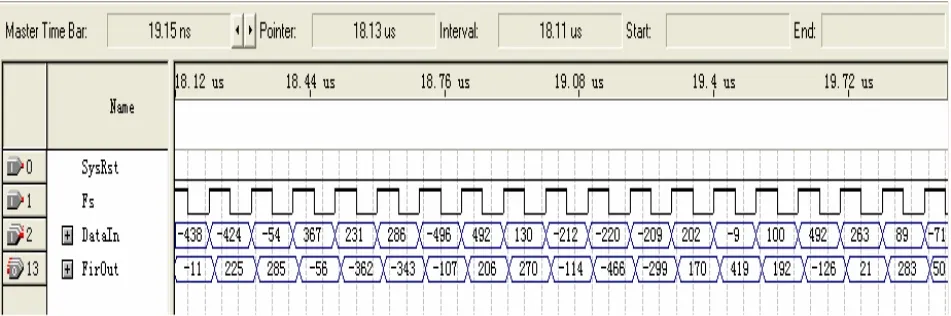

分布式算法非常適合于硬件實現,可以極大地減少硬件資源的消耗。本文討論了分布式算法的原理和基本結構,并根據實際抽頭數較多查找表規模過大的情況簡化了算法,降低的抽頭數,進一步提高了算法的效率。最后利用QII8.0進行調試,仿真結果表明實現16階的FIR濾波器只需要占用硬件2%的邏輯單元,大大提高了硬件資源的實用效率。其功能仿真圖如圖4所示。

圖4 系統功能仿真時序圖

驗證FPGA仿真結果:

FPGA仿真輸出文件FirTop.vht中位置18.1us處驗證datain=[-424,-54,367,231,286,-496,492,130,-212,-220,-209,202,-9,100,492,263];結果50

[1] 魏靈,楊日杰,崔旭濤. 基于分布式算法的數字濾波器設計[J]. 儀器儀表學報, 2008,29(10):2100~2104

[2] 趙嵐,畢衛紅,劉豐.基于FPGA的分布式算法FIR濾波器設計[J]. 電子測量技術, 2007,30(7):101~104

[3] 胡廣書. 數字信號處理教程[M]. 北京: 清華大學出版社,2001:25~35

[4] HU G SH. Digital signal processing-theory, algorithm and realizes[M].Beijing : Tsinghua University Press, 1998:55~58

[5] 王學梅, 吳敏. 基于FPGA的分布式算法FIR濾波器的設計實現[J]. 世界電子元器件, 2004,10:65~67

Design of Digital FIR Lowpass Filter Using Distributed Algorithm Based on FPGA

Gui Jing Tian Senping

(The College of Automatic Science and Engineering, South China University of Technology)

The design method of FIR filter based on distributed arithmetic is researched in this paper. The algorithm can realize changeless constant multiplication and is applied in the design of FIR filter and a 16 order FIR filter. The EP3C25F324C8 is used. The speed of the process is improved effectively. The results shows that this method to be capable and high effective.

FIR Filter;FPGA;Distributed Arithmetic;LUT

桂婧, 女,1982 年1月出生, 碩士研究生,主要研究方向為系統工程和數字信號處理。