流水線電路的容錯設計*

吳珍妮 ,梁華國 ,黃正峰 ,陳秀美 ,曹 源

(1.合肥工業大學 計算機與信息學院,安徽 合肥 230009;2.合肥工業大學 電子科學與應用物理學院,安徽 合肥 230009)

軟錯誤 (Soft Error)也稱為單事件翻轉SEU(Single Event Upset),是由宇宙輻射中的中子和封裝材料中的α粒子轟擊電路所造成的瞬態錯誤[1],它是一種間歇性的不可預測的硬件工作錯誤。過去曾經認為高能粒子在穿越大氣層時能量迅速減弱,不會引起地面上的集成電路發生功能性錯誤。但是隨著集成電路特征尺寸的急劇減小,單芯片中的節點迅速增加,并且由于供電電壓的降低,節點的電量也隨之降低,較低能量的粒子也有可能影響集成電路的正常運行[2]。

當粒子轟擊集成電路時,粒子與硅晶格在庫倫力的作用下會產生沉積電荷。當電荷累計到一定量時,受影響節點會翻轉到一個錯誤的邏輯值。對于存儲器或觸發器等時序邏輯電路,錯誤的值將一直被保持到下一個值寫入,這種現象稱為SEU。對于組合邏輯電路,錯誤值只會形成一個寬 0.35 ns~1.3 ns的毛刺[3],稱為單事件瞬態SET(Single Event Transient)。SEU的發生頻率很高,商用MIPS處理器在500 km地球近地軌道上大約每分鐘發生1次 SEU[2]。據參考文獻[1]統計的數據,存儲器和時序邏輯電路SEU的發生頻率約是組合邏輯電路SET的9倍。

針對軟錯誤,國際上提出了許多單元級的容錯設計。在組合邏輯電路上,針對單個門提出加固方法,主要有輸出鉗位電路法[4]和復制門法[5]。而在時序邏輯電路上,以設計具有容錯性能結構的新型時序單元(latch,flip-flop)來代替傳統結構的時序單元,從而達到容軟錯誤的目的。已提出的結構有 TMR-latch[6]、SDT-latch[7]、DF-DICE-latch[8],以及本研究小組所提出的RHBD-latch[9]等。

本文通過對時序單元的容錯性能進行分析,考慮流水線電路時序單元數目多、對SEU敏感度大的特點,利用RHBD-latch結構代替傳統時序單元,設計出具有優良容錯性能的流水線電路。同時綜合考慮提高可靠性所帶來的附加開銷,提出了基于開銷限制前提的容錯流水線電路設計解決思路。該方案能使傳統電路以較少的附加開銷達到容錯性能的顯著提升。

1 容錯時序單元

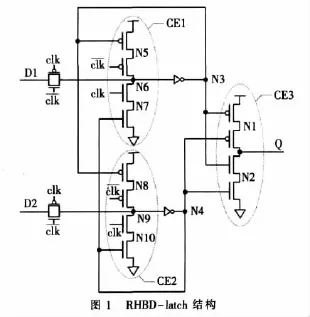

1.1 RHBD-latch

本研究小組在參考文獻[9]中提出的RHBD-latch具有良好的容錯性能,它采用了帶有內部反饋鏈的雙向互鎖結構,從而消除了鎖存器內部的脆弱點。RHBD-latch的結構如圖1所示,輸入D1或D2可以加一級延時單元,這樣RHBD-latch就能夠同時消除SEU和SET對電路的影響。RHBD-latch結構擁有3個獨立的C單元CE(C-Element):CE1、CE2、CE3。 CE1 和 CE2 形成了一個雙向互鎖的保持結構,這樣既可以在鎖存器非透明的時候保持正確的值,又可以消除粒子轟擊電路內部節點帶來的影響。無論鎖存器是否處于非透明狀態,CE3都可以阻止SEU造成的輸出錯誤。

1.2 單元容錯性能分析

為了評估時序單元對SEU的容錯性能,本文引入了參數STF(SEU-Tolerance Function)。STF與時序單元內部節點數Ninternal-node和脆弱點數Nvulnerable-node有關。脆弱點(vulnerable node)是指內部節點中存在某些節點,當這些節點被粒子轟擊后會直接造成單元輸出錯誤。

Setvulnerable-node、Setinternal-node分別表示單元脆弱點和內部節點的集合。

電路在180 nm工藝下,由宇宙輻射中的中子和封裝材料中的α粒子轟擊電路所造成的沉積電荷量最大可達300 fC,電荷量的上限會隨著工藝水平的提高而降低。例如在130 nm、100 nm、70 nm工藝水平下,沉積電荷量的上限分別是150 fC、80 fC、40 fC[10]。

對于傳統的鎖存器結構:Setvulnerable-node=Setinternal-node,即鎖存器中的任意節點受到粒子轟擊并隨之產生一定量的沉積電荷后(這里采用180 nm工藝下的沉積電荷上限Qmax=300 fC),都會造成輸出錯誤。而對于RHBD-latch結構,通過SPICE工具進行仿真后的實驗證明,RHBD-latch結構不含脆弱點,Setvulnerable-node=?。 定義:

式中VF(Vulnerability Factor)為時序單元的脆弱因子,

STF∈[0,1],STF的值越高,單元的容錯性能就越強。對于傳統結構的 latch,STF=0,而對于 RHBD-latch結構,STF=1。

2 流水線電路的容錯設計

2.1 方案

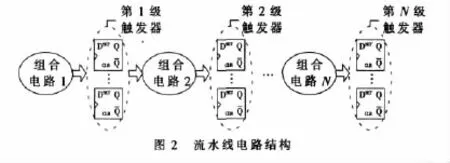

流水線電路將功能的執行操作分成多步并在若干個高速時鐘內完成,如圖2所示。

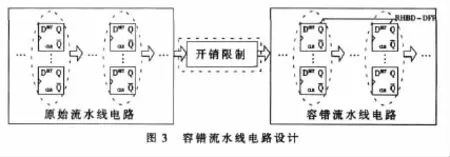

時序單元對整個流水線電路工作起到至關重要的作用。流水線電路中存在大量的觸發器,若其中某個觸發器發生SEU,則很可能造成下級多個觸發器出錯,并最終引起整個電路功能錯誤。本文針對電路的SEU,使用主從RHBD結構的D觸發器(RHBD-DFF)代替傳統觸發器,如圖3所示。若將原始電路中的傳統觸發器全部替換為RHBD-DFF,根據RHBD結構的容錯性能,相對于使用傳統鎖存器或觸發器,整體電路的容錯性能將能得到最大提升。但綜合考慮電路工作的實際條件,由于RHBD結構相對于傳統鎖存器或觸發器,在面積上有一定的附加開銷,而對于大多數片上系統SoC(System on Chip)設計,由于芯片內部硬件資源有限,因此,對所設計電路存在一定開銷限制。在此前提下,可以挑選出對整體電路的運行功能以及可靠性影響最大,即最關鍵的觸發器集合進行替換,從而達到以最小的代價獲得最大容錯性能的目的。

2.2 容錯性能提升評估

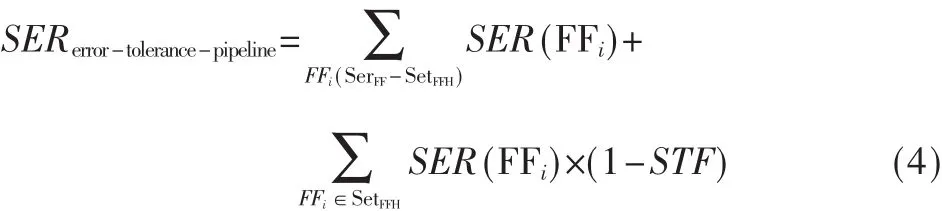

評價電路受軟錯誤影響程度的指標是軟錯誤率SER(Soft Error Rate),即軟錯誤的發生頻率。容錯流水線電路SER:

式中,SER(FFi)是單個觸發器FFi受粒子轟擊并出錯的頻率,SetFF為原始流水線電路的全部時序單元集合(本文統一時序單元為主從鎖存器結構的 D觸發器),SetFFH表示需要用RHBD-DFF進行替換的觸發器集合。本文提出的容錯流水電路設計是在期望可靠性最大的情況下(SetFF=SetFFH),即需要將電路中所有傳統觸發器替換成RHBD-DFF,這是由傳統觸發器或鎖存器對SEU的敏感性以及RHBD結構優良的容錯性能所決定的。但對于許多SoC設計,由于芯片內資源有限,電路存在開銷限制條件,為了在有限的開銷限制條件下達到電路容錯性能的最佳提升,則需要挑選出最關鍵的觸發器集合SetFFH,SetFFH?SetFF,僅對集合SetFFH中的觸發器進行替換。

為了評估電路容錯性能的改善,本文引入容錯性能改善系數 STIF(SEU-Tolerance Improved Factor):

式中,SERpipeline為原始流水線電路的SER。

3 實驗結果

本文以4級流水布斯乘法器為實驗電路,內含66個D觸發器,采用加速的方法[11]對電路進行故障注入。考慮輸入是隨機分布的情況,趨于極限則概率服從均勻分布,即將所有輸入的向量組合都考慮到,并給每種組合賦予相同的出現概率。在每種輸入情況下,對被測電路每個觸發器分別注入故障,通過復位D觸發器來模擬SEU的出現。

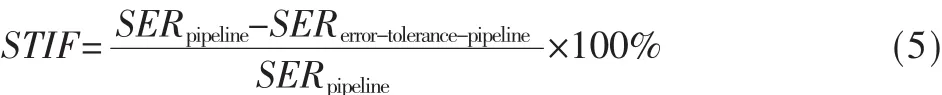

通過仿真工具NC-Verilog及綜合工具Design Compiler對電路進行了仿真和綜合,根據式(5)及本文提出的容錯設計方案,在對實驗電路進行容錯設計改進后,STIF能達到100%,即容錯性能的最大提升,相對于原始電路,帶來的額外面積開銷為51.3%,如圖4所示。圖4中同時列出使用其他容錯SEU結構的鎖存器對電路進行替換時,所帶來的額外面積開銷情況。需要注意的是,在使用 SDT-latch和 DF-DICE-latch進行替換時,雖然額外面積開銷相對于本方案較低,但由于其結構本身存在脆弱點(即STF<1)的情況下,即使將電路的傳統時序單元全部替換,也無法使STIF達到100%的提升,電路的容錯性能無法完善。RHBD-latch和TMR-latch的結構內部不存在脆弱點,單元容錯性能相同,即STF=1,但在達到相同的STIF情況下,采用TMR-latch設計電路的額外開銷較大。

圖4 各種鎖存器設計電路的額外面積開銷

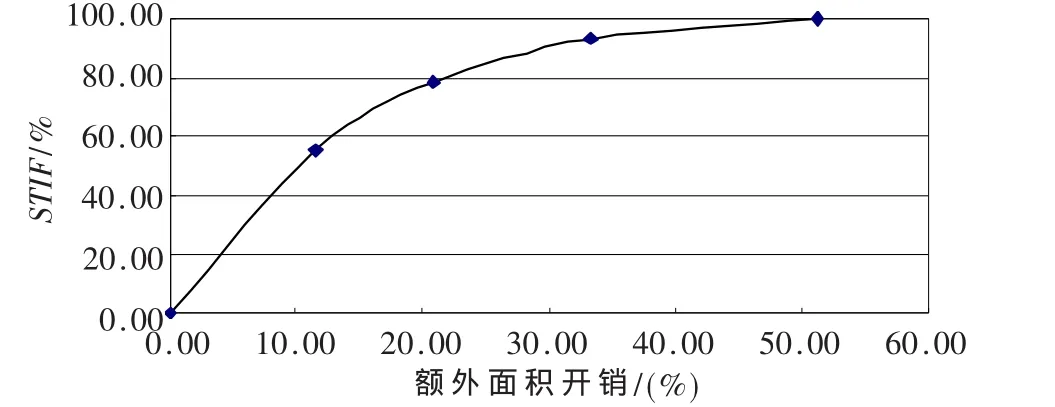

在考慮面積開銷限制條件的前提下,確定不同大小的SetFFH對整體電路容錯能力提升STIF帶來的影響,如圖5所示。橫坐標表示對不同大小SetFFH進行替換后所造成的額外面積開銷。若對電路時序單元全部采用本方案(RHBD-latch結構)進行替換,STIF達到100%時,電路的額外面積開銷為51.3%。若有存在面積開銷限制,例如要求額外開銷在10%左右,可選取對應的SetFFH、根據實驗結果,替換后,整體電路面積僅比原始電路多了11.5%,而 STIF提升到 55.4%。

圖5 電路容錯效果提升

本文針對環境輻射引起地面電路出現軟錯誤,并對電路工作構成嚴重影響這一事實,對當今數字電路設計應用廣泛的流水線電路,提出了容錯設計方案。在對時序單元進行容錯性能分析的基礎上,采用容錯性能優良的RHBD-latch結構對流水線電路中存在的大量傳統時序單元進行替換,使流水線電路具備容錯特性。本文使用RHBD-latch結構來代替原始電路傳統觸發器中的主從鎖存器,其結構的優良性能夠極大地提高流水線電路的可靠性。若使用其他有脆弱點的結構(如DF-DICEDFF或SDT-DFF),將無法使電路的容錯性能得到最優提升。相比于用TMR-DFF替換,本方案在達到相同STIF的前提下,面積開銷可節省30%。

[1]MITRA S,SEIFERT N,ZHANG M,et al.Robust system design with built-in soft-error resilience[J].Computer,2005,38(2):43-52.

[2]陳微,龔銳,劉芳,等.FT51:一種容軟錯誤高可靠微控制器[J].計算機學報,2007,30(10):1662-1673.

[3]EATON P, BENEDETTO J, MAVIS D, et al.Single event transient pulsewidth measurements using a variable temporal latch technique[J].Nuclear Science, IEEE Transactions on,2004,51(6):3365-3368.

[4]GARG R, JAYAKUMAR N, KHATRI S P, et al.A design approach for radiation-hard digital electronics[C]//ProceedingsofDesign Automation Conference, 2006 43rd ACM/IEEE,2006:773-778.

[5]NIEUWLAND A K, JASAREVIC S, JERIN G.Combinational logic soft error analysis and protection[C]//Proceedings of On-Line Testing Symposium,2006.IOLTS 2006.12th IEEE International,2006:6.

[6]FAZELI M, PATOOGHY A, MIREMADI S G, etal.Feedback redundancy:a power efficient SEU-tolerant latch design for deep sub-micron technologies[C]//Proceedings of Dependable Systems and Networks, 2007.DSN’07.37th Annual IEEE/IFIP International Conference on,2007:276-285.

[7]ZHAO Chong, ZHAO Yi, DEY S.Intelligent robustness insertion for optimal transient error tolerance improvement in VLSI circuits[J].Very Large Scale Integration(VLSI)Systems, IEEE Transactions on, 2008, 16(6):714-724.

[8]NASEER R,DRAPER J.DF-DICE:a scalable solution for soft error tolerant circuit design[C]//Proceedings of Circuits and Systems,2006.ISCAS 2006.Proceedings.2006 IEEE International Symposium on,2006:4.

[9]HUANG Zheng Feng,LIANG Hua Guo.A new radiation hardened by design latch for ultra-deep-sub-micron technologies[C]//Proceedings of On-Line Testing Symposium,2008.IOLTS’08.14th IEEE International, 2008:175-176.

[10]ZHOU Qu Ming,MOHANRAM K.Gate sizing to radiation harden combinational logic[J].Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on,2006,25(1):155-166.

[11]唐志敏,黃海林,許彤.龍芯1號處理器的故障注入方法與軟錯誤敏感性分析 [J].計算機研究與發展,2006,43(10):1820-1827.