多功能數(shù)據(jù)采集處理系統(tǒng)實現(xiàn)

趙 磊

引言

數(shù)據(jù)采集與處理系統(tǒng)的設(shè)計是現(xiàn)代信號處理系統(tǒng)的基礎(chǔ),被廣泛應(yīng)用于雷達、通信、圖像處理等領(lǐng)域。近年來,隨著信息科學的高速發(fā)展,人們面臨的信號處理任務(wù)越來越繁重,對實時信號數(shù)據(jù)采集處理系統(tǒng)的要求也越來越高。所用系統(tǒng)要求具有處理大量高速數(shù)據(jù)的能力,這就要求系統(tǒng)硬件達到很高的運算速度,并且軟件處理程序也盡可能優(yōu)化,以保證系統(tǒng)的實時性。同時,伴隨著電子產(chǎn)品應(yīng)用的多樣化,電路設(shè)計的通用性也受到了大家的重視。

器件選型

A/D采樣芯片

凌力爾特(Linear)的LTC2260是一種14 bit ADC,它具有105 Msps的采樣率,功耗僅為106m,顯著減少了用于高速數(shù)據(jù)采集的功率預(yù)算,同時集成有高性能采樣保持電路,提供CMOS兼容的輸出,輸入信號和采樣時鐘均支持差分模式。LTC2260具有以下特點:信噪比73.4dB,無雜散動態(tài)范圍85dB,單1.8V電源,滿功率帶寬800MHz,CMOS、DDR CMOS或DDR LVDS輸出,可選輸入范圍1VP-P至2VP-P。

FPGA

在FPGA的選型中,通過對算法所需資源的估算和充分考慮器件的適用性,選用Altera公司StratixⅢ系列的EP3SE260。

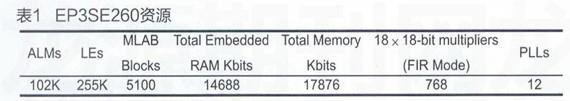

StratixⅢ擁有功能強大的DSP模塊,速度高達550MHz,具有896個18×18的乘法器,支持可變位寬,支持基本乘法器、求和、累加、級聯(lián)、取整、飽和以及桶形移位寄存器等功能。EP3SE260資源如表1所示。

DSP

本設(shè)計中DSP選用ADI公司的新一代ADSP TS201s數(shù)字信號處理器,兼有FPGA和ASlC信號處理性能和指令集處理器的高度可編程性,適用于大存儲量、高性能、高速度的信號處理領(lǐng)域。ADSP TS201S采用超級哈佛結(jié)構(gòu),靜態(tài)超標量操作適合多處理器模式運算,可直接構(gòu)成分布式并行系統(tǒng)和共享存儲式系統(tǒng),專為大的信號處理任務(wù)和通信結(jié)構(gòu)優(yōu)化。

硬件電路設(shè)計

本系統(tǒng)中設(shè)計了四路A/D,采樣后的數(shù)字信號送到FPGA進行預(yù)處理,F(xiàn)PGA同時為系統(tǒng)提供時鐘、對A/D和D/A進行控制、與DSP進行數(shù)據(jù)交換、還要為CPCI接口的實現(xiàn)提供時序邏輯和通信接口,DSP做相應(yīng)的算法處理,四路D/A可提供測試信號和自檢信號,系統(tǒng)結(jié)構(gòu)框圖如圖1所示。

A/D電路

高速A/D芯片的輸入端通常采用差分輸入,這種方式有以下優(yōu)點:差分特性對來自電源和其他電路的外部共模噪聲源具有抑制作用;能夠抵消偶次諧波;每個差分輸入所需電壓擺幅僅為單端輸入時的50%。可以降低對電源的要求。

本設(shè)計中運放采用的是ADI公司的AD8138,體積非常小巧,使得A/D芯片與信號輸入點的距離可以很近,大大減少了外界噪聲的影響,是理想的驅(qū)動芯片。單端轉(zhuǎn)差分器件選用Mini-Circuits公司的寬帶變壓器ADT1-1WT,其工作頻帶為0.4~800MHz,配合簡單的電阻網(wǎng)絡(luò)及濾波電容就可以完成設(shè)計任務(wù)了。

LTC2260的工作時鐘由FPGA提供,輸出1.8V的并行數(shù)據(jù)到FPGA進行處理,F(xiàn)PGA采用2.5V的I/O電壓。

FPGA和DSP的設(shè)計

本系統(tǒng)采用松耦合結(jié)構(gòu)設(shè)計,F(xiàn)PGA和DSP都有其各自獨立的存儲器,DSP和FPGA之間通過LINK進行互連,DSP與FPGA之間通信通過編寫FPGA仿TS201 Lib/K邏輯完成,DSP還可通過LINK與外部交換數(shù)據(jù),系統(tǒng)結(jié)構(gòu)框圖如圖2所示。這種連接方式的優(yōu)點在于:

(1)DSP和EIFPGA片間數(shù)據(jù)交換數(shù)據(jù)率更高,最高可達4GB/s;

(2)DSP和FGPA可以同時訪問各自的外部存儲器,系統(tǒng)總的存儲帶寬較大;

(3)DSP和FPGA訪問外部存儲器的同時可以通過LINK鏈路進行數(shù)傳通信;

(4)系統(tǒng)硬件連線相對獨立,易實現(xiàn)。

FPGA接口設(shè)計

FPGA主要提供3個邏輯接口,分別為與DSP的LINK接口、外部存儲器sDRAM的接口以及系統(tǒng)的輸入輸出接口。與DSP的LINK接口采用IP核設(shè)計實現(xiàn),接口能夠穩(wěn)定工作在500MHz速度上,為FPGA和DDSP之間提供4GB/s的數(shù)據(jù)傳輸能力。

FPGA到SDRAM接口邏輯自行設(shè)計,與DSP外部存儲器相同采用4片K4SS11632M構(gòu)成64bit的256MB存儲空間。接口工作在80MHz時鐘頻率,數(shù)據(jù)率為640MB/s。

FPGA的輸入輸出接口連接到系統(tǒng)外,因此采用LVDS協(xié)議來保證信號的穩(wěn)定、準確傳輸,雙向備提供32bit數(shù)據(jù)寬度,采用250MHz的板間傳輸頻率,可以提供2GB/s的傳輸能力。

DSP總線接口設(shè)計

ADSP TS201外部總線支持多種不同的協(xié)議,并且可以通過編程進行配置。外部總線接口支持流水線協(xié)議,SDRAM協(xié)議和慢速設(shè)備協(xié)議。TS201可以采用流水線協(xié)議訪問存儲系統(tǒng)。另外TS201有片上的SDRAM控制器,支持與sDRAM的無縫連接。本設(shè)計中總線上的外設(shè)分別為SDRAM以及DSP加載程序的FLASH存儲器。

TS201處理器的sDRAM接口,支持1024、512、256字的頁面長度,通過對sDRCON寄存器的編程可實現(xiàn)頁面長度的選擇。同時sDRAM占用TS201的外部存儲空間地址,通過/MSSD3~0來確定SDRAM的地址空間范圍。本設(shè)計選用的sDRAM型號為K4S511632M,頁面長度為s12字,將四片SDRAM拼接成64位的總線寬度,實現(xiàn)與TS201的無縫接口的2S6MB存儲空間。

DSP進行運算除了其外部存儲器外,還需要對其自身進行程序加載的BOOT FLASH。本設(shè)計中使用AT49BV321,設(shè)計中FLAsH的cE信號需要使用DSP的BMS和MSO相與后給入,這樣才能保證可以通過DSP的外總線給FLASH進行在線編程。

系統(tǒng)應(yīng)用

本文設(shè)計的高速數(shù)據(jù)采集與處理系統(tǒng),借助上面介紹的硬件平臺,可以完成通用的數(shù)據(jù)采集與處理,其中關(guān)鍵的問題就是后續(xù)的處理系統(tǒng)設(shè)計,即后續(xù)的信號處理系統(tǒng)完成的算法與功能。針對輸入信號的不同以及高速數(shù)據(jù)采集與處理系統(tǒng)的用途,后續(xù)的信號處理算法也具有多樣性。

數(shù)字下變頻

對于接收通道送來的中頻信號,由于本系統(tǒng)采用了10SMsps的采樣率,故可以直接采樣后進行下變頻處理,如圖3所示。數(shù)字下變頻器的組成包括數(shù)字混頻器、數(shù)字控制振蕩器和低通

濾波器,全部可以在FPGA中實現(xiàn),醫(yī)為通過軟件進行運算,乘法器和低通濾波器可以做到完全一致,解決了I、Q通道幅度不平衡的問題,數(shù)字下變頻器的控制和修改也更加容易。

脈壓

在雷達回波信號處理中,通常利用線性調(diào)頻信號脈沖壓縮技術(shù)來獲得高的距離分辨率,它可以在保證雷達作用距離的情況下提高雷達的距離分辨率。數(shù)字脈沖壓縮就是利用數(shù)字信號處理的方法來實現(xiàn)雷達信號的脈沖壓縮,分為時域和頻域兩種實現(xiàn)方式。一般而言,對于小時寬帶寬積信號,用時域脈壓較好,可以用專用的FIR濾波器或FPGA設(shè)計實現(xiàn);但對于大時寬帶寬積信號,用頻域脈壓較好,一般采用FFT方法在頻域?qū)崿F(xiàn)。由于DSP芯片具有很強的數(shù)據(jù)處理能力,完全能夠滿足雷達脈沖壓縮信號處理實時性的需求。

動目標檢測(MTD)

MTD是根據(jù)最佳濾波器理論發(fā)展起來的一種雷達信號處理技術(shù)。MTD濾波器是一組相鄰且部分重疊的窄帶濾波器組,覆蓋整個重復(fù)頻率的范圍。由于固定雜波和運動目標回波的多譜勒頻移不相同,利用多譜勒濾波器濾去固定雜波而取出運動目標的回波,就可以大大改善在雜波背景下檢測運動目標的能力。采用加權(quán)法的每個濾波器具有較低的副瓣,可以抑制運動雜波,還有在零頻附近的深凹口抑制固定雜波,具有較好的雜波抑制性能。MTD利用DSP內(nèi)部的FFT運算實現(xiàn)相參積累,不但提高了系統(tǒng)輸出的信噪比,還增強了雷達在各種雜波以及干擾條件下的目標檢測能力。

上面舉了一些應(yīng)用方面的例子,諸如MTI、CFAR、積累、求模以及目標錄取之類的應(yīng)用,在本系統(tǒng)中也可以輕松地實現(xiàn)。

結(jié)語

本文提出了一種基于FPGA和DSP的高速數(shù)據(jù)采集處理系統(tǒng)設(shè)計方案。該設(shè)計具有一定的通用性和可擴展性,F(xiàn)PGA可完成高速數(shù)據(jù)的存儲與相應(yīng)的數(shù)據(jù)預(yù)處理,為DSP分擔部分信號處理工作,且硬件實現(xiàn)速度快于DSP的數(shù)據(jù)處理;采用浮點DSP進行后續(xù)處理,提高了數(shù)據(jù)處理精度。該高速數(shù)據(jù)采集處理系統(tǒng)可以通過修改FPGA內(nèi)部程序來實現(xiàn)其它功能擴展,并利用后續(xù)DsP的強大實時處理能力,完成更為復(fù)雜的數(shù)字信號處理,因此在工程應(yīng)用上具有較強的通用性。

Tota IPON解決方案,適應(yīng)多標準、多規(guī)范的電信市場應(yīng)用

近日在北京舉辦的中國光網(wǎng)絡(luò)研討會上,PMC-Sierra&司帶來的TotalPON產(chǎn)品是為電信領(lǐng)域提供的一種完整解決方案。TotalPON是一款單芯片產(chǎn)品,只需一顆芯片、一款軟件,就可實現(xiàn)不同的PON標準,即目前市場上存在的兩套標準GPON和EPON,以及PON的下一代標準10GEPON和XGPON。因為這些標準實際上存在很多共性,不論是標準層面還是物理層上,以及相應(yīng)的一些應(yīng)用。同時在實施層面上,單就線卡而言,GPON和EPON也有很多相似的地方,如都有相應(yīng)的處理器、交換器,不同的只是PON在光模塊這方面的差別,而這方面比較容易解決,因為都是可插拔的,這樣就誕生了TotalPON。