高精度Σ-ΔADC中的數字抽取濾波器設計

吳笑峰,劉紅俠,李迪,胡仕剛,石立春

(1. 湖南科技大學 信息與電氣工程學院,湖南 湘潭,411201;2. 西安電子科技大學 微電子學院 寬禁帶半導體材料與器件教育部重點實驗室,陜西 西安,710071)

Σ-ΔADC現已成為高精度ADC[1]設計的一種切實可行的解決方案。Σ-ΔADC由Σ-Δ調制器和抽取濾波器組成,Σ-ΔADC中調制器的基本原理是過采樣和噪聲整形。在Σ-ΔADC中,需要采用數字抽取濾波器對調制器的輸出數據進行抽取,將原來的過采樣頻率降低到奈奎斯特采樣率,并同時將模擬信號轉換成數字信號。數字抽取濾波器的主要作用是移除量化噪聲,降低采樣頻率和抗混疊。本文的主要目標是設計1個應用于18位二階Σ-ΔDC中的數字抽取濾波器。數字抽取濾波器的性能參數如下:輸入信號采樣頻率為6.144 MHz,輸出信號采樣頻率為奈奎斯特率即48 kHz,降采樣率為128,通帶頻率為21.77 kHz,阻帶增益頻率為26.23 kHz,通帶波紋系數為±0.01 dB,阻帶增益衰減120 dB。由于數字抽取濾波器對整個Σ-ΔADC的面積和功耗有非常重要的影響[2-4],在此,本文作者采用多級結構[5-7]的實現形式,并對各級濾波器的面積和功耗進行最大程度優化。

1 整體結構

多級結構可以極大地減小濾波器的階數,因此,本文采用多級結構(如圖1)來達到降采樣的目的。設計中,同時根據最終的設計目標,采用一些特殊的濾波器來進一步減小面積和功耗。

圖1 數字抽取濾波器結構Fig.1 Structure of digital decimation filter

在設計Σ-ΔADC時,由于第1級抽取系數比較大,通帶只占輸出抽樣頻率的很小部分,因此,第1級濾波器可以采用 1種特殊的濾波器即級聯梳狀(Cascade of integrators comb, CIC)濾波器[8]。它可以大大減小第1級濾波器的階數,也使得整體設計簡化很多。雖然第1級梳狀濾波器的面積很小,但梳狀濾波器在通帶內有衰減,這就需要在第2級補償帶內衰減,因此,第2級采用CIC補償濾波器。CIC補償濾波器實際上是1個FIR濾波器,其降采樣率為2。第3級采用半帶濾波器。半帶濾波器的一半系數為 0,另外一半系數對稱,這就降低了第3級濾波器階數,第3級濾波器降采樣率為 2。通過分析可以得到各級濾波器的輸入輸出采樣頻率、通帶、阻帶邊界頻率及降采樣率,如表1所示。

表1 各級濾波器的指標Table 1 Performance of filters at various levels

2 數字抽取濾波器設計

2.1 梳狀濾波器的設計

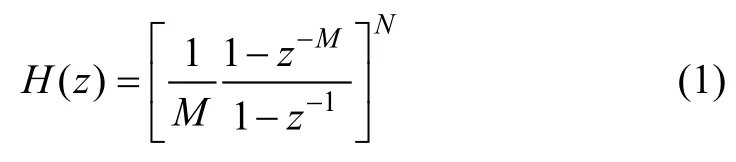

梳狀濾波器是一種在高速抽取或差值系統中非常有效的單元,主要用于無線通信和Σ-ΔADC中。采用多級級聯梳狀濾波器的結構來優化第1級濾波器的頻率響應。CIC濾波器的傳遞函數為:

其頻率響應為:

其中:M為梳狀濾波器的降采樣率;N為梳狀濾波器級聯的個數,它的頻率響應如圖2所示(以M=8為例)。一般來說,在對L階、過采樣率為M的Σ-Δ模擬調制器進行降頻時,梳狀濾波器的級聯個數要達到L+1以上,才能產生足夠的噪聲衰減[9]。由圖 2可知:梳狀濾波器在通帶內會衰減,因此,第2級濾波器用補償濾波器來實現。設定梳狀濾波器的輸出頻率為奈奎斯特采樣率的4倍,其原因是:若輸出采樣頻率太高,則會增大后級濾波器的階數,進而增大面積和功耗;若輸出采樣頻率太低,則相當于增加了梳狀濾波器自身的“瓣數”,而通帶邊界不變,很明顯,通帶頻率Fp處的衰減會增大,同時,也使得通帶邊界“靠近”阻帶邊界,增大通帶內噪聲。

圖2 級聯梳狀濾波器的頻率響應(M=8, N=4)Fig.2 Frequency response of CIC filter (M=8, N=4)

根據上面分析,確定本文的級聯梳狀濾波器的結構為:級聯個數N=5,降采樣率M=32。

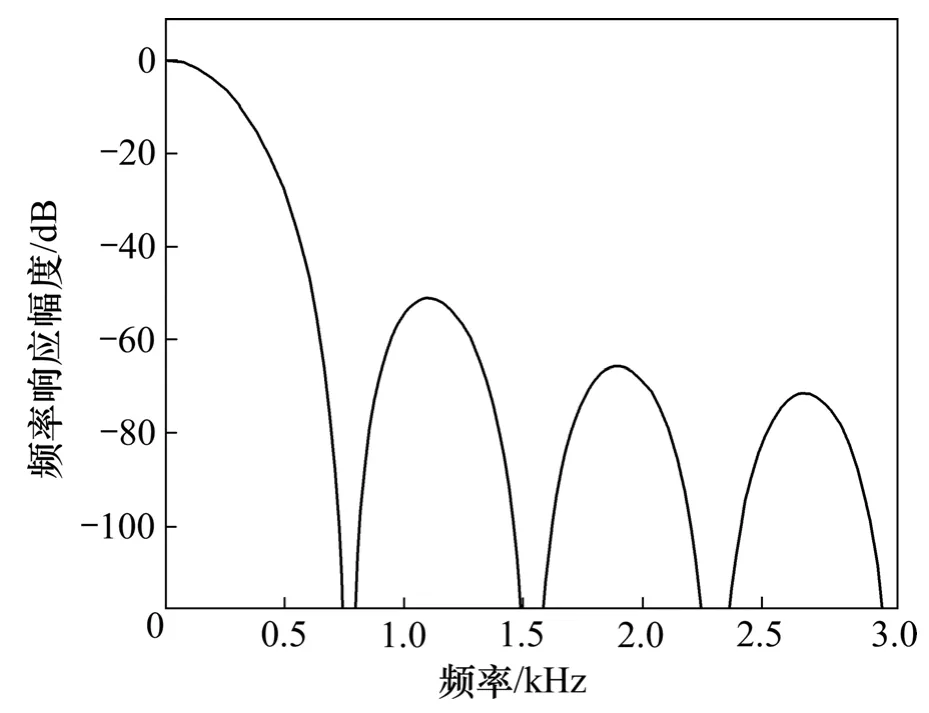

2.2 CIC補償濾波器的設計

為了補償CIC濾波器對通帶的衰減,第2級采用CIC補償濾波器。CIC補償濾波器是 1種 FIR濾波器。設計補償濾波器就要根據FIR濾波器的設計方法進行設計。本文采用切比雪夫最佳逼近法來設計CIC補償濾波器。對這種結構進行設計時,一般是參考Mcclallan的 Remez算法進行迭代,求出濾波器的系數[10]。可以調用Matlab中的Remez函數來設計,也可調用Matlab8.0 filter design toolbox中的CIC補償濾波器模型來設計[11]。CIC補償濾波器頻率響應如圖3所示。從圖3可見:補償濾波器在通帶內有凸起,能起到一定的補償作用,但需要和CIC濾波器級聯來看最終的補償結果。

圖3 CIC補償濾波器的頻率響應Fig.3 Frequency response of CIC compensation filter

根據表1中的CIC濾波器設計參數:降采樣率為32,微分延時(硬件設計時的反饋延時)為1。據補償濾波器的邊界頻率和降采樣率來設計相關的補償濾波器,可以得到相應的補償濾波器。它與CIC濾波器以及兩者級聯(Cascade filter)以后的頻率響應如圖 4所示。從圖4所示CIC濾波器和CIC補償濾波器的級聯結果來看,求得的補償濾波器可以很好地補償 CIC filter在通帶內的衰減,能達到設計的目標。

由Matlab運算得到CIC補償濾波器,它共有22階,各階系數見表2。從表2可以看出:CIC補償濾波器的系數是對稱的,在其22階的系數中,只有11個不重復的系數。在硬件實現時,這個特點可以使本級濾波器的面積減小一半。

圖4 CIC濾波器、CIC補償濾波器和Cascade濾波器的頻率響應Fig.4 Frequency response of CIC filter, CIC compensation filter and Cascade filter

表2 CIC補償濾波器的系數Table 2 Coefficient of CIC compensation filter

2.3 半帶濾波器的設計

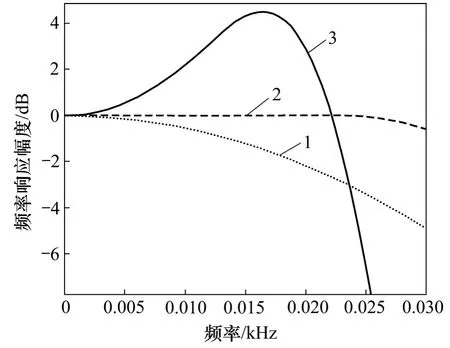

在設計最后一級濾波器時,發現只需要2倍降采樣的濾波器即可,而半帶濾波器可以滿足這種要求,它的近一半系數為 0。因此,相對于能達到同樣效果的普通FIR濾波器來說,半帶濾波器乘法單元減少一半。因此,最后一級濾波器采用半帶濾波器[12]。半帶濾波器的頻率響應為:

其半帶濾波的單位脈沖響應為:

其中:N為奇數。從式(3)可以看到:當n-(N-1)/2為偶數時,濾波器的系數h(n)為 0,而且半帶濾波器也屬于FIR濾波器。FIR濾波器的單位脈沖響應有對稱性[13],因此,半帶濾波最多只有N/4+1個不重復系數。與補償濾波器一樣,半帶濾波器也屬于FIR濾波器。考慮到半帶濾波器的特點,在用切比雪夫逼近法設計半帶濾波器時,可以簡化設計。假定需要設計1個長度為N的半帶濾波器,當(N-1)/2為奇數時(若為偶數,則h(0)=h(n)=0,相當于1個N-2的半帶濾波器),設計的通帶邊界、阻帶邊界和波紋系數分別為ωp,ωc和δp。首先用等波紋設計1個(N-1)/2的普通FIR濾波器g(n),其通帶波紋系數為2δp,通帶邊界系數為2ωp。由于2ωc>π,故可以將這個g(n)的阻帶邊界系數設為π。定義:

則有

其中:n=0, 1, …,N-1。根據G(n)的參數求出g(n),然后,根據公式(6)得到h(n)的系數,它們的頻率響應如圖5所示。

采用Matlab8.0/simulink/filter design toolbox中的Halfband濾波器模型設計更方便。最終得到的159階Halfband濾波器,系數的有效數為40個。

圖5 G(n)與H(n)的頻率響應Fig.5 Frequency response of G(n) and H(n)

3 芯片測試結果

整個芯片采用Chartered 0.35 μm CMOS工藝實現,工作電壓為5 V。

模擬調制器部分和數字降采樣濾波器部分使用隔離環進行隔離,防止數字部分的噪聲影響模擬電路部分。CIC補償濾波器和半帶濾波器的系數采用 CSD(Canonic signed digit)碼實現,以實現濾波器系數最大程度的優化。電路使用移位器和加法器實現。使用邏輯分析儀對模擬調制器輸出測試端口的信號進行數據采集,并使用 MATLAB軟件進行頻譜分析,可得調制器輸出頻譜圖如圖6所示。從圖6可見:當輸入信號為-4 dB(頻率為6 kHz)時,在帶寬24 kHz內,信噪失真比 (SNDR)為102.8 dB,有效位數為16.79位。使用相同的方法,經過降采樣濾波,所得信號頻譜如圖7所示。從圖7可見:所設計的數字降采樣濾波器通帶截止頻率為21.77 kHz,過渡帶為4.5 kHz,通帶波紋系數為±0.01 dB,阻帶增益衰減120 dB。對芯片的測試結果表明:當工作電壓5 V時,所設計的抽取濾波器部分功耗僅為49 mW,面積約為0.6 mm×1.9 mm。

圖6 調制器的測試頻譜圖Fig.6 Testing frequency spectrum of modulator

圖7 數字濾波器輸出頻譜圖Fig.7 Output frequency spectrum of digital decimation filter

4 結論

(1) 采用Chartered 0.35 μm CMOS 工藝實現了一種用于高精度Σ-ΔADC多級多采樣率結構的數字抽取濾波器。該數字抽取濾波器的帶寬為21.77 kHz,輸入采用頻率6.144 MHz,降采樣率為128。對濾波器的系統結構進行了設計,在確定采用多級結構之后,分別對各級濾波器的結構、階數以及系數進行優化設計。

(2) 在滿足濾波器的設計目標下,采用了最優的選擇。測試結果表明,數字降采樣濾波器組的設計符合預期的要求。

[1] 凌玉華. 高速高精度模/數轉換的微機動態軌道衡[J]. 中南工業大學學報: 自然科學版, 1999, 30(6): 623-625.LING Yu-hua. A microcomputerizer dynamic railway scale with high-speed and high-glass accuracy A/D conversion[J]. Journal of Central South University of Technology: Natural Science,1999, 30(6): 623-625.

[2] Hogenauer E B. An economical class of digital filters for decimation and interpolation[J]. IEEE Transactions on Acoustics Speech and Signal Processing, 1981, 29(2): 155-162.

[3] Chen L, Zhao Y F, Gao D Y, et al. A decimation filter design and implementation for oversampled sigma delta APD converters[C]//Proceedings of 2005 IEEE International Workshop on VLSI Design and Video Technology. Suzhou, 2005:55-58.

[4] Ren S, Siferd R, Blumgold R, et al. Hardware efficient FIR compensation filter for delta sigma modulator analog to digital converters[C]//48th Midwest Symposium on Circuits and Systems. Covington, Kentucky, 2005: 1514-1517.

[5] Brandt B P, Wooley B A. A low-power area efficient digital filter for decimation and interpolation[J]. IEEE Journal of Solid-state Circuits, 1994, 29(6): 679-687.

[6] Goodman J, Carey M J. Nine digital filters for decimation and interpolation[J]. IEEE Trans Acoust, Speech, Signal Processing,1997, 25(3): 121-126.

[7] Coffey M. Optimizing multistage decimation and interpolation processing[J]. IEEE Signal Process Lett, 2003, 10(4): 107-110.

[8] Aboushady H, Mehrez H. Efficient polyphase decomposition of comb filters in SD analog-to-digital converters[J]. IEEE Trans Circuits Syst Ⅱ: Analog and Digital Signal Process, 2001, 48:898-903.

[9] Candy J C. Decimation for sigma delta modulation[J]. IEEE Trans Comm, 1986, 34(1): 72-76.

[10] Crochiere R E, Rabiner L R. Interpolation and decimation of digital signals: A tutorial review[C]//Proceeding of the IEEE.Houston, 1981, 69: 300-331.

[11] Maulik P C, Chadha M S, Lee W L. A 16-bit 250-KHz delta-sigma modulator and decimation Filter[J]. IEEE Journal of Solid-state Circuits, 2000, 35: 458-467.

[12] Vaidyanathan P P, Nguyen T Q. A “TRICK” for the design of FIR half-band filters[J]. IEEE Trans Circuits and Systems, 1987,34(3): 297-301.

[13] Lu W, Hinamoto T. Design of FIR filters with discrete coefficients via polynomial programming: towards the global solution[C]//IEEE ISCAS. New Orleans, 2007: 2048-2051.