高k柵介質/金屬柵結構CMOS器件的等效氧化層厚度控制技術

陳世杰,王文武,蔡雪梅,陳大鵬,王曉磊,韓 鍇

(中國科學院微電子研究所,北京 100029)

自20世紀60年代以來,集成電路制造工藝一直遵循著摩爾定律高速發展。CMOS器件的特征尺寸始終按照一定的比例不斷的進行縮小,而其性能和功耗則不斷地得到優化。根據2007年ITRS的預測,在2009年以后,高性能CMOS器件的柵介質層EOT會縮小到1 nm以下。在這個尺寸下,傳統的SiO2柵介質暴露出柵漏電流過大,可靠性降低等嚴重問題。通過引入高k柵介質材料,增大了柵介質層的物理厚度,從而有效地降低了柵漏電流。因此,采用高k柵介質取代傳統的SiO2是以CMOS器件為核心的集成電路發展的必然選擇。在2007年,Intel公司在其45 nm CPU產品中已經采用了新一代的高k柵介質/金屬柵工藝,并在其2010年即將上市的32 nm工藝產品中用到第二代高k/金屬柵技術。這表明從45 nm技術節點開始,CMOS器件中的傳統SiO2/多晶硅柵結構將被全新的高k柵介質/金屬柵結構所取代,這是一次劃時代的革新。有鑒于此,本文將結合國內外相關的文獻報導和各半導體公司的最新研究進展,綜述在45 nm以下技術節點中,高k柵介質/金屬柵結構CMOS器件的EOT縮小動因、厚度控制技術以及存在的可能挑戰和展望。

1 高k柵介質/金屬柵結構CMOS器件EOT縮小的動因

現代半導體工業中,CMOS工藝能占據支配地位的兩個最主要原因是CMOS器件的零靜態功耗和MOSFETS能夠按比例縮小。集成電路誕生至今,其發展一直遵循著摩爾定律,器件尺寸始終按照一定的比例不斷地減小。目前,通常采用的按比例縮小方法是同時結合了恒定電場和恒定電壓的規則。更小的器件尺寸可以使得器件性能大幅提升,讓器件速度更快、功耗更小、集成度更高、制造成本更低廉以及功能更強大等。根據器件按比例縮小的原則,CMOS器件的柵介質厚度需要不斷地變小,進而提高器件開態飽和電流和柵控能力[1]。

從器件角度來說,由于溝道變得越來越短,源端和漏端的空間電荷區變得越來越靠近,為了防止源漏的穿通,這要求更高的溝道摻雜來使空間電荷區變得更薄,而更高的溝道摻雜會使閾值電壓升高,為了把閾值電壓控制在合適的值,需要更薄的柵氧化層[2]。

2 EOT縮小的方法

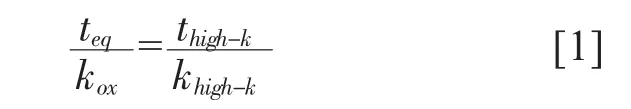

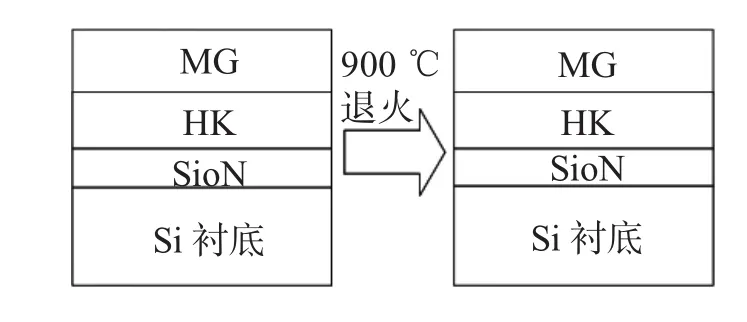

在45 nm技術節點之前,半導體工業界一直采用向SiO2柵介質層中摻入N元素以形成SiON的方法來提高柵介質的相對介電常數k值,而SiON的k值一般為7左右。進入45 nm技術節點以后,SiON材料已不能滿足CMOS器件對超薄柵介質的要求,新型高k柵介質成為最有前景的替代材料[3]。高k柵介質的k值普遍在12以上,這使得在具有同樣EOT的情況下,高k柵介質的物理厚度要比SiO2至少增加3倍以上,從而可以顯著降低柵漏電流。高k柵介質的物理厚度thigh-k、Khigh-k值與SiO2的厚度teq和kox值的關系可表示為:

以下將對高k柵介質/金屬柵結構CMOS器件的幾種EOT控制技術分別進行概述。

2.1 采用復合高k柵介質材料

針對22 nm及以下技術節點的CMOS器件,EOT需要縮小至0.7 nm以下,這對相關工藝技術提出了更高的挑戰,而采用具有更高k值的higher-k柵介質材料是最直接、有效的方法。新一代的高k柵介質材料需要具有更高的k值、合適的帶隙、更好的界面特性以及器件兼容性等特征。表1列出了一些候選的高k柵介質材料的相關信息[3]。

表1 候選的higher-k材料的k值、禁帶寬度以及帶隙

由此可見,La2O3、LaAlOx,HfLaOx等高 k 材料符合獲得更小的EOT需求。另外,面對22 nm及以下技術節點,在Hf基高k柵介質中摻入Ti、Ta、Bi等元素形成的復合高k柵介質,會具有更高的k值,這也是縮小EOT的研究方向之一[4]。但引入新的元素會導致非常多的困難,例如這些元素引入后的高k材料往往帶隙較低[3],導致隧穿電流增加,很難達到小尺寸器件對漏電流的要求,而后續的高溫工藝又會導致低k導致界面層生長,增加了EOT[4],另外,還有一些可能存在的未知的困難。

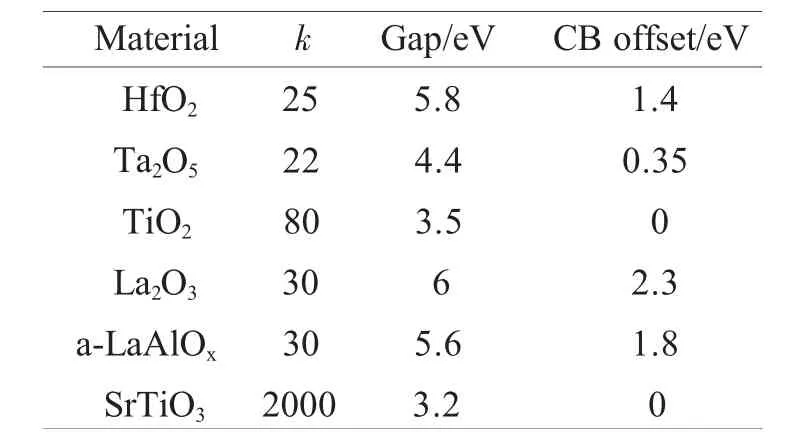

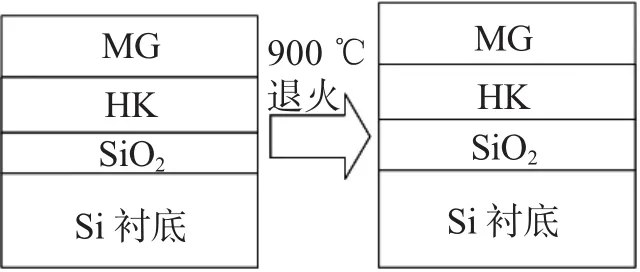

2.2 采用界面控制技術

縮小EOT的第二種方法是采用一些界面控制技術。這種技術能夠解決柵介質層生長完成后,后續工藝帶來的低k值界面層生長的問題。一種簡單可行的辦法是在界面層中摻入N元素以形成SiON界面層,SiON界面層在后續的高溫退火工藝中能夠有效抑制新的SiO2生長[5]。如圖1、圖2所示。

圖1 SiO2界面層在經過高溫退火后厚度增加

圖2 在界面層摻入N元素抑制退火后厚度增加

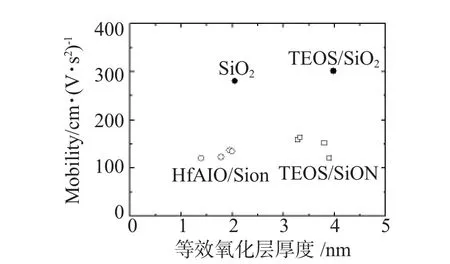

但由于N元素靠近溝道的原因,采用SiON界面層會進一步對溝道載流子產生散射,致使載流子遷移率退化[5],如圖3所示。

圖3 HfAlO/SiON與TEOS-SiO2/SiON,和SiO2在高場強(0.8 MV/cm)下的電子遷移率比較

2.3 采用零界面層

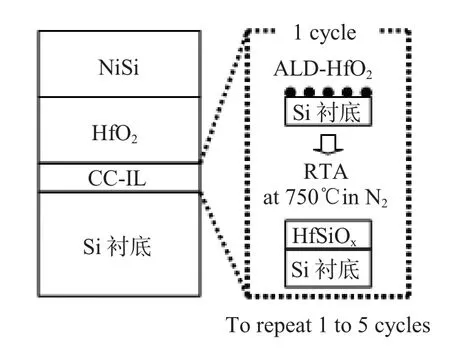

相比較前兩種方法而言,第三種縮小EOT的的方法——采用ZIL(零SiO2界面層)則體現出更多的優勢。在2005年的IEDM上,M.Suzuki等報道了僅有0.3 nmEOT的Mo/LaAlO結構的器件[6],2008年11月,東京工業大學的角島邦之副教授的研究小組報道了在Si襯底上直接淀積La2O3介質材料的研究[7],采用該工藝,可將EOT降至0.37 nm。而M.Takahashi等報道了采用HfSiOx界面層取代SiO2,使得EOT降至0.49 nm的方法,研究展示了一種采用極薄的HfO2與Si襯底反應生成HfSiOx薄膜層的方法,其通過一種Cycle-by-Cycle的工藝實現[8],如圖 4 所示。

圖4 Cycle-by-Cycle HfSiOx界面層生長工藝

該工藝包括幾個周期的重復步驟,一個周期的工藝包括:采用原子層沉積技術淀積HfO2,之后采用750度的RTA退火處理使得Si與HfO2反應生成HfSiOx。但是,這些采用ZIL的工藝都存在一個共同的問題——不能經受接近1 000度源漏退火溫度的考驗,這意味著在傳統的Gate first工藝中,這種采用ZIL工藝的技術沒有實際意義,因為在后續的1000度左右的源漏退火工藝中,SiO2界面層會生長,使得器件EOT迅速增加[9-10]。在2009年的VLSI會議上,J.Huang等人的報道針對該問題提出了解決方案,而且相比起這種Cycle-by-Cycle的復雜工藝,新的工藝更為簡單和優化。該技術直接在HfOx淀積過程中對氧含量進行控制,形成HfOx(x<2)高k層,同時通過該HfOx層,在后續的高溫退火工藝中起到對界面層生長的抑制作用,形成ZIL[4]。采用ZIL工藝縮小EOT并不是沒有代價,在EOT縮小的同時,Si/HK之間的界面質量迅速下降,界面上的缺陷、陷阱和界面電荷大量增加,由此帶來了嚴重的溝道載流子遷移率的退化,另外,由于界面層厚度減小本身也會導致一定的溝道載流子遷移率退化[11]。這些采用ZIL的“副作用”,仍有待解決。

2.4 氧吸除工藝

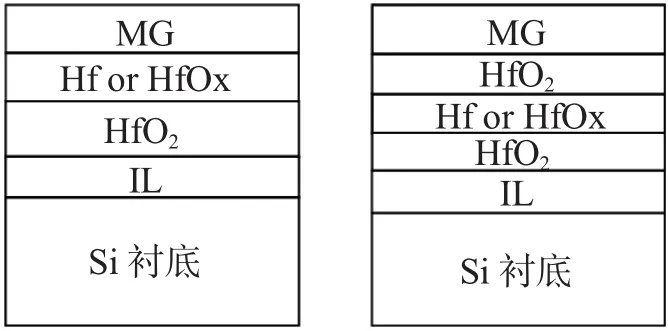

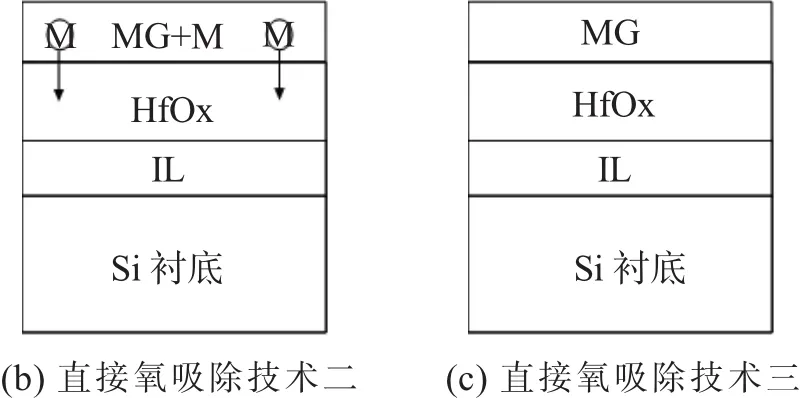

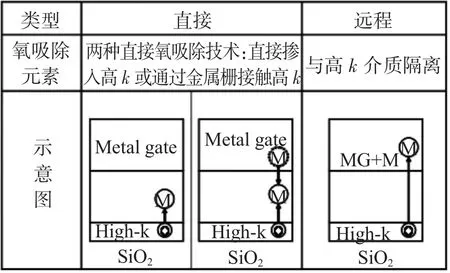

縮小EOT的第四種方法是一種采用氧吸除工藝(oxygen scavenging)的技術,這種工藝是目前最有效的EOT縮小技術[9-14]。相比與ZIL技術而言,氧吸除工藝除了能控制界面層厚度、降低EOT以外,由于并沒有讓高k介質層與Si襯底直接接觸,因此其高k/Si界面質量優于采用ZIL技術的界面質量。氧吸除工藝分為直接氧吸除和遠程氧吸除。直接氧吸除工藝是在高k介質層中直接摻入一種具有氧吸除作用的金屬元素,利用該金屬元素在高溫過程中吸除SiO2界面層中的氧,達到抑制SiO2界面層在高溫過程中的生長,甚至減少SiO2界面層的厚度的目的。其具體實現方式包括3種:(1)直接在高k介質層中混合該元素,在高k介質層上淀積或者在高k介質層中間插入一層極薄的金屬薄膜或金屬氧化物薄膜[8]。(2)在金屬柵中摻入該元素[14],通過熱擴散到達高k介質層。(3)采用類似HfOx(x<2)或者HfSiOx這樣的含有不飽和氧配比的高k介質層[4]。如圖5所示。

圖4 (a) 直接氧吸除技術一

圖5 直接氧吸除技術

直接氧吸除技術能有效抑制IL層的生長甚至達到ZIL的效果。但直接氧吸除工藝仍然有一些問題,因為該工藝需要在高k介質層上或者高k介質層中摻入其他金屬元素,這意味著會改變整個高k介質層,致使高k介質層的各項特性都會隨之改變,以及更多未知的影響,這些影響都會對器件性能以及工藝集成帶來諸多困難和不確定,這不是我們希望看到的。

因此,更為優化的遠程氧吸除技術被重點關注和研究。遠程氧吸除即指在金屬柵極中采用合金的方式加入某種金屬元素或者在金屬柵中淀積一層金屬薄膜,這種金屬元素具有氧吸除的作用,例如在TaN或者TiN[10-13]金屬柵中合金加入該元素。該元素需具備高度的熱穩定性,在高溫過程中不會擴散到高k介質層中。直接氧吸除技術與遠程氧吸除技術對比示意圖如圖6所示。

圖6 直接氧吸除技術與遠程氧吸除技術對比示意圖

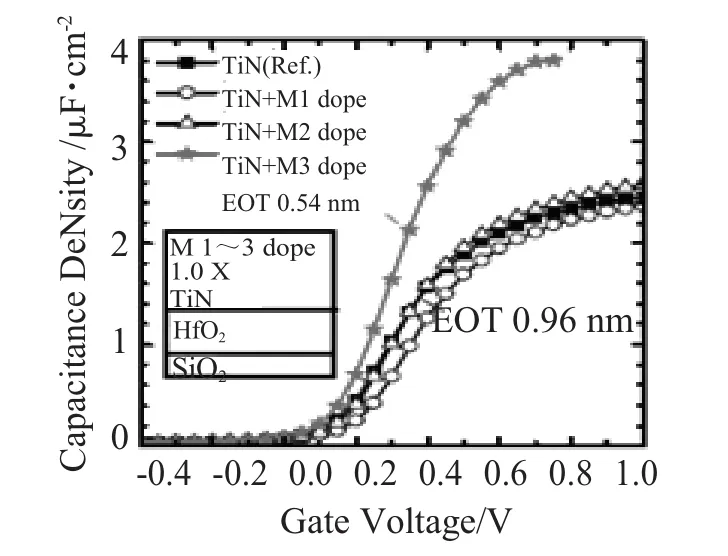

遠程氧吸除工藝的優勢顯而易見,首先,該技術能有效抑制高溫過程中SiO2界面層的生長,甚至降低原有的SiO2界面層的厚度。其效果如圖7的C-V曲線和圖8的TEM圖像所示(注:M3金屬即為在TiN金屬柵中摻入的氧吸除元素):

圖7 采用遠程氧吸除技術與未采用該技術的的器件C-V曲線

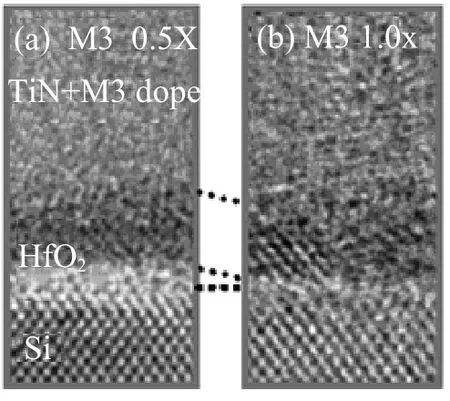

圖8 摻入不同數量M3元素的器件TEM分析圖像對比

其次,采用遠程氧吸除技術的氧吸除元素并沒有擴散進入高k介質層,因此不會有改變高k介質層化學元素組分所帶來的一系列問題。

這項工藝技術實現過程一種可能的機理是:在高溫退火過程中,摻入TiN中的M3元素首先奪走一部分HfO2中的氧原子與其形成M3金屬的氧化物,這時,在HfO2中會產生與被奪走氧原子等量的氧空位。之后,這個氧空位會被由IL層的SiO2中釋放的氧原子填充,而IL層的SiO2則被分解為Si和氧[11]。而另一種可能的機理是:在高溫退火過程中,由于外界的氧不能進入到高k和SiO2界面,而界面SiO2則在高溫下分解,SiO2分解產生的氧被擴散至高k中被臨近的M3元素所吸收形成M3元素的氧化物[15]。

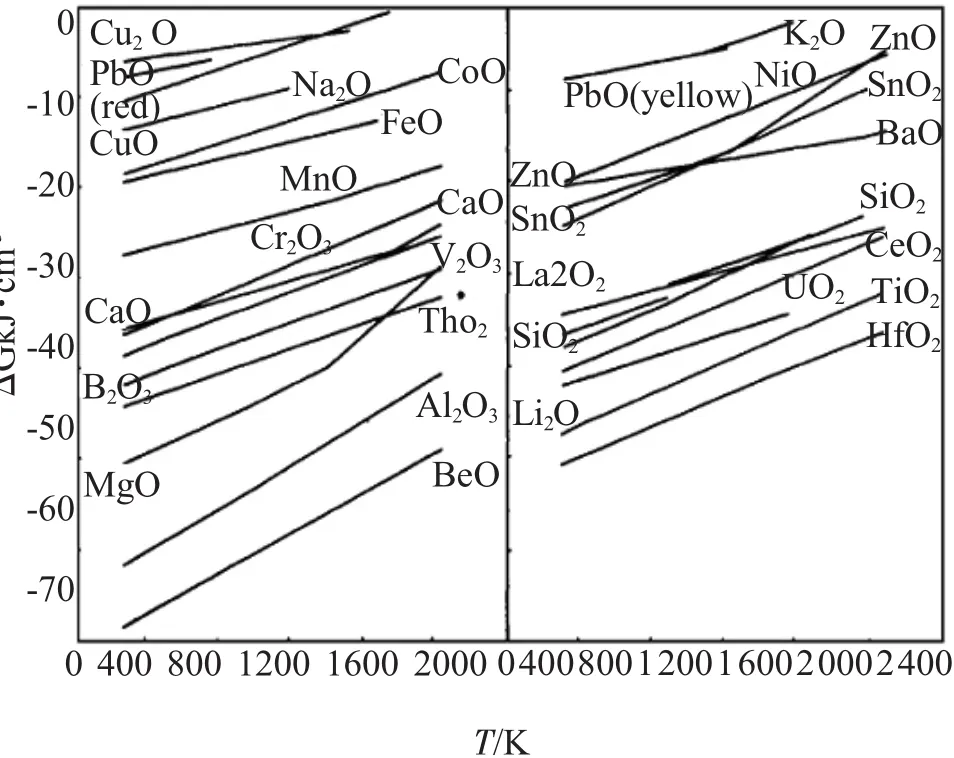

基于熱力學原理,判斷金屬在不同條件下生成氧化物的趨勢大小,一般采用氧化物標準生成吉布斯自由能變化(ΔG)作為熱力學判斷依據[11,16]。圖8為一些氧化物單位體積標準生成吉布斯自由能變化圖。

圖8 氧化物單位體積標準生成吉布斯自由能變化圖

在圖8中,可反映出各種氧化物的形成驅動力有如下排序:BeO>Al2O3>HfO2>MgO>ThO2>CeO2>Y2O3>Cr2O3>FeO>NiO[16]。由此可見,Hf、Al、Ti等氧化物形成驅動力大于Si的元素,均有可能被用做氧吸除元素。但值得注意的是,在高溫情況下(例如1 000 k),各元素的生成吉布斯自由能變化仍可能變化,因此各元素的氧吸除效果需要熱力學計算與實驗結果相結合以確認。

值得注意的是,氧吸除過程需要在對外界氧進行充分隔絕的情況下,因為氧吸除技術的實質即是通過高溫過程在器件柵極結構中進行氧元素的再分配,如果外界氛圍的氧氣輕易的通過熱擴散進入到結構中,氧吸除技術則失去了意義。

3 總結與展望

CMOS器件特征尺寸已縮小至45 nm以下,SiO2或SiON材料柵介質已不滿足柵極絕緣層的性能要求,HK/MG柵極結構將取代SiO2/多晶硅柵極結構使得CMOS器件特征尺寸能夠繼續縮小。但是,面對器件尺寸縮小至32 nm甚至22 nm時,對HK/MG柵極結構亦提出了更高的要求和更多的挑戰。尤其在22 nm以及22 nm以后的工藝節點上,由于嚴重的短溝道效應,要求MOS器件的EOT達到0.5 nm左右,因此,使EOT變得更小的HK/MG技術將被開發出來。本文綜述了基于第一代HK/MG技術上的幾種新的EOT縮小技術,將這幾種技術綜合應用將成為22 nm及22 nm以下節點MOS器件柵極結構的解決方案。

但是,我們仍需要嚴重關注這些EOT縮小所帶來的界面質量變差、溝道遷移率退化、有效功函數調整、以及工藝集成等諸多挑戰。因此,有必要對材料的電學特性和可靠性進行深入研究,尤其是柵極各薄膜層之間的界面特性和相互作用的機理(例如偶極子理論)需要更加深入、全面和細致的研究。

[1] 王陽元,張興,劉曉彥,等.32 nm及其以下技術節點CMOS技術中的新工藝及新結構器件[J].中國科學,2008,38(6):921-932.

[2] 施敏,王國玨.半導體器件物理[M].耿莉,張瑞智.第三版,西安:西安交通大學出版社,2008:250.

[3] John Robertson.High dielectric constant gate oxides for metal oxide Sitransistors[J]Reports on Progress in Physics,2006,69:327–396.

[4] J.Huang,D.Heh,P.Sivasubramani,et al.Gate First High-k/Metal Gate Stacks with Zero SiOx Interface Achieving EOT=0.59 nm for 16nm Application[C]//VLSI Tech,2009:34-35.

[5] Kazuyoshi Torii,Riichiro Mitsuhashi,Hiroshi Ohji,et al.Nitrogen Profile Engineering in the Interfacial SiON in a HfAlO/SiON Gate Dielectric by NO Re-Oxidation[J].Trancationson Electron Devices,2006,53(2):323-328.

[6] Masamichi Suzuki,Mitsuhiro Tomita,Takeshi Yamaguchi,et al.Ultra-thin(EOT=3?)and low leakage dielectrics of La-alminate directly on Si substrate fabricatedbyhightemperaturedeposition[C]//IEDM,2005:433-436.

[7] Kuniyuki Kakushima,Koichi Okamoto,Kiichi Tachi,et al.Further EOT Scaling below 0.4nm for High-k Gated MOSFET[C]//International Workshop on Dielectric Thin Films,2008:9-10.

[8] M.Takahashi,A.Ogawa,A.Hirano,et al.Gate-First Processed FUSI/HfO2/HfSiOx/Si MOSFETs with EOT=0.5nm[C]//IEDM,2007:523-526.

[9] Changhwan Choi,Chang Yong Kang,Se Jong Rhee,et al.Fabrication of TaN-gated Ultra-Thin MOSFETs(EOT<1.0nm)with HfO2using a Novel Oxygen Scavenging Process for Sub 65nm Application[C]//VLSI Tech,2005:226-227.

[10] Changhwan Choi,Chang Yong Kang,Se Jong Rhee,et al.Aggressively Scaled UltraThin Undoped HfO2Gate Dielectric(EOT<0:7 nm)With TaN Gate Electrode Using Engineered Interface Layer[J].IEEE Electron De vice Letters,2005,26(7):454-457.

[11] T.Ando,M.M.Frank,K.Choi,et al.Understanding Mo bility Mechanisms in Extremely Scaled HfO2(EOT 0.42 nm)Using Remote Interfacial Layer Scavenging Technique and Vt-tuning Dipoles with Gate-First Process[C]//IEDM,2009:.423-426

[12] Kaoru Nakajima,Akira Fujiyoshi,Zhao Ming,et al.In situ observation of oxygen gettering by titanium overlayer on HfO2/SiO2/Si using high-resolution Rutherford backscattering spectroscopy[J].Journal of Applied Physice,2007,102:064507.

[13] Kang-III Seo,Dong-Ick Lee,Piero Pianetta,et al.Chemical states and electrical properties of a high-k metal oxide/silicon interface with oxygen-gettering titanium-metal-overlayer[J].Applied PhysicsLetters,2006,89:142912.

[14] K.Choi,H.Jagannathan,C.Choi,et al.Extremely Scaled Gate-First High-k/Metal Gate Stack with EOT of 0.55 nm Using Novel Interfacial Layer Scavenging Techniques for 22nm Technology Node and Beyond[C]//VLSI Tech.2009:138-139.

[15] R.Tromp,G.W.Rubloff,P.Balk,et al.High-Temperature SiO2Decomposition at the SiO2/Si interface[J].Physics Review Letters,1985,55:21.

[16] 李正偉,何業東,齊慧濱,等.金屬氧(硫、碳、氮)化物單位體積標準生成自由能圖[J].中國有色金屬學報,1998,8:增刊 1:55-60.