DDS信號發生器的設計

陳 慧,云乃彰

(1.南京航空航天大學,江蘇 南京 210016;

2.無錫職業技術學院電子信息技術學院,江蘇 無錫 214121)

DDS信號發生器的設計

陳 慧1,2,云乃彰1

(1.南京航空航天大學,江蘇 南京 210016;

2.無錫職業技術學院電子信息技術學院,江蘇 無錫 214121)

利用現場可編程邏輯門陣列(FPGA)實現直接數字頻率合成(DDS)原理以及以DDS為核心的信號發生器的設計,并給出了以單片機80C 51為內核的FPGA的設計方案及信號發生器產生的仿真波形。

直接數字頻率合成技術(DDS);現場可編程邏輯門陣列(FPGA)

作為電子系統必不可少的信號源,在很大程度上決定了系統的性能,因而常稱之為電子系統的“心臟”。傳統的信號源采用振蕩器,只能產生少數幾種波形,自動化程度較低,且儀器體積大,靈活性與準確度差。而現在要求信號源能產生波形的種類多、頻率高,而且還要體積小、可靠性高、操作靈活、使用方便及可由計算機控制。為此可采用直接數字頻率合成(D irec t D igital Syn thesis,簡稱DDS)技術,把信號發生器的頻率穩定度、準確度提高到與基準頻率相同的水平,并且可以在很寬的頻率范圍內進行精細的頻率調節。采用這種方法設計的信號源可工作于調制狀態,可對輸出電平進行調節,也可輸出各種波形。

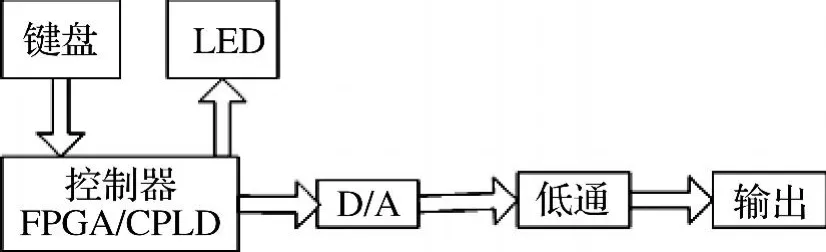

現在我們又可以采用FPGA/CPLD作為控制器,利用其豐富的I/O資源,并行處理數據。并且具有高密度、高速度、多功能、低功耗、設計靈活方便、可無限次反復編程等特點,由FPGA/CPLD完成信號的產生、頻率控制、LED顯示等。該方案的系統方框圖如圖1所示,其優點在于系統結構緊湊,可以實現復雜的測量與控制。

圖1 FPGA控制框圖Fig.1 FPGA con tro l b lock diag ram

1 DDS基本工作原理

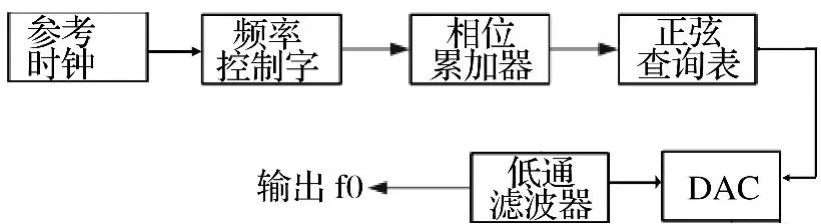

一個典型的DDS系統如圖2所示,相位累加器可以在時鐘的控制下完成相位的累加;相位/幅度碼轉換電路一般由正弦ROM查詢表實現;D/A轉換電路,將數字形式的幅度碼轉換成模擬信號;低通濾波器將DDS產生的混疊干擾濾除等四部分組成。

圖2 DDS基本原理框圖Fig.2 B asic b lock d iag ram of DDS

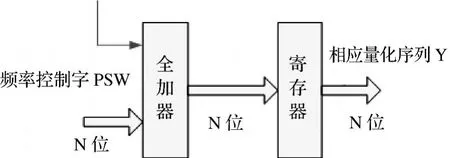

DDS技術的基本原理是利用采樣定理,通過查表法產生波形。它首先對需要產生的波形進行采樣,將采樣值數字化存入存儲器作為查找表,然后再通過查找表將數據讀出,經過D/A轉換器轉換成模擬量,把存入的波形重新合成出來。對每一個時鐘脈沖,N位加法器將頻率控制字FSW與累加寄存器輸出的累加相位數據相加,把相加后的結果送至相位累加器的輸入端。相位累加寄存器一方面將上一時鐘周期作用后所產生的新的相位數據反饋到加法器的輸入端,以使加法器在下一時鐘的作用下繼續與頻率控制字FSW相加,如圖3所示,另一方面將這個值作為取樣地址值送入幅度/相位轉換電路,幅度/相位轉換電路根據這個地址值輸出相應的波形數據。最后經數/模轉換和低通濾波器將波形數據轉換成所需要的模擬波形。這其中導致了各種誤差,尤其是相位截斷誤差,因此各種雜波是不可避免的。

圖3 相位累加器原理框圖Fig.3 Schem atic diagram of the phase accum u lator

2 DDS信號發生器的設計

2.1 累加器模塊

相位累加器是DDS最基本的組成部分,由N位全加器和N位寄存器級聯而成,對代表頻率的二進制碼進行累加運算,產生累加結果Y。相位累加器是一個典型的反饋電路,見圖3。若當前相位累加器的值為∑n,經過一個時鐘周期后變為∑n +1,則滿足:

由上式可見∑n為一等差數列,不難得出

其中∑0為相位累加器的初始相位值。

2.2 ROM查找表

DDS查詢表所存儲的數據是每一個相位所對應的二進制數字正弦幅值,在每一個時鐘周期內,相位累加器輸出序列的高M位對其進行尋址,最后的輸出為該相位相對應的二進制正弦幅值序列。查找表時即是把輸入的地址相位信息映射成正弦波幅度的數字量信號,以驅動D/A轉換電路。

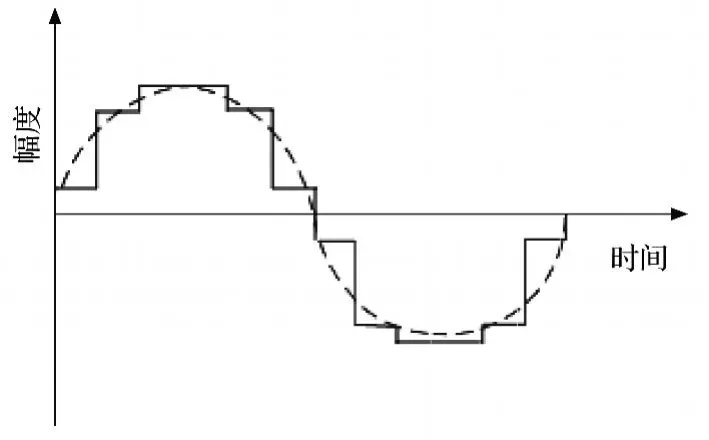

2.3 數模轉換器

數模轉換器的作用是將數字形式的波形幅值轉換成所要求合成頻率的模擬形式信號。DAC有電壓和電流輸出兩種,其輸出的信號并不能真正連續可變,而是以其絕對分辨率為最小單位的,所以其輸出實際上是一個階梯模擬信號。如圖4所示,最后通過低通濾波器平滑后得到一個純凈的正弦模擬信號。

圖4 DAC輸出的模擬信號Fig.4 O u tpu t ana log signal o f DAC

2.4 LED顯示模塊

LED顯示模塊主要是完成頻率控制字的顯示,頻率控制字控制著頻率的大小,而恰好此時的頻率控制字就是系統輸出波形的頻率,所以LED顯示的也是產生波形的頻率。

3 仿真波形與實驗結果

3.1 DDS仿真圖

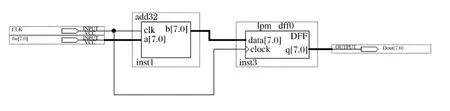

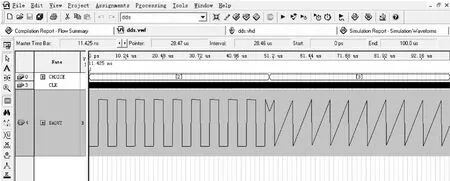

如圖5所示,累加器在時鐘信號(c lock)的作用下完成對各類調制信號的相位累加,累加后輸出的數據作為波形表模塊(lpm dff0)地址輸入信號。

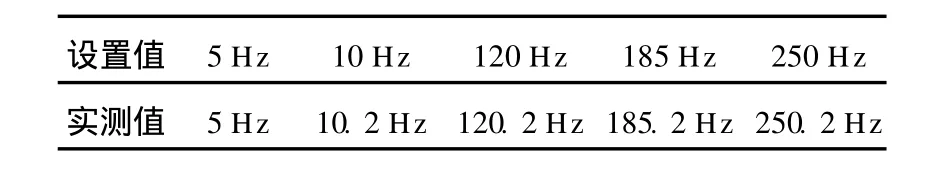

3.2 系統測試結果如表1所示

表1 系統測試結果Tab.1 Test resu lts

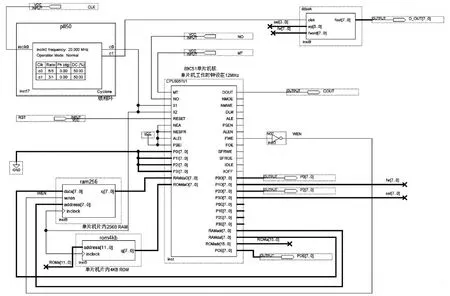

4 總體設計

本設計采用FPGA器件是A ltera公司的Cyc lone II系列的EP2C 5T144,圖6為FPGA內部電路結構圖,以Q uartusⅡ8.1作為硬件開發平臺,采用DDS技術實現全數字波形信號發生器的研制,頻率步進可以很小,切換速度快,頻率控制容易,電路設計簡單。

該圖由以下幾個模塊組成:輸入信號c lock為 50M H z,信號來源于系統有源晶振,輸出頻率CO為125M Hz,輸出頻率C 1為12NHz;RAM的容量是256字節;ROM的容量為4 k字節;89C 51單片機核,單片機工作時鐘設在12M H z;C 1接到DDS的時鐘端,DDS的選擇端由單片機核的P3口的低四位控制,頻率控制字接在P1口。

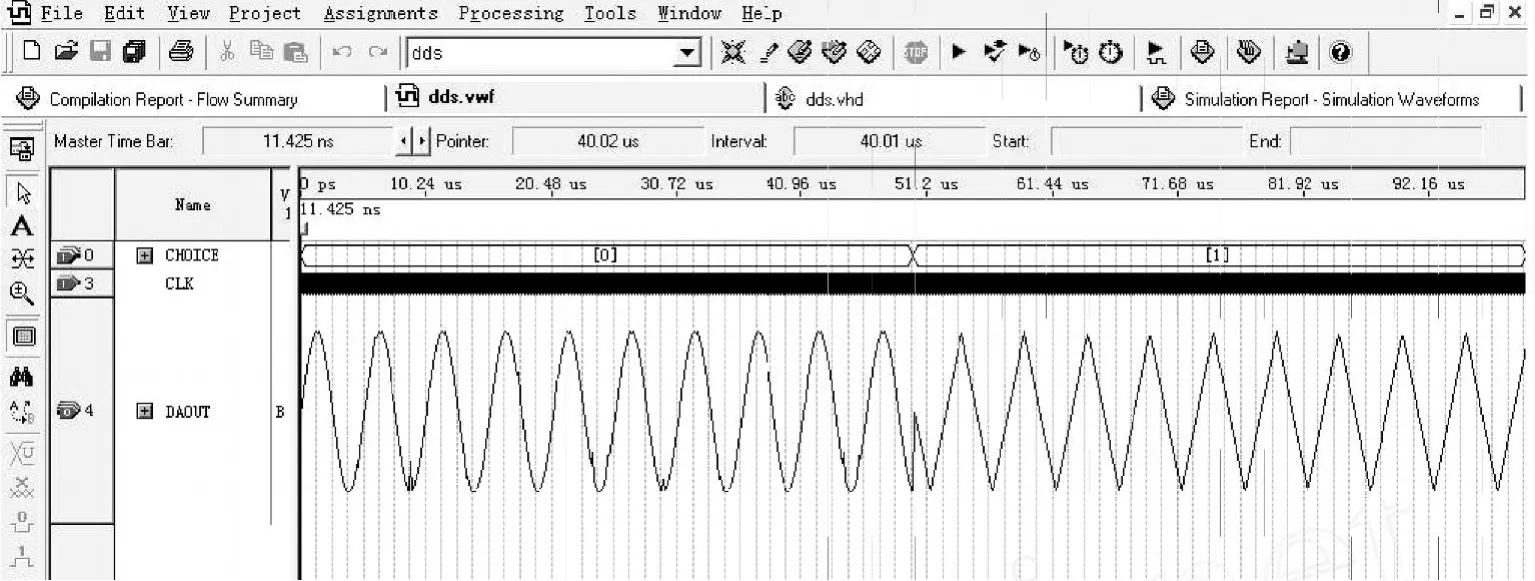

通過仿真可產生基本波形:正弦波、三角波、方波和鋸齒波,如圖7和圖8所示。雖然市場上利用專用DDS芯片開發的信號源比較多,它們輸出頻率高、波形好、功能也較多,但控制方式卻是固定的,因此不一定是我們所需要的。而利用FPGA則可以根據需要方便地實現各種比較復雜的調頻、調相和調幅功能,具有良好的實用性。

圖5 DDS總體仿真圖Fig.5 O verall sim u lation d iag ram of DDS

圖6 FPGA內部電路結構圖Fig.6 In ternal circuit d iag ram of FPGA

圖7 正弦波、三角波波形仿真圖Fig.7 Sinew ave,triang lew ave sim u lation of figure

圖8 方波、鋸齒波波形仿真圖Fig.8 Squarew ave,saw too th w ave sim u lation d iagram

[1] 徐志軍,徐光輝.CPLD/FPGA的開發與應用[M].北京:電子工業出版社,2002.

[2] 潘 松,黃繼業.EDA技術實用教程[M].北京:科學出版社,2005.

[3] 徐 欣,于紅旗,易 凡,等.基于FPGA的嵌入式系統設計[M].北京:機械工業出版社,2005.

Design o fDDS Signa lGene ra to r

CHEN Hui1,2,YUN Nai-zhang1

(1.N an jing U n iversity of A eronau tics and A stronau tics,N an jing 210016,China;

2.E lectrical Info rm ation Institu te,W ux i Institu te of Techno logy,W ux i 214121,Ch ina)

The use of field p rog ramm ab le gate arrays fo r d irec t d igital frequency syn thesis p rincip le and w ith DDS as the co re of the signal generato r.D esign on 80C 51 sing le-chip m ic rocom pu ter as the co re of the FPGA and p resen t the sim u lation w ave fo rm from the signal generato r.

d irec t d igital frequency syn thesis;field p rog ramm ab le gate array

TN 911

A

1671-7880(2010)01-0028-04

2009-12-13

陳 慧(1980— ),女,江蘇丹陽人,碩士研究生,無錫職業技術學院講師。