TMS320C6455的硬件資源分析

謝瑞雯, 陳國興

(西南電子電信技術研究所,四川 成都 610041)

0 引言

DSP技術廣泛應用于雷達、通信、圖像處理等領域[1-2],DSP生產廠家不斷推出新產品,以滿足新一代系統對更高處理性能與更大存儲器容量的需求。德州儀器(TI)日前新推出的高端DSP芯片TMS320C645x,可實現更高性能、更精簡代碼、更多片上存儲器以及超高帶寬的集成外設,包括用于處理器間通信的Serial RapidIO總線。該款新型DSP提升了2至12倍的性能及I/O帶寬,使電信、網絡與視頻基礎設施終端設備以及高端成像系統開發人員可大幅增強系統性能,并在系統內集成更多的高帶寬通道,同時推出更高效率的軟件產品以加快產品的上市進程。

現對TMS320C6455和TMS320C6416T的硬件資源進行分析比較,為C641x DSP開發人員升級到TMS320C6455提供有效的參考幫助。

1 TMS320C6455硬件配置及初始化設置

TMS320C6455硬件配置及初始化設置參考文獻[3-4]。C6455的程序引導模式和硬件配置由上電復位的時候決定。不同于C6416T的是,外設資源的使能/關閉是上電復位后由相應的寄存器進行控制,而 C6416T的外設資源在上電復位以后都是使能的。由于C6455缺省情況下所有外圍設備資源是不可用的,所以一級引導程序中必須將下級引導程序中用到的外圍設備接口打開,才能繼續下一步的工作。

C6455的硬件配置選項由地址線AEA[19:0]和ABA[1:0]決定,若要改變默認配置選項,可在這些地址線上外接 1K的上拉/下拉電阻。C6416T在上電復位時就決定了內部時鐘鎖相環倍頻率,而C6455的鎖相環倍頻率控制寄存器在上電復位階段是不會被檢測的,需要在程序中進行設置。C6455對內部ROM進行讀取時,內核時鐘頻率不能超過750 MHz;在PCI/RapidIO引導模式下相環倍頻率固定為15,所以這2種引導模式下 C6455的 CLKIN1輸入時鐘頻率不得超過 50 MHz。在其它引導模式下,最好在啟動開始、初始化其它外設資源之前就先設置好鐘鎖相環倍頻率。

TMS320C6455復位和上電時的引導模式主要有:NO BOOT模式、主機(HPI/PCI接口) 引導模式、FLASH引導模式、主I2C引導模式、從I2C引導模式、SRIO引導模式。采用哪種引導模式,由復位或上電時采樣管腳BOOTMODE3~0來決定。在C6455的地址空間0x100000到0x107FFF之間集成了32 K的內部 ROM,其中固化了一段引導代碼,用來在上電時,對DSP進行必要的配置和代碼加載。

2 TMS320C6455的外圍設備資源

TMS320C6455的外圍設備資源參考文獻[5-6]。

2.1 TMS320C6455的外部存儲器接口EMIFA

C6455保留了 C6416T的 64-bit寬的外部存儲器接口EMIFA,其輸入時鐘可以由外部輸入,也可由內部產生。外部時鐘由AECLKIN腿輸入,內部產生的時鐘信號SYSCLK4由內核時鐘分頻而來,默認情況下是內核時鐘頻率的 1/8,分頻因子可以通過PLL的軟件寄存器進行設置。而對于C6416T,內部產生時鐘固定為內核時鐘頻率的1/4或者1/6。

2.2 TMS320C6455的主機口HPI和PCI接口

C6455的主機口HPI與PCI接口復用,在上電復位時決定選擇采用HPI還是PCI。若采用HPI接口,在二級引導程序中設置HPI總線寬度(32 bit/16 bit);若采用PCI接口,則二級引導程序中設置PCI的啟動方式和總線頻率(33/66 MHz)。

如果系統中不使用HPI/PCI口時,最好將不用的管腿接上上拉電阻,以避免不必要的功耗的產生。

2.3 多通道緩存串口McBSP

C6455的McBSP與C6416T的用法基本相同, McBSP的數量由C6416T的3個減為C6455的2個;C6455的2個McBSP共用一個外部時鐘CLKS信號,而C6416T的3個McBSP有各自獨立的CLKS信號;C6455的McBSP的內部時鐘源為內核時鐘的1/3,而C6416T的McBSP的內部時鐘源為內核時鐘的1/4。

2.4 譯碼協處理器VCP2和TCP2

C6455的維特比譯碼協處理器VCP2和Turbo譯碼協處理器TCP2在C6416T的VCP和TCP的基礎上,功能和性能上都有了較大的提升。它們不僅全面兼容VCP和TCP,而且無論在譯碼速度、動態范圍、支持的幀長和編碼方式、編程的靈活度以及功耗等方面都有了比較大的改進。

具體來說,VCP的運行時鐘等于CPU內核時鐘/4,而VCP2提升到了CPU內核時鐘/3;分支度量(Branch Metrics)的位寬由VCP的7 bit提高到了VCP2的8 bit,VCP2支持的最大滑動窗口也比VCP的增加了30%左右。對于Turbo譯碼協處理器來說,TCP2的時鐘由TCP的CPU內核時鐘/2降到CPU內核時鐘/3,但是支持一次性譯碼幀長由TCP的5114增大到20730,支持的編碼率在TCP的1/2、1/3和1/4的基礎上增加了3/4和1/5的編碼率,支持重復譯碼和休眠模式等。

2.5 增強型直接存儲器訪問EDMA3

C6455的增強型直接存儲器由C6416T的EDMA2升級到了EDMA3。EDMA3的參數RAM大小由EDMA2的6個32 bit字增大到了8個32 bit字,并且參數RAM內對應的事件是靈活可配置的;EDMA3的源和目的地址的索引可以單獨控制,而EDMA2的源和目的地址的索引是相同的;傳輸塊的維數由原來的2維增加到了3維;EDMA3將QDMA的功能統一起來,提供更加靈活的 QDMA的配置;增加了錯誤中斷機制;并且增加了DMA區域訪問、內存保護、可視化調試、錯誤檢測等功能,極大的方便了設計人員的開發與調試。

2.6 C6455增加的其它外設資源

C6455能夠提供比C6416T更加豐富的外設資源。片上集成了I2C串行總線接口,通過I2C總線,C6455可以很方便的通過數據線SDA和時鐘SCL構成的串行總線發送和接收數據。C6455片上集成的千兆以太網MAC支持4種以太網媒體接口:MII、RMII、GMII和RGMII。其中MII支持10兆和100兆的操作, RMII是簡化的MII接口,同樣支持10兆和100兆的總線接口速度。GMII是千兆網的MII接口,這個也有相應的RGMII接口,表示簡化了的GMII接口。C6455還提供了異步傳輸模式 (ATM) 鏈路與物理層 (PHY) 芯片之間的標準接口 UTOPIA,它與 MII/RMII/GMII接口復用,當使用UTOPIA接口時,EMAC只能使用RGMII接口。C6455還提供4個串行快速I/O口SRIO,由于SRIO通過提供極低時延、高帶寬(10Gb/s全雙工)與低引腳數連接等優異特性消除了I/O瓶頸,因而使系統性能提升了12倍。除此之外,C6455用533MHz的DDR2外部存儲器接口替代了C6416T的EMIFB接口,將數據總線寬度擴展到32 bit,容量達到512 M字節,實現了存儲器I/O與處理器性能的完美平衡。

3 TMS320C6455與TMS320C6416T硬件資源對比

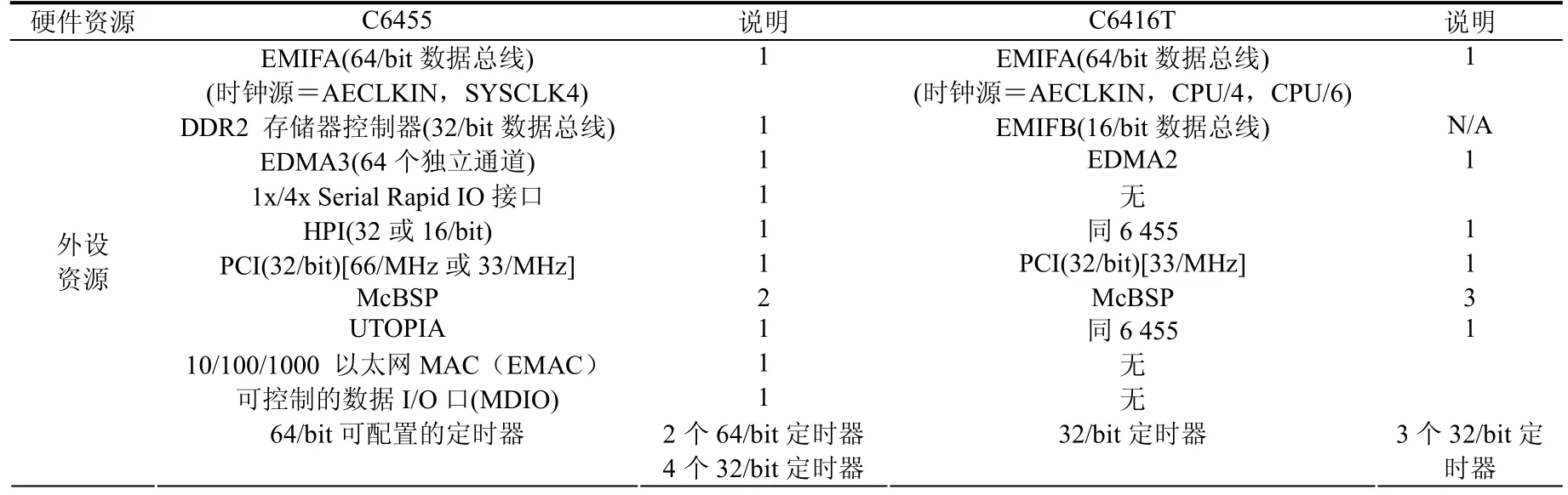

表1給出了TMS320C6455與TMS320C6416T硬件資源的異同點。

表1 TMS320C6455與TMS320C6416T硬件資源對比

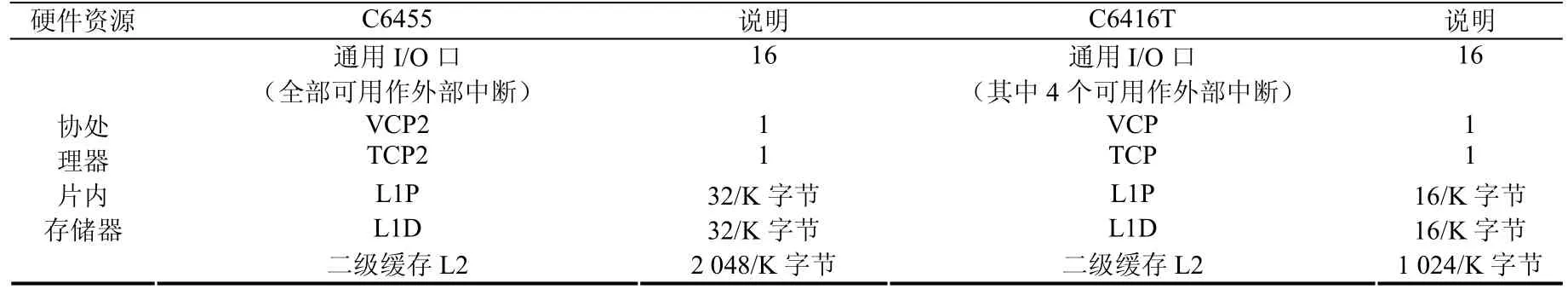

續表1

4 結語

C6454 DSP是C641x DSP開發人員尋求升級的理想之選,它建立在增強型TMS320C64x+DSP內核與TI最高性能DSP架構基礎之上,不僅為開發人員提供了兩倍于 641x的存儲器容量與 I/O帶寬,還具備其它高級特性與功能,提供了更加豐富、更高級的外設。C6455可以應用于各種基礎局端設備,包括高端電信設備、無線基礎局端以及視頻與影像應用等領域,是一款應用前景非常廣泛的DSP器件。

[1] 汪安民,張松燦,常春藤. TMS320C6000DSP實用技術與開發案例[M].北京:人民郵電出版社,2008:67-70.

[2] 呂穎利,李文峰. DSPC6000環境下視頻輸入輸出驅動程序開發[J].通信技術,2009,42(11):45-47.

[3] Texas Instruments. Literature number SPRS276H.TMS320C6455 Fixed-Point Digital Signal Processor[S].[s.l.]Texas Instruments Incorporated,2007.

[4] Texas Instruments. Literature number SPRU871J.TMS320C64x+ DSP Megamodule Reference Guide[S].[s.l.]Texas Instruments Incorporated,2008.

[5] Texas Instruments. Literature number SPRS226L. TMS320C6414T,TMS320C6415T, TMS3206416T fixed-point digital signal processors[S].[s.l.] Texas Instruments Incorporated,2008.

[6] Texas Instruments. Literature number SPRUE52.TMS320C645x DSP Peripherals Overview Reference Guide[S]. [s.l.]Texas Instruments Incorporated, 2006.