64QAM系統中濾波器在脈沖成形和符號同步中的應用和實現

張 軍 鐘洪聲

(電子科技大學,四川 成都 611731)

64QAM系統中濾波器在脈沖成形和符號同步中的應用和實現

張 軍 鐘洪聲

(電子科技大學,四川 成都 611731)

主要討論64QAM全數字調制解調系統中,濾波器在基帶成形(接收端為匹配濾波)和符號同步這兩部分的實現方法。給出這兩部分的實現思想:基帶成形部分是由加窗的根升余弦濾波器來實現,結合FPGA,采取并行流水線和查找表的結構來實現。符號同步部分考慮插值濾波器的實現方法,采用能適用于Fallow結構的直線型插值、分段拋物線型插值和立方插值。最后,在此基礎之上,仿真出FIR濾波器的滾降系數和碼間串擾之間的關系,同時針對誤差檢測器的自噪聲過大問題,提出一種在誤差檢測器中增加一個簡單的高通濾波器這種改進方案來減小檢測器的環路誤差。

濾波器;脈沖成形;符號同步;插值

(一)前言

QAM(Quadrature Amplitude Modulation)是一種頻帶利用率高和抗干擾能力強的調制解調技術。在全數字64QAM系統中,濾波器是基帶信號處理的重要組成部分:成形(匹配)濾波器可以消除由于帶限引起的碼間干擾(ISI),而符號同步中的濾波器如插值或多項等濾波器更是接收端位同步電路的核心部分。設計一種高速、所占資源少和性能優良的濾波器具有重要的意義。

(二)基帶成形濾波器的設計

1.根升余弦FIR(有限沖擊響應)濾波器的基本思想

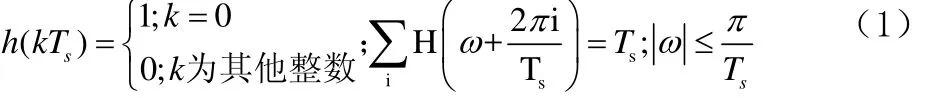

Nyquist第一無失真準則告訴我們:如果信號傳輸后整個波形發生了變化,但只要其特定點的抽樣值保持不變,那么用再次抽樣的方法仍然可以準確的恢復原始信號,即:每個抽樣時刻只對當前符號有響應,對其他符號的響應全等于0,那么ISI影響就可以消除,基帶系統沖擊響應和頻域條件為:

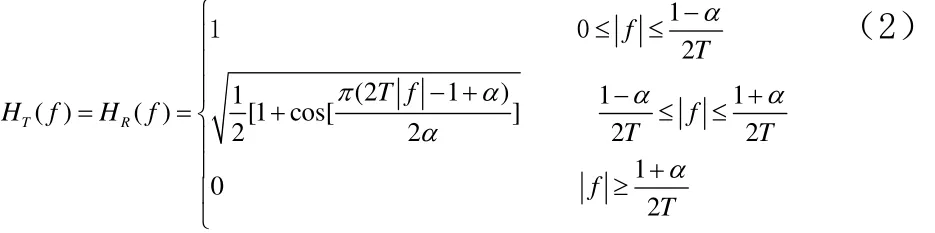

由于理想低通濾波器的不可實現性,實際應用中廣泛采用的成形濾波器是升余弦濾波器,它有一個平滑的過渡帶,通過引入滾降系數,改變傳輸信號的成形波形,效果逼近理想低通濾波器。考慮到發射端和接受端的匹配問題,一般使用根升余弦濾波器,公式如下:

根升余弦濾波器的時域特性和幅頻特性分別為下圖(1),圖(2)所示:

圖(1)根升余弦濾波器時域特性曲線

圖(2)根升余弦濾波器頻域特性曲線

2.根升余弦FIR濾波器的仿真與FPGA實現

(1)FIR濾波器的Matlab仿真

由于FIR濾波器具有穩定、線性相位特性、系數對稱特性、只含實數運算等突出優點,非常適合相移調制。其中窗函數法設計比較簡便,常用到的有漢寧、漢明和凱塞爾窗等。以下是matlab常見的函數:

B=firrocs(N,fo,df,type,delay,window):N為濾波器階數;fo是截止頻率;df為過渡帶頻率;type默認為升余弦,若為’sqt’為根升余弦;delay為延時;window是窗的類型。

(2)FIR濾波器的FPGA實現

FIR濾波器具有線性相位,其系數對稱,方程為:

由上式可以看出:使用FPGA實現時占用資源和影響速度最多的是乘法器,優化乘法器設計主要從兩個方面考慮:減小部分積個數和提高部分積相加的運算速度。以下是主要的設計思想:

文獻[1],[2]介紹一種分布式算法(DA:distributed arithmetic),是一種將固定系數的乘積和運算轉化為查表操作,提供了不用乘法器實現FIR濾波器的方法,非常適合于FPGA實現。

文獻[3]介紹了流水線技術和改進Booth算法相結合的設計。流水線技術是把一個周期內執行的邏輯操作分成幾步較小的操作,并在多個高速的時鐘下完成,每次邏輯小操作的結果都存儲在寄存器中,被高速時鐘同步以便下一個流水單元使用。改進的Booth算法是將Booth乘法器分成Booth編碼模塊、部分積加法器陣列模塊以及最終加法器模塊。這樣可以把部分積得數目減小到原來的一半。

文獻[4]介紹正規則符號數(CSD)編碼、wallace樹結構以及超前進位加法器相結合的設計方法。

FIR濾波器的FPGA實現設計思想比較成熟,以上參考文獻中也講的比較詳細,這里就不過多贅述。

2.根升余弦FIR濾波器的抗時鐘抖動分析

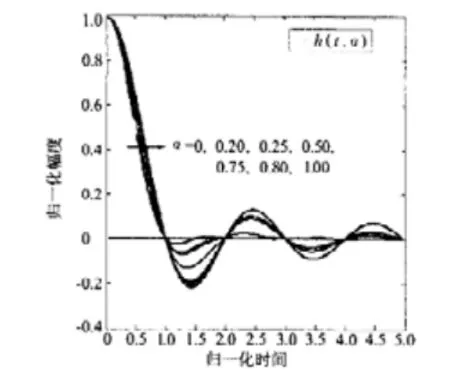

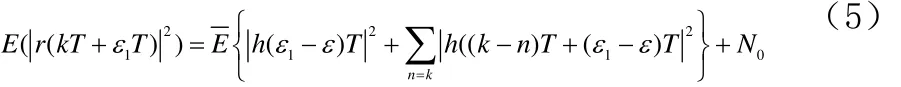

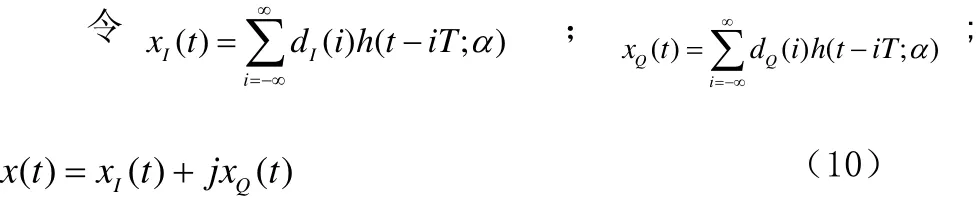

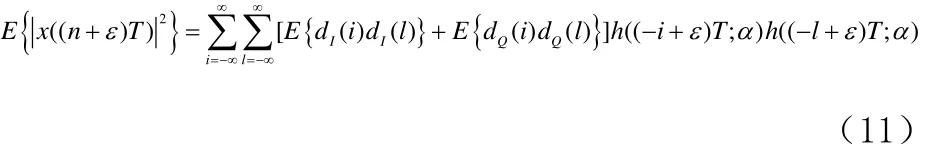

根升余弦濾波器可以抑制ISI的影響,但不同的成形濾波器,抗時鐘抖動的效果是不同的,通過使用Matlab對平方根升余弦進行仿真,可以掌握它們抗時鐘抖動的特性。接收信號其中an:傳輸數據;h(t):成形濾波函數;Tε:時鐘延時兩邊做均方運算:其中

N0代表點態噪聲的平均干擾量;考慮到噪聲的存在,把碼間串擾量當作干擾噪聲,可定義

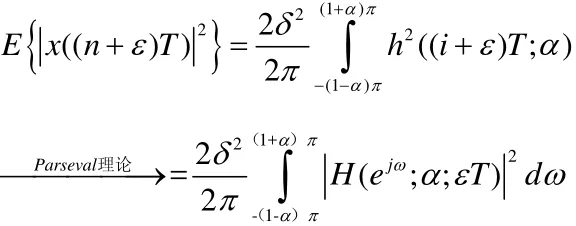

為碼元ak在t=kT+ε1T時刻的碼間串擾量的度量。通過Matlab仿真,如圖(3)

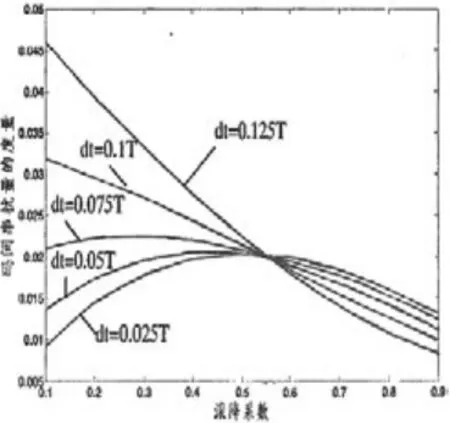

圖(4)全數字字符同步環路電路框圖

圖(3)平方根升余弦濾波器的碼間串擾曲線

由上圖(3)可知:1)碼間串擾量隨采樣時鐘誤差的增加而增加;2)對相同采樣時鐘誤差,碼間串擾隨根升余弦的滾降系數變大而減小(因為滾降系數越小,濾波器沖擊響應的旁瓣電平幅度越小,對誤差靈敏度越小);3)對采樣時鐘偏差遠小于0.1T時,碼間串擾量隨滾降系數增加有個很小上升的過程,這是因為根升余弦濾波器沖擊響應序列本身也存在一定的碼間串擾,在采樣點處旁瓣電平并不為零。

(三)插值濾波器的設計

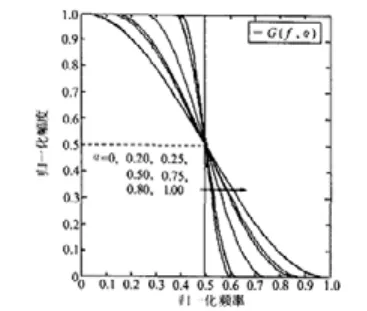

1.符號同步框圖(如圖(4))

內插器:從輸入的非同步AD轉換器采樣信號中恢復出發送的符號

內插控制過程:獲取環路濾波送來的定時誤差參量,進行相關計算后得到下次采樣點的位置。然后通過NCO產生過零信號觸發重采樣,并將殘留值kμ送給內插器更新抽頭系數

設計指導思想:利用定時誤差檢測和內插控制手段對獨立的信號樣本進行插值運算,以得到最佳采樣時刻的近似值[5]。

2.插值濾波器的設計

(1)插值濾波器的表達式:

其中mk是整數的基本指針(NCO產生),kμ是小數的分數間隔 (分數間隔器產生)。

(2)插值濾波器的實現

內插濾波器的構造函數有很多,如:sinc內插、多項式內插、三角內插、多相內插等,其中多項式內插濾波器的單位脈沖響應具有多項結構或分段結構,適合采用Farrow結構實現,并可以大大降低實現復雜度。Gardner詳細比較了線性(一階)、分段拋物線(二階)、立方(三階)拉格朗日多項式插值算法的性能,綜合考慮,立方拉格朗日多項式插值效果最好。

文獻[6]詳細地介紹了多項式插值以及基于Farrow結構的濾波器實現方法。除了使用插值濾波器實現符號同步外,也有使用基于多相濾波器組來重新采樣的。文獻[7]就介紹了通過一個低通濾波器取不同群延遲而導出的多項濾波器組。文獻[8]提出一種在采樣點插值和多相濾波器方法基礎上,通過對匹配濾波器脈沖響應改變其群時延特性,實現符號同步的方法。

目前有很多文章來介紹插值濾波器的FPGA實現,在這里就不過多論述。

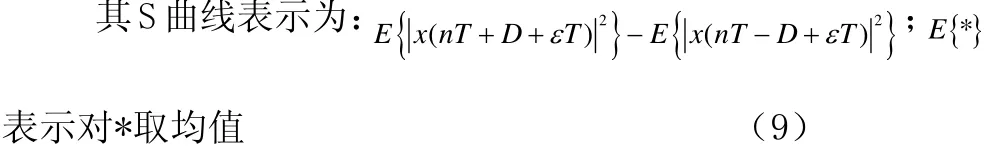

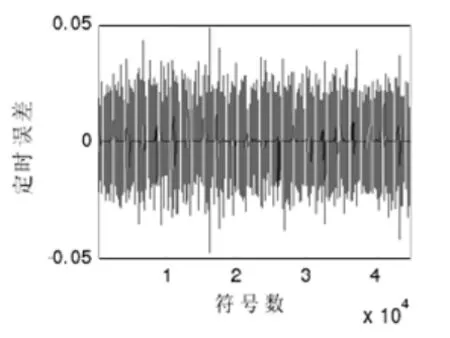

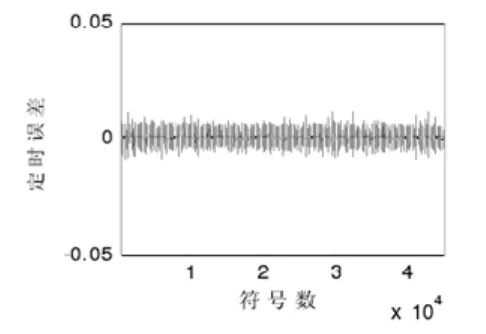

3.濾波器對環路誤差的改善

由于QAM信號的隨機性,Gardner算法的定時誤差檢測器在符號同步環路達到收斂狀態后依然會產生比較大的自噪聲,造成定時抖動。文獻[5]提出了一種利用內插控制部分的NCO產生無抖動的時鐘,并用該時鐘重新產生內插數據,從而達到減小這種定時抖動。本文引入一種在定時誤差檢測器中增加一個簡單的高通濾波器來減小誤差檢測器的自噪聲的方法。

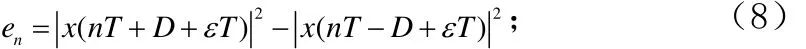

定時誤差表示為:

其中h(t,α)是升余弦滾降濾波器的沖擊響應;dI(i),dQ(i)是QAM信號同相量和正交量數據。

將t=(n+ε)T 帶入x(t),再令n=0,可得

若dI(t),dQ(t)均值為零且具有同方差δ2相互獨立序列,則(11)可簡化為:

圖(5)Garnder檢測器環路誤差

圖(6)改進的檢測器環路誤差

(四)結論

通過對64QAM系統基帶濾波器的仿真,找出了成形濾波器中滾降系數、時鐘采樣誤差和碼間串擾度量三者之間的關系;通過在誤差檢測器中增加一個高通濾波器,有效地減小了定時抖動,使改進后的抖動僅為原來的1/5。

[1] 衛強,葉亮,劉其中.高速FIR濾波器的設計與FPGA實現[J].測控技術,2007.26:92-95.

[2] 李文剛.基于FPGA的高速、高階FIR濾波器的設計[J].四川理工學院學報,2005.3.18(1):38-41.

[3] 劉軍黃,君凱,易清明.一種高速FIR濾波器的設計及實現[J].微電子學與計算機,200.7.21(7):150-152.

[4] 萬超.高速FIR濾波器的設計與實現[D].合肥:合肥工業大學,2007.12.

[5] 汪中.DVB-C接收機符號同步內插的算法設計與仿真[D].成都.電子科技大學,2007.5.

[6] 葉雙應.QAM解調芯片中匹配插值濾波器的設計與實現[D].南京.東南大學.2006.3.

[7] 易鴻鋒,谷春燕.一種高精度的符號定時同步方法[J].西安電子科技大學學報,2005.12.32(6):915-919

[8] 劉祖軍,王杰令,易克初.一種采用匹配濾波器插值的符號定時同步方法[J].西安電子科技大學學報,2008.12.42(12):1550-1554.

TN713

A

1008-1151(2010)04-0045-03

2010-01-03

張軍(1976-),男,江蘇徐州人,電子科技大學電子信息工程學院碩士研究生,研究方向為64QAM系統中濾波器的應用。