一種遠程配置FPGA的設計方法

張學森 李宏 中國電子科技集團公司第38研究所 230031

一種遠程配置FPGA的設計方法

張學森 李宏 中國電子科技集團公司第38研究所 230031

遠程配置FPGA是通過對FPGA配置芯片的讀寫實現對FPGA設計的更新。本文主要介紹了一種基于片上可編程系統(SOPC)技術,通過以太網實現對現場可編程邏輯器件進行遠程更新配置文件的設計方法。

FPGA;片上可編程系統;遠程配置

FPGA; system on a programmable chip(SOPC);remote configuration

1、引言

隨著FPGA廣泛的應用于很多領域,在有些領域要求系統具有遠程更新設計的功能,而對FPGA設計的升級必須更新FPGA的配置文件才能完成,目前很多方案都是基于CPU+CPLD+FLASH方案,其原理是通過CPU獲得遠程加載數據寫入FLASH存儲器,CPLD電路從FLASH讀取配置數據產生相應的時序對FPGA進行配置。本文主要介紹在Altera公司的FPGA里運用SOPC設計手段,嵌入Nios II軟核處理器技術,通過對FPGA配置芯片EPCS器件的讀寫實現對FPGA設計的更新。

2、SOPC技術及FPGA常用配置方法簡介

SOPC(System on a Programmable Chip:片上可編程系統)是Altera公司提出來的一種靈活、高效的片上系統(S O C)解決方案,它將處理器、存儲器、I/O口等系統設計需要的功能模塊集成到一個可編程器件上,構建成一個可編程的片上系統,根據系統實際需求可裁減、可擴充、可升級,并具備軟硬件編程的功能。Nios II 是Altera 公司為SOPC設計提供的軟核處理器,它具有32位處理器的基本結構單元—32位指令大小,32 位數據和地址總線,32 位通用寄存器和32個外部中斷源,其處理速度可達到200DMIPS,Nios II 軟核發展至今主要以下幾大特點:1)在一片FPGA器件里可配置多個軟核處理器;2)支持操作系統的移植;3)支持硬件加速;4)支持用戶接口的開發。

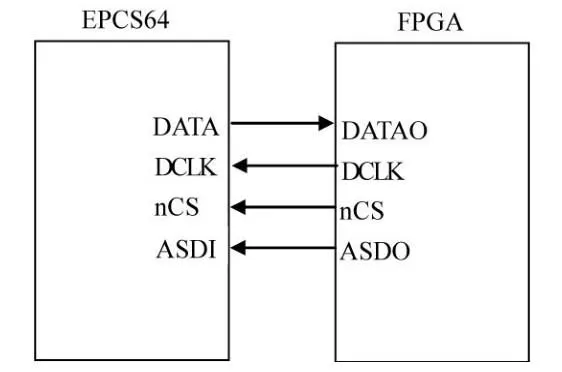

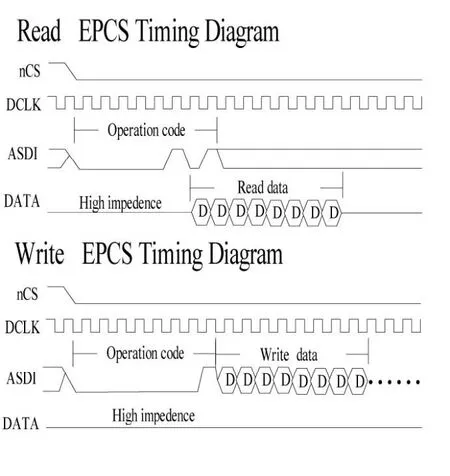

FPGA的配置器芯片常用的有兩大類:一類配置芯片是主動的,其代表是EPC16系列, 這類器件可以主動產生F P G A配置時需要的時序,把其內部FLASH存儲的文件加載到FPGA;另一類是配置芯片是被動的,其代表是EPCS系列,FPGA需要主動產生相應的時序去讀寫這類芯片內的FLASH。本文介紹配置系統中選用的EPCS系列的EPCS64,其配置連接關系如圖1, EPCS64是串行被動配置芯片,內部有64Mbits數據存儲空間。配置系統的讀寫時序關序如圖2。

圖1 串行配置芯片與FPGA接法

圖2 EPCS讀寫時序圖

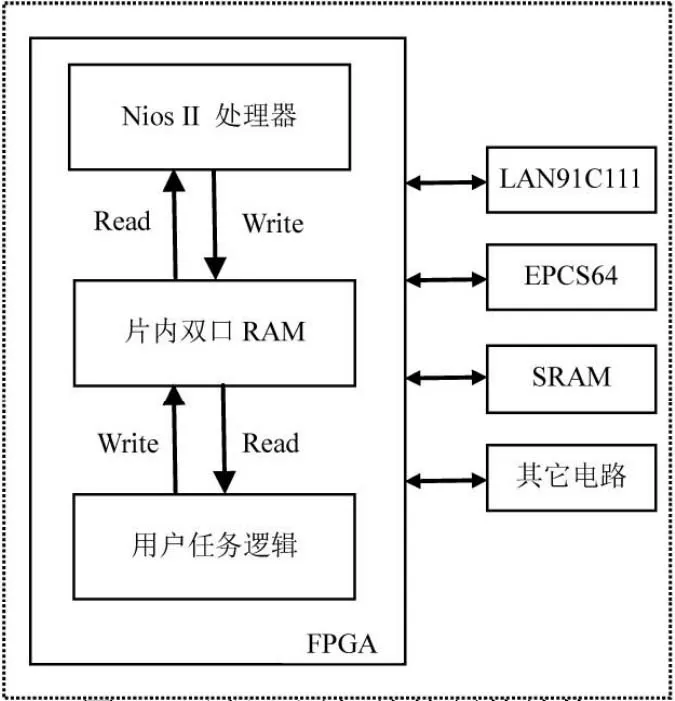

圖3 遠程配置相關的硬件結構

3、遠程配置的硬件架構

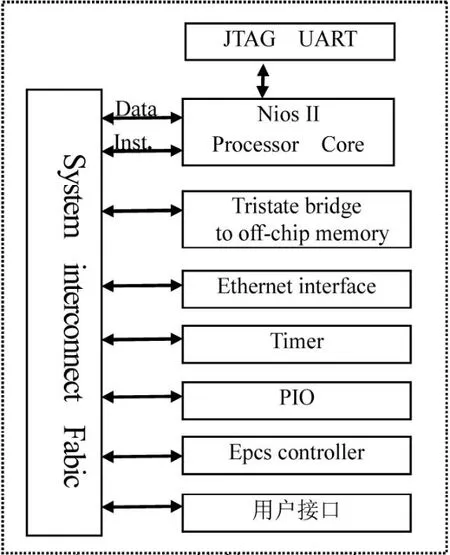

在某系統中,其遠程加載功能部分涉及到的硬件結構如圖3,圖3中FPGA選用的是EP2S30系列,其內部大部分邏輯是用來完成用戶任務,另外一部分是Nios II處理器及其相關外圍接口電路控制;以太網接口芯片選用了SMSC 公司推出的LAN91C111 芯片,該芯片內部集成了以太網介質訪問(MAC) 及物理層收發器(PHY) ,支持10M/100M 全雙工傳輸模式、自動協商等功能;EPCS64芯片用來存儲FPGA配置文件、Nios II運行程序以及用戶數據;SRAM是Nios II 程序運行的空間;FPGA內部的雙口RAM是用戶任務邏輯與Nios II 之間交換數據的空間。軟核處理器Nios II配置的相關資源如圖4。整個系統配置啟動過程如下:FPGA上電啟動時,主動從EPCS器件里讀取其自身加載文件,讀寫完畢后,FPGA開始正常工作,FPGA內嵌入的Nios II 處理器的EPCS controller從EPCS相應存儲空間里搬移程序運行文件至Nioss II程序運行空間SRAM,搬移完后,Nios II開始正常工作。

圖4 配置軟核處理器資源

4、遠程配置的軟件設計

在某系統中,Nios II處理器里嵌入了uC/os II操作系統,嵌入式操作系統uC/os II是基于任務優先級的多任務的微內核RTOS,其源代碼公開,可移植性好,可裁減。Altera公司已在其Nios II開發環境里嵌入了uC/os II操作系統,設計者僅根據需要去選擇。所以該系統中Nios II需處理的任務都是在uC/os II操作系統架構下完成的,本節僅介紹遠程配置任務的軟件設計。

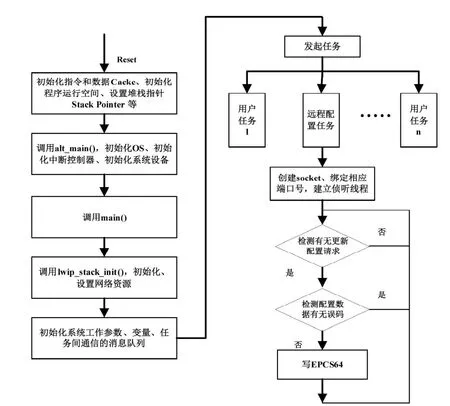

對于NiosII處理器來說完成對FPGA配置的任務主要需要解決兩個問題:一個是獲得遠程配置更新的數據,一個是將配置數據寫入配置芯片。在此我們利用網絡技術獲取遠程配置數據,在uC/os II操作系統采用輕量級網絡協議LWIP(Light weight IP,LWIP), LWIP是一種專門針對嵌入式系統應用而設計的網絡通信協議,由于LWIP 實現的關鍵在于削減代碼大小和內存消耗,在網絡協議棧初始化后,使用標準套接字API 創建新任務訪問網絡協議棧就可以實現網絡通信了。對于配置芯片讀寫是通過EPCS_contrller接口去控制的,該接口根據Nios II處理器發出的指令,產生類似圖2所表述的時序。其軟件具體流程如圖5。

5、結論

本文論述了遠程配置FPGA的設計方法,該設計方法基于SOPC 和嵌入式系統技術,實現了遠程更新FPGA的配置文件及Nios II的運行軟件,完善了SOPC設計。整個系統僅集中在一片FPGA里完成,系統安全可靠,應前景廣闊。

圖5 遠程配置軟件設流程

[1] Altera Company. Nios II Processor Reference Handbook [ Z] .2009

[2] Altera Company. Nios II Software Developer’s Handbook

[3] JEAN J.LABROSSE,邵貝貝譯. uC/OS-II 源碼公開的實時嵌入式操作系統[M].北京,中國電力出版社

A Design Method for FPGA Remote Configuration

Zhang Xuesen Li Hong38th Research Institute of China Electronic Technology Corporation, Hefei230031,China

Update the design of FPGA depend on reading &writing the configurable chip, that is FPGA remote configuration. A design method for FPGA remote updating and configurating files on Ethernet base on system on a programmable chip(SOPC) in the article.

10.3969/j.issn.1001-8972.2010.14.048

張學森 男,1979年,工程師,研究方向:雷達信號處理,陣列信號處理;

李宏 男,1979年,工程師,研究方向:雷達信號處理,陣列信號處理。