SOC中的MBIST設計

桂江華,錢黎明,申柏泉,周 毅

(中國電子科技集團公司第58研究所,江蘇 無錫 214035)

1 引言

隨著深亞微米集成電路的出現,單芯片的集成度得到了很大的提高,為了縮短設計周期,加快上市時間,基于IP的SOC設計正在成為IC設計的主流[1]。由于ARM核的方便、易用和易擴展性,目前采用ARM核的SOC產品遍布汽車、消費電子、工業控制、海量存儲、網絡和無線等各類產品市場,可以說ARM技術無處不在。同時為了降低SOC芯片的測試成本和難度,提高芯片的質量和成品率,需要對芯片進行可測性設計,簡稱DFT[2]。其中SOC集成了大量的存儲器,為了確保這些存儲器的好壞,只靠功能驗證碼要花費很大的人力資源,而內建自測試(BIST)可以很方便地完成存儲器的測試。然而殘酷的競爭對成本提出了更加苛刻的要求,因此本文采用A R M核所集成的TA P控制器來控制MBIST,既能完成存儲器的自測試又不會因BIST帶來額外的PAD數量,降低芯片制造和封裝的成本。

2 MBIST設計

由于工藝的不斷進步,存儲器芯片的集成度不斷提高,使得每個存儲器的面積和價格都按指數下降,同時存儲器在制造和使用過程中都易受到干擾[3],故障也越來越復雜。根據故障的成因以及所影響的大小,可將存儲器的故障分成以下幾種[4]:Address Faults(AF)、Address Decoder Open Faults(ADOF)、Coupling Faults(CF)、Data Retention Faults(DRF)、Stuck-at Faults(SAF)、Stuck Open Faults(SOF)和Transition Faults(TF)。為了合理地測試這些故障,主要的測試算法大致有:M a r c h C、CheckerBoard和Rom。本文主要討論SRAM的BIST設計,采用MarchC-(march1)算法,該算法大致的測試步驟如下:

地址(0)→地址(最高位):Write(55)

地址(0)→地址(最高位):Read(55)-Write(AA)

地址(0)→地址(最高位):Read(AA)-Write(55)

地址(最高位)→地址(0):Read(55)-Write(AA)

地址(最高位)→地址(0):Read(AA)-Write(55)

地址(最高位)→地址(0):Read(55)

其中選擇55和AA的原因是因為它們的二進制代碼是互補的,而且01交互,有利于全面覆蓋故障。

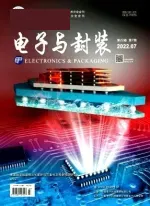

常用的MBIST結構如圖1所示,它包括MBIST控制器和比較器。其中控制器由狀態機控制MBIST的運轉順序;在MBIST測試時控制器還可以產生Memory的地址、數據和讀寫控制信號。Memory的輸出結果輸入到比較器中,由比較器判斷結果正確與否。

圖1 MBIST結構圖

3 ARM JTAG介紹

JTAG是Joint Test Action Group的簡稱。IEEE1149.1標準就是由JTAG這個組織最初提出的,最終由IEEE批準并且標準化。JTAG最初的目的是測試IC之間或PCB之間的連接是否存在故障。后來隨著JTAG的普及和實用性,它的功能不斷得到擴展。目前JTAG還用來調試,因此JTAG成為數字系統可測性設計的重要組成部分。ARM公司也將JTAG內嵌到ARM核中,并且做了擴展,充分發揮了JTAG的作用[5]。

通常來說JTAG主要由邊界掃描寄存器和TAP控制器構成,ARM JTAG包括以下五個端口:

(1)Test Clock Input(TCK)

TCK為TAP操作提供了一個獨立的時鐘端口,TAP的所有操作都是基于該時鐘的。

(2)Test Mode Selection Input(TMS)

TMS用來控制TAP狀態機的轉換,TMS信號在TCK的上升沿有效。

(3)Test Data Input(TDI)

TDI是數據輸入端,所有的輸入數據都是通過TDI一位一位的串行輸入到特定的寄存器中。

(4)Test Data Output(TDO)

TDO是數據輸出端,所有特定寄存器的輸出數據都是通過TDO接口一位一位的串行輸出的。

(5)Test Reset Input(TRST)

TRST可以對TAP控制器進行異步復位。

實際上,通過TAP接口,對特定的數據寄存器進行訪問的一般過程如下:

(1)通過指令寄存器(IR)選定一個需要訪問的數據寄存器(DR);

(2)控制TAP把特定DR連接到TDI和TDO之間;

(3)由TCK驅動,把需要輸入的數據掃入到DR中,同時DR中的數據通過TDO掃出。

另外,ARM7提供了4條掃描鏈:掃描鏈0、掃描鏈1、掃描鏈2和掃描鏈3。為了MBIST的設計,本文對掃描鏈進行了擴展,增加了掃描鏈4和掃描鏈5。

下面先來看看ARM7 JTAG中常用到的幾條指令。

(1)IDCODE:指令二進制代碼是1110。該指令是通過32個TCK周期讀出ARM的ID。

(2)SCAN_N:指令代碼是0010。該指令是將4位掃描鏈所選擇的寄存器連接到TDI和TDO之間。

(3)BYPASS:指令的二進制代碼是1111。該指令將1-Bit長的BYPASS寄存器連接到TDI和TDO之間。

(4)INTEST:指令的二進制代碼是1100。該指令將通過SCAN_N選定的掃描鏈置于內部測試模式。

(5)EXTEST:指令的二進制代碼是0000。指令將通過SCAN_N選定的掃描鏈置于外部測試模式。

4 ARM SOC中的MBIST實現

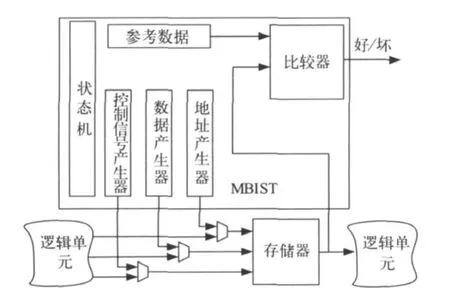

在當今的大規模SOC中,JTAG和MBIST被廣泛采用,如何有效地將兩者結合起來,提高系統的利用率和降低硬件資源的開銷是很關鍵的問題。在SOC芯片中本文采用了圖2所示的結構。

圖2 SOC結構圖

關于圖2,可以從以下幾點闡述:

(1)一個MBIST Engine控制多個SRAM,MBIST產生地址和數據的位寬以最大的SRAM為基準。

(2)MBIST測試SRAM的算法不是固定的,可以通過DFF1配置合適的算法,例如MARCHC。

(3)MBIST的啟動由DFF2控制。

(4)MBIST的結果保存在DFF3中。

(5)DFF1、DFF2和DFF3分別串成一條鏈,與ARM相關的端口連在一起。

(6)在ARM Wrap中增加掃描鏈5和MBIST指令,以便完成MBIST的測試。

因此,在MBIST測試時,先選擇掃描鏈5,讓MBIST中的DFF1、DFF2和DFF3串行連在TDI和TDO之間。通過TDI端口串行掃入MBIST的配置信息,然后再啟動MBIST指令,等待MBIST工作完畢,掃出DFF3中所保存的MBIST結果。

5 仿真結果及分析

通過上述分析,完成相應的代碼設計。為了驗證功能的正確性,編寫測試激勵,且為了書寫方便,在測試激勵文件中定義了一些T A S K,例如Load_Inst、Shiftin_DR、Shiftin_DR_Custom、Shiftout_DR等等[6]。測試激勵中的關鍵部分如下:

Load_Inst(Scan_N);

Shiftin_DR(4,scan_path5);

Load_Inst(Extest);

Shiftin_DR_Custom(20,num);

Load_Inst(MBIST);

……//wait MBIST Finish

Load_Inst(Extest);

Shiftout_DR(20);

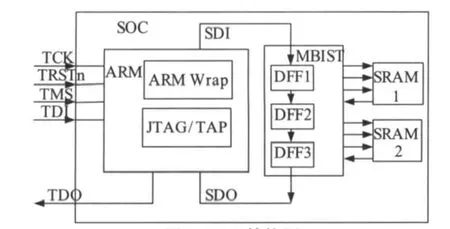

圖3 啟動MBIST

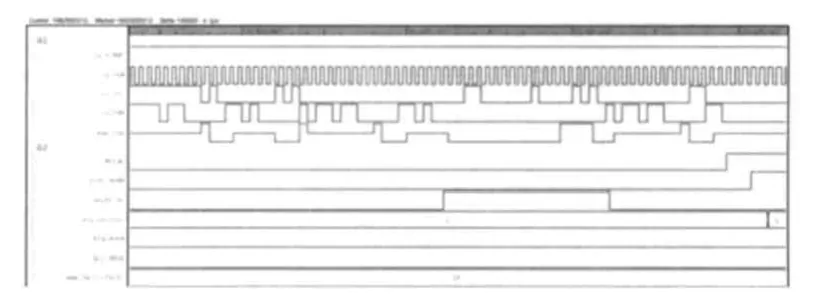

圖4 MBIST運行

圖5 掃出MBIST結果

對圖3~5做如下說明:

(1)在圖3中,通過TDI配置MBIST,可以看到MBIST算法(alg_no[3:0]信號)變成MarchC(用2表示);mbrun和bist_mode置高(有效)。

(2)在圖4中,MBIST正在運行,可以看出Memory的地址、數據和控制信號都在按MarchC算法定義的規律變化。

(3)在圖5中,等MBIST完成后,通過TDO掃出20位的結果,可以發現判斷SRAM出錯的位一直保持為1(0:有故障,1:沒有故障)。

6 結論

總之,隨著大規模集成電路的發展,SOC成為主流。目前在SOC設計中,ARM是經常被采用的核;另外SOC中大量用到存儲器。如何保證存儲器的功能正確,MBIST顯得很有必要。本文通過ARM JTAG來控制MBIST,既達到DFT設計的目的,又降低了普通MBIST所帶來的硬件開銷。

[1]王新安,吉利久.SOC測試中的BIST的若干思考[J].微電子學與計算機,2003.

[2]虞希清. 專用集成電路設計實用教程[M].杭州:浙江大學出版社,2007.

[3]王新安,蔣安平,宋春殫. 數字系統測試[M].北京:電子工業出版社,2007.

[4]MBIST Architect Process Guide[M].Mentor Graphics,2008.

[5]許瓊.基于JTAG的ARM7TDMI調試系統[J].計算機工程,2008.

[6]Writing JTAG Sequences for ARM9 Processors[P]. ARM corp. 2008.