深亞微米工藝下系統芯片低功耗技術

王 棟,蔡 葒

(中國電子科技集團公司第58研究所,江蘇 無錫 214035)

1 引言

隨著集成電路工藝技術迅速發展,單個芯片的規模已經發展到幾十億個晶體管。隨著芯片規模的進一步擴大,功耗問題正在變得日益突出,并成為制約未來集成電路發展的十分關鍵的因素之一。功耗估計及低功耗系統設計工作已經在集成電路工藝制造、設計以及軟件系統設計等層次全面開展。在動態和靜態功耗的建模及優化方面都有大量的研究在進行探索,但其速度還遠遠跟不上以指數形式增長的功耗提高速度,特別是在靜態功耗的快速估計和優化、面向片上系統的低功耗設計技術、面向特定應用的低功耗系統設計等方面。本文從不同的角度對超大規模集成電路存在的低功耗問題進行分析,并提出一些解決措施。

集成電路的功耗一般分為動態功耗和靜態功耗兩大部分。動態功耗是在電路工作狀態發生變化時產生的,主要包括三個部分:由于邏輯跳變引起的電容功耗、由于通路延時引起的競爭冒險功耗、由于電路瞬間導通引起的短路功耗,動態功耗曾經是電路總功耗的主要部分[1]。

靜態功耗是電路處于非活動狀態時電路的功耗。當電路工藝進入深亞微米或者更深的納米階段后,漏電流帶來的靜態功耗占很重要的部分,并且其增長速度比動態功耗快得多。漏電流主要包括三個部分:亞閾漏電流、柵極漏電流、源漏級反偏漏電流[2]。主要原因是柵氧化層厚度按比例減小導致柵氧化層內的電場強度增大,產生較為明顯的柵氧隧穿泄漏電路,加上漏極與襯底之間的反偏PN結電流等,使得泄漏功耗成為總功耗的重要組成部分。一般來說,影響泄漏電流大小的因素包括閾值電壓、溝道的物理尺寸、溝道/表面的注入工藝、漏極/源極的結深度、柵氧化層的厚度和供電電壓等,到納米時代,泄漏功耗占總功耗50%左右[3]。

目前SoC 低功耗設計技術的研究主要集中在兩個方面[4-5]:低功耗電路設計和低功耗EDA 軟件研究。低功耗電路設計的研究和其本身的產品方向有著密切關系,擁有生產線的廠商主要集中在生產工藝方面(如LSI Logic TSMC等),EDA供應商則主要集中在低功耗軟件研究方面(如Synopsys Mentor等),而一些大型處理器設計公司則比較關注SoC各個層次的設計技術和低功耗處理器模型的研究(如ARM、IBM和NEC等),低功耗EDA 軟件的研究主要集中在功耗建模、功耗分析和功耗優化三個方面,國外各大學對低功耗技術的研究比較全面,但每個大學進行的側重點不同,有的側重低功耗處理器的研究,有的側重進行低功耗綜合技術的研究,另外一些則從事異步電路的研究。國內對低功耗技術的研究還處于發展階段,雖然也有一些專門的低功耗研究機構如中科院,但目前開展的一些工作主要集中在工藝研究和功耗建模方面,SoC軟件低功耗設計技術的研究較少,硬件低功耗設計技術也有待進一步完善和提高。

2 低功耗技術的實現

低功耗設計技術貫穿算法/系統級到版圖/電路級的整個設計過程。在設計早期通過有效的分析、驗證和優化技術發現并解決問題,使功耗等技術指標滿足設計規范,然后進入下一階段。

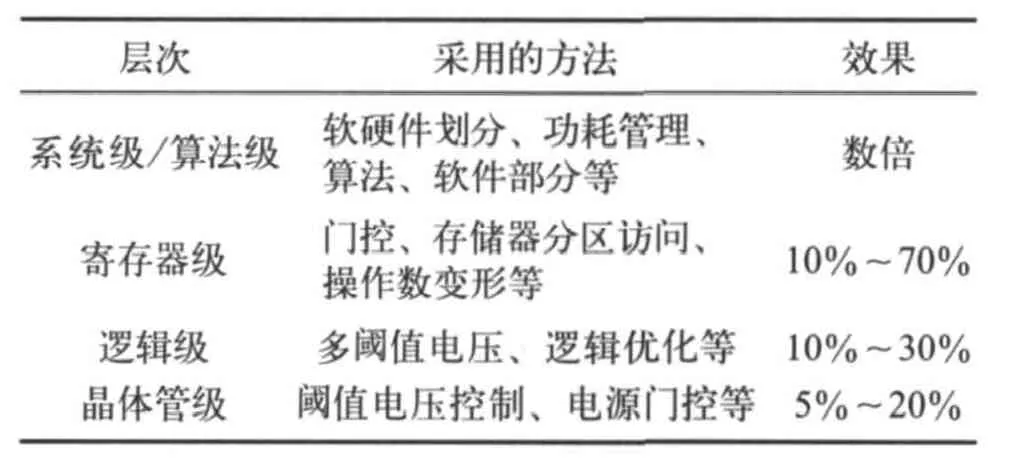

設計證明不同設計層次對功耗的改善程度是不同的,層次越高,改善的程度越大[4]。表1給出在各個不同硬件層次上可采用的低功耗設計技術以及這些低功耗設計技術對降低系統整體功耗的影響。

表1 不同層次低功耗設計技術及其效果

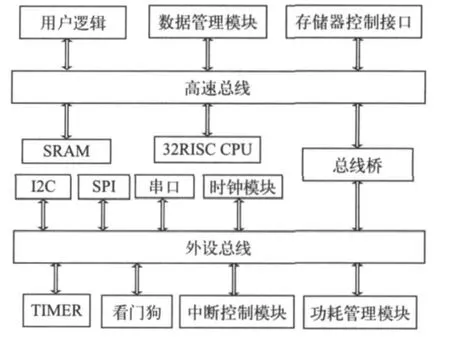

以我們設計的一款系統芯片為例,該系統芯片的架構如圖1所示,其規模超過200萬門,內嵌一個32位微處理器、一些通用的接口模塊、128kB存儲器模塊、中斷模塊、功耗管理模塊以及用戶IP模塊。

圖1 系統芯片架構

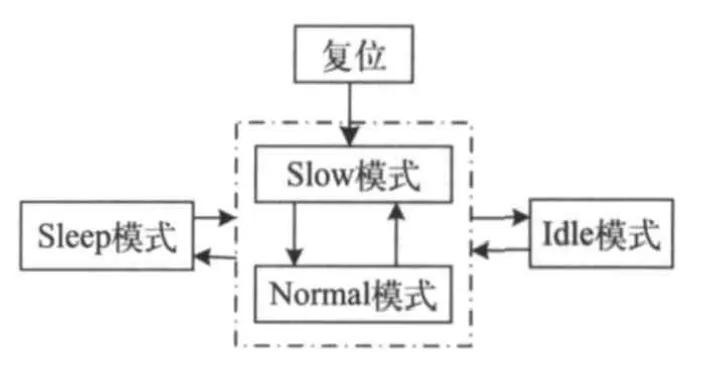

圖2 芯片的工作模式

(1)系統級(system level)基本思想是在部分模塊進入空閑狀態后立即關閉(shut down),主要研究如何進行系統劃分和狀態預測。

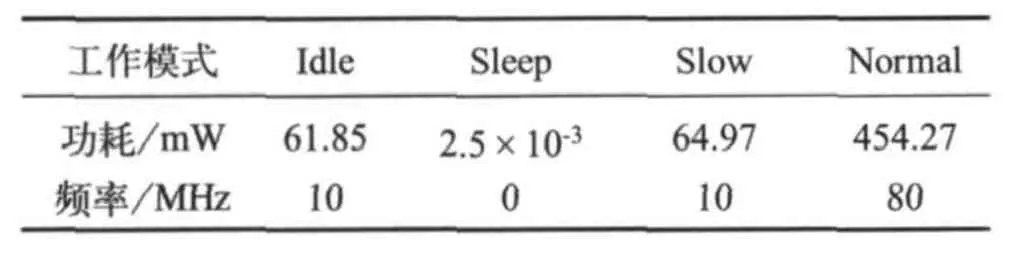

在具體設計中,對芯片工作狀態進行合理的設計,大致分為四種工作模式:Slow模式;Idle模式;Sleep模式和正常(Normal)工作模式。當系統復位完成或系統只需要低頻下工作時(測試模式下),芯片可以在Slow模式;如果處理器結束所有工作,系統將進入很長的等待時間,此時芯片就會進入Idle模式,該模式下,CPU被關閉,所有任務都處于掛起或停止狀態,但大多數的外設仍處于活動狀態,該狀態是外設工作、CPU不工作的低功耗模式。

Sleep模式下將關閉CPU核和所有模塊的時鐘源,僅給重要的內部電路供電,所以功耗最低。雖然可以從Slow模式或Normal模式切換到Sleep模式,但是當它退出Sleep模式時,系統只能回到Slow模式。

Nomal模式下系統中所有模塊的時鐘源都來自于時鐘模塊,該模式下,CPU和所有的外設都處在上電狀態,系統滿負荷運行,功耗最大。當然在這種模式下也可以根據系統的應用要求關閉某些模塊。如果系統需要調整時鐘頻率,可以通過動態配置時鐘電路來實現。

喚醒機制是為了幫助系統從Idle模式或Sleep模式中恢復出來,建立完整、有效的喚醒機制是必須的。有三種方式可以讓系統從低功耗模式中喚醒。第一,通過內部所有模塊的中斷信號,可以讓系統回到進入Idle之前的狀態;第二,內部Watchdog reset信號使系統回到Slow狀態;第三,外部輸入中斷信號可以使系統恢復到低功耗之前的工作狀態。

在進行程序開發時,為配合硬件進行低功耗設計,要充分利用電源管理機制,在電路不同工作模式切換過程中強調應用程序與其配合,減少系統的功耗。芯片上功耗管理模塊具有動態控制整個芯片功耗的功能。仿真顯示各個模式下的功耗如表2所示。

表2 不同模式下的功耗情況

(2)算法級(Algorithm Level)通過選擇適當的算法表述減少跳變率,基本思想還是集中在通過軟、硬件的合理劃分來降低電路功耗[5]。

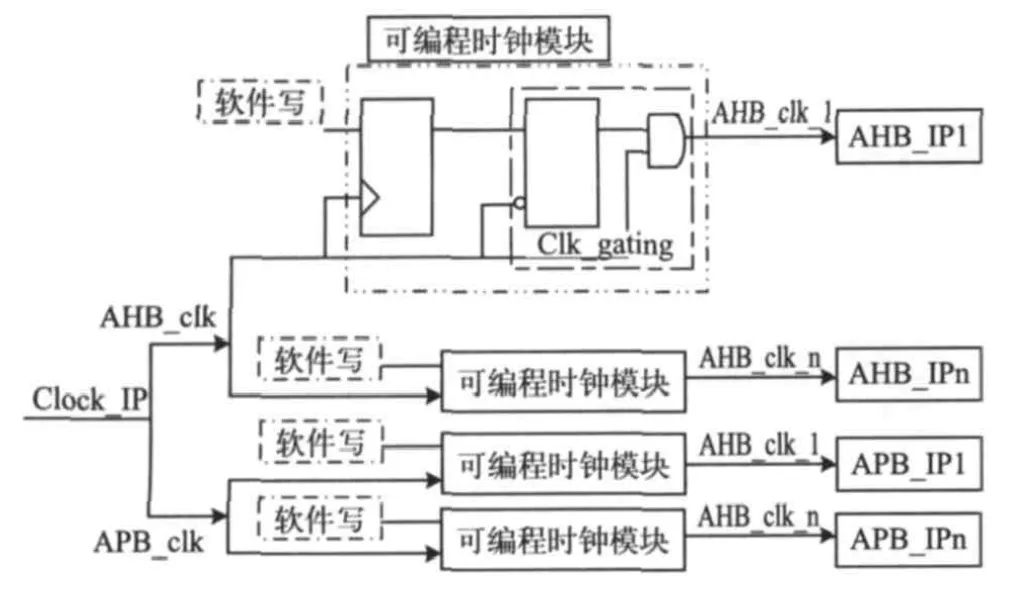

圖3 可編程模塊的控制

SoC工作時對內部IP模塊的要求也不一樣,在不同的時刻IP可以處在不同的工作狀態,這樣可以根據實際工作需要對IP模塊進行合理的管理,控制整個芯片的功耗。為此我們提出圖3 所示的一個時鐘動態管理策略:每個外設時鐘都有一組使能信號進行控制,當某個IP模塊不工作時,用戶可以通過軟件對可編程IP時鐘單元進行編程,當寫入“0”時,該模塊輸入時鐘就會停止工作;當寫入“1”時,該模塊就會重新工作。

(3)寄存器傳輸級(Register Transfer Level)主要有門控時鐘(clocking gating)、有限狀態機編碼優化、通路平衡、總線編碼優化等方法。

門控時鐘可以在設計流程中實現自動化,減少工作量。其中寄存器替換是Synopsys的Power Compiler主要方法,它是將設計中的寄存器替換成帶有門控時鐘“使能”端的寄存器。對下面的一段代碼(a)修改為代碼(b),利用EDA工具在設計的邏輯綜合階段加入門控時鐘綜合腳本,可以綜合出帶有門控時鐘的寄存器。

(a)

Module FFEN(ena,d,clk,q)

input ena, d, clk;

output q;

reg q;

always @(posedge clk )

begin

if(ena)

q <= d;

end

endmodule

(b)

Module G_FFEN(ena, d, clk,q)

input ena,d, clk;

output q;

reg q,g_clk;

always @(posedge g_clk)

begin

q<=d;

end

always @(clk or ena)

begin

if(!clk)

I_ena <= ena;

end

assign g_clk = I_ena &clk;

endmodule

利用綜合工具Design Compiler,將實現在電路插入門控時鐘,通過腳本靈活實現:

/*設置門控時鐘設計常用的變量*/

Set power_preserve_rtl_hier_names true

Set hdlin_no_group_register true

/*設定門控時鐘類型及相關參數*/

Set_clock_gating_style –sequential_cell latch –setup 0.2 –hold 0.1 –control_point before –control_signal scan_enable –minimum_bitwidth 2 –max_fanout 6

/*讀入RTL代碼,插入門控時鐘*/

Analyze –fanout verilog –lib library_name –define SYNOPSIS

/*確定控制信號是否采用門控時鐘*/

Set_clock_gating_signals –design design_name

Elaborate design_name –gate_clock –update –lib liabrary_name

/*將所涉及到的控制點信號連接到一起*/

Hookup_testports -verbose

/*插入門控時鐘的報告*/

Report_clock_gating –gating_elements –gated –ungated –hier

/*插入門控時鐘后的時鐘定義與約束*/

Set CLK_PER 10

Set UNCERTAINTY 0.12

Set INSERTION_DELAY 0.2

Create_clock –period $ CLK_PER –name CLK[get_ports clk_power]

Create_clock –period $ CLK_PER –name POST_CG_CLK [get_pins –hierarchical “*clk_gate”/ENCLK]

Create_clock –period $ CLK_PER –name PRE_CG_CLK [get_pins –hierarchical “*clk_gate”/CLK]

Set_clock_latency $INSERTION_DELAY [get_clocks{CLK POST_CG_CLK}]

Source –e –v top_constraints.tcl

Propagate_constrains –gate_clock

Uniquify compile

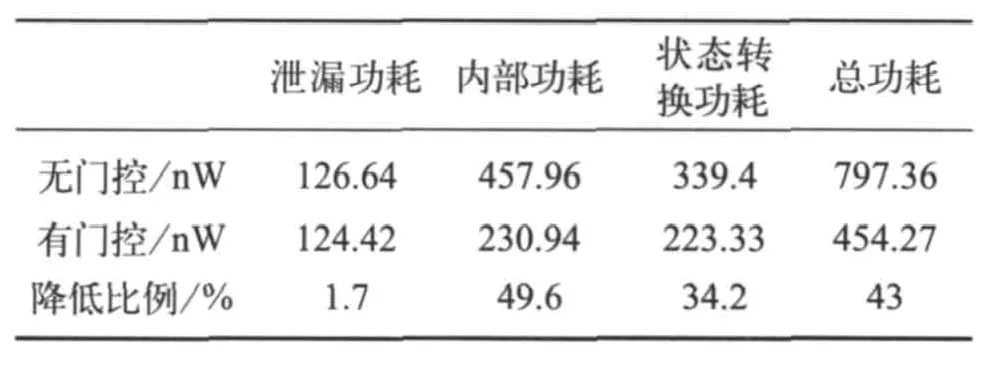

采用SMIC 0.18μm CMOS工藝,目標工作頻率100MHz。物理設計完成后最終的功耗分析結果見表3。分析結果表明,在不改變RTL代碼的情況下,有效使用EDA工具進行門控時鐘的插入可以使得電路功耗明顯降低。

表3 由Power Compiler產生的功耗報告

3 結論

本文分析深亞微米工藝下系統芯片功耗的組成,并以實際設計的芯片為例,分別從不同層次(系統級/算法、寄存器級以及邏輯門級)采取低功耗優化方法進行設計,給出實際設計結果,這些方法的綜合應用可以顯著地降低芯片的功耗,同時也驗證了功耗設計策略。

[1]Benini L,Bogliolo A,Micheli G,D. A survey of design techniques for system-level dynamic power management[J].IEEE Transactions on VLSI Systems, 2000,8(3):299-31.

[2]Xu,Y.,et al. Minimum leakage pattern generation using stack effect[C]. ASIC, 2003, Proceedings. 5th International Conference. 2003.

[3]Abdollahi, A.,F.Fallah, M.Pedram. Leakage current reduction in CMOS VLSI circuits by input vector control[J].VLSI Systems. IEEE Transactions,2004,12(2):140-154.

[4]Anand R, Niraj K J, Sujit D. High-level power analysis and optimization[M]. Boston, Kluwer Academic Publishers,2004.11-73.

[5]Lekatsas H, Henkel J,Wolf W. Arithmetic Coding for Low Power Embedded System Design[A]. Data Compression Conference (DCC’00),Snowbird, Utah,2000.430-439.