視頻圖像實時采集和顯示系統的FPGA設計

李興富

LI Xing-fu

(桂林航天工業高等專科學校,桂林 541004)

0 引言

視頻信息采集為視頻圖像處理、傳輸、顯示等提供提供原始的數字圖像數據,視頻采集系統的性能是影響視頻圖像系統性能的關鍵因素之一[1]。隨著人們對視頻圖像質量的要求越來越高,對視頻采集系統的性能要求也將越來越高[2]。目前視頻采集系統常用的處理器包括通用處理器、DSP和FPGA。盡管通用處理器能夠處理許多任務,但是它們通常缺少執行復雜數據處理任務所需要的帶寬,常因速度不夠快而不能滿足設計目標[3];DSP雖然內部利用專用硬件實現數字信號處理中的常用算法,運算速度很快,但其采用單指令執行系統,并且僅對某些固定的運算可以優化,因此靈活性不夠; FPGA作為當今主流的大規模可編程集成電路,采用硬連線邏輯實現數據處理和運算,具有集成度高、速度快、性能穩定、開發周期短、便于改進升級等一系列優點,還能實現視頻采集、圖像顯示的外圍邏輯控制,在視頻采集和圖像處理方面具有獨特優勢。使用FPGA實現該類任務已成為很好的選擇[4]。

本文采用FPGA作為視頻圖像實時采集和顯示系統的核心控制器。首先對視頻圖像采集顯示系統的構成、工作原理及技術現狀做了簡單介紹,然后敘述了各功能模塊和接口電路的設計方法和過程,重點介紹了FPGA應用系統設計中一些難點問題的解決辦法。

1 系統的總體結構及器件選擇

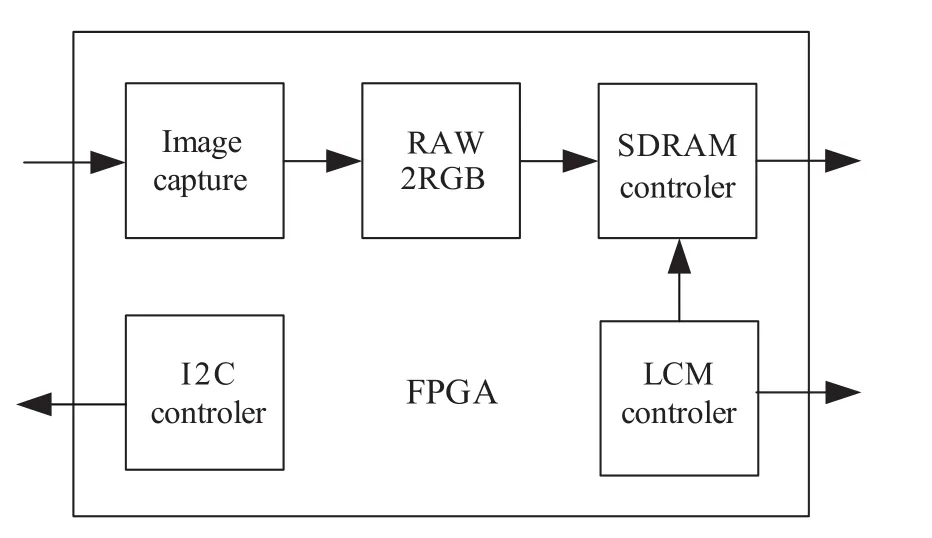

系統硬件框圖如圖1所示。其中,CMOS sensor為圖像傳感器,型號為MT9M111,用于實時接收視頻信號;LCD的型號為TD036THEA3,用于實時顯示視頻圖像; SDRAM采用ISSI公司的IS42S16400B,用于緩存視頻數據;FPGA采用CycloneII EP2C35F672C8 ,作為整個系統的控制核心。

圖1 系統總體結構框圖

MT9M111是美光公司推出的集成CMOS傳感器和圖形處理器的SOC產品;130萬像素分辨率(1280H×1024V),可以支持SXGA格式輸出;嵌入的可編程圖像處理器提供的功能包括色彩恢復和修補、自動曝光、白平衡、鏡頭陰影修正、增加清晰度、可編程灰度修正、黑暗電平失調修正、閃爍避免、連續調整濾光尺寸、平滑的數字變焦、快速自動曝光模式和不工作時缺陷修正等,可以通過兩線串行接口對其進行配置。

EP2C35F672C8為Altera公司CycloneII系列FPGA芯片,在性能、功耗和性價比方面超越了第一代Cyclone系列。可以內嵌各種IP核,實現強大的控制處理功能;內嵌M4K存儲器塊,用于實現單端口RAM、雙端口RAM、ROM以及同步FIFO和異步FIFO; 除了支持LVTTL、LVCMOS、SSTL等標準的單端I/O外,還支持LVDS、RSDS、mini-LVDS、LVPECL等標準的差分信號;支持四個可編程鎖相環(PLL)和最多16個全局時鐘線,還有對時鐘管理和頻率合成的能力。價格也比較適中,所以很適合作為大批量產品的解決方案。是視頻處理低成本解決方案的理想選擇。

IS42S16400B是ISSI公司的SDRAM產品。包含67,108,864bits,可配置為具有同步接口的四塊DRAM。該SDRAM包括自動刷新模式、省電模式和掉電模式。所有信號在時鐘信號上升沿保存。所有輸入和輸出與LVTTL兼容。內部塊之間交錯隱藏預充電時間,支持同步猝發數據傳輸方式。

TD036THEA3為3.6寸有源矩陣彩色TFT液晶顯示模塊,采用低溫多晶矽硅TFT技術,分辨率為320×240,數據格式為RGB565,具體顯示為QVGA模式,輸出像素時鐘為19.28MHz。

2 系統的FPGA設計

系統的FPGA設計模塊圖如圖2所示。I2C controler模塊用于通過I2C總線協議控制MT9M111的寄存器配置,使攝像頭按照配置的模式工作,輸出行場同步信號、像素時鐘、圖像數據。 Image Capture模塊檢測行場同步信號、生成寫使能信號,在像素時鐘的上升沿將視頻數據采集到寄存器中。RAW2RGB模塊將采集的數據轉換成RGB信號,SDRAM controler模塊用于控制數據的緩沖,將數據寫入SDRAM。LCM Controller模塊產生LCD控制信號,將SDRAM中的數據送到LCD上,這樣就完成了視頻圖像的實時采集與顯示。

設計中采用VerilogHDL進行編程,可以在抽象層對電路進行描述,而不必考慮特定的制造工藝,通過使用Altera公司QuartusII軟件的邏輯綜合工具能夠將設計自動轉換為任意一種制造工藝版圖。

圖2 FPGA模塊圖

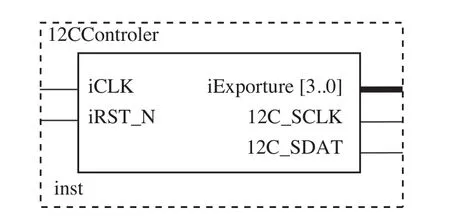

2.1 I2C controler模塊設計

I2C controller模塊是通過編寫Verilog代碼自定義邏輯實現的。模塊圖如圖3所示。

圖3 I2C controller模塊

在該模塊中,由于需要把I2C總線接口的SCL和SDA信號在系統時鐘下同步,因此采用系統時鐘iCLK對SCL和SDA信號進行三次緩沖,得到其上升沿和下降沿脈沖信號,便于狀態機處理;狀態機對I2C的讀/寫寄存器操作進行說明,狀態包括器件地址部分、寄存器地址部分和數據部分。

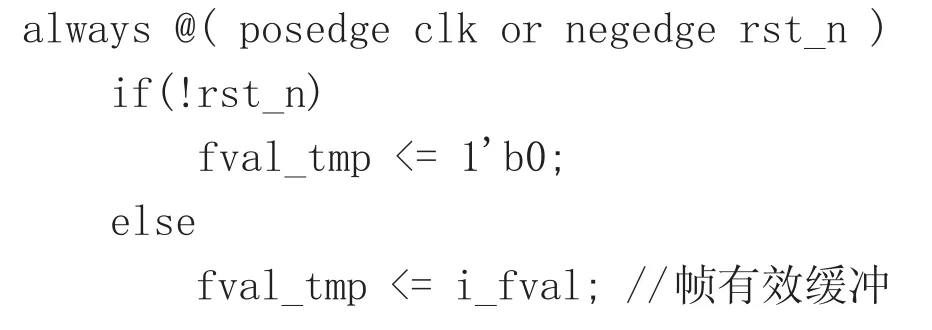

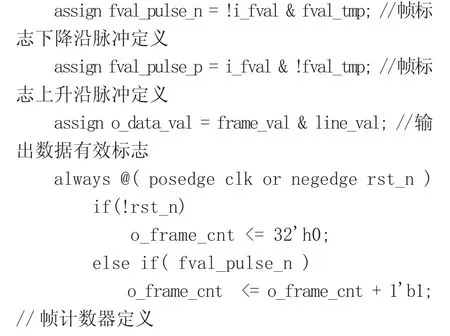

2.2 圖像數據采集模塊設計

在程序設計過程中,首先需要檢測視頻圖像中幀標志的有效起始和結束,在判斷到幀標志有效后,需要繼續檢測視頻圖像中行的有效起始和結束標志,在判斷到行標志有效后,在像素時鐘上升沿把圖像的有效像素值存入存儲器;同時,在幀標志的上升沿后,列計數器x_cnt清0,在行標志有效期間,對列計數器進行計數,記滿1280為一行數據,行計數器加1;最后,輸出數據的有效使能信號,供下一級圖像格式轉換模塊使用。

部分源代碼如下:

2.3 圖像格式轉換模塊設計

由于在MT9M111圖像傳感器的配置中,采用原始的Bayer輸出格式,使得其每次只產生一種顏色分量的響應值,而FPGA后續設計需要4∶4∶4的RGB顏色,因此需要對顏色分量進行處理。

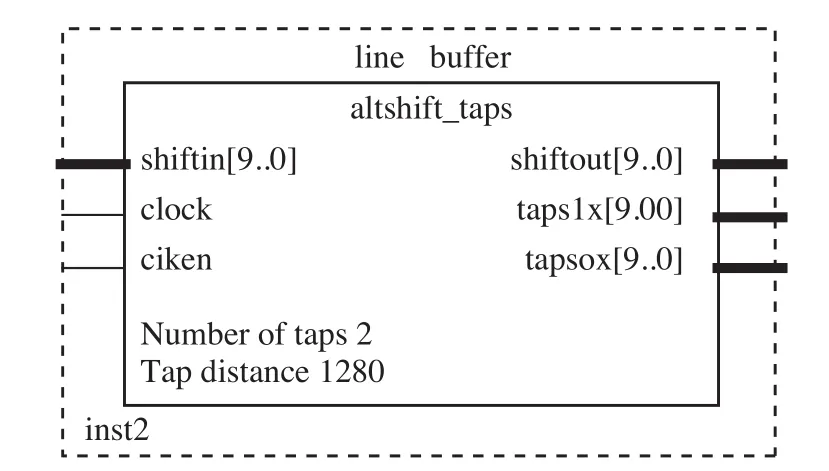

本模塊設計需要大量的移位寄存器,如果全部采用FPGA內部的觸發器串聯構成的話,需要2560個10bit的觸發器,會導致LE中的觸發器資源緊張,可能會出現最終邏輯資源不夠用的情況。在Altera FPGA中,內嵌的M512和M4K專用IP存儲模塊,可以被用來支持移位寄存器模式,不僅可以節省觸發器資源,同時也減少了布線資源。通過調用Altera的IP核生成器產生移位寄存器,數據寬度為10bits,抽頭數(Taps)為2,如圖4所示。

圖4 調用IP核生成移位寄存器

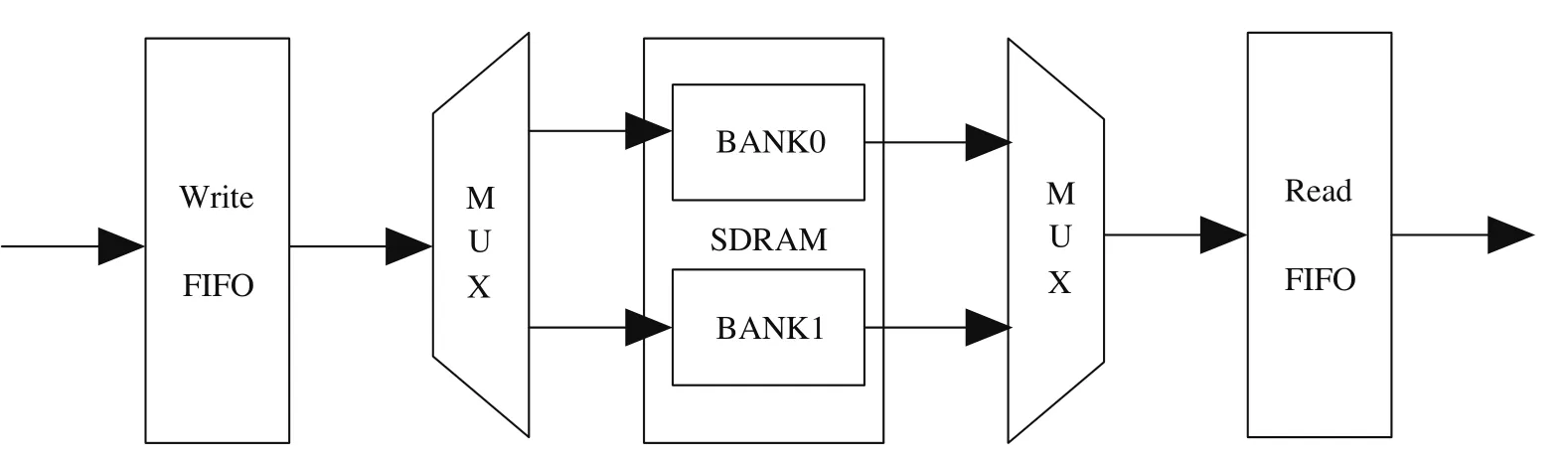

圖5 存儲器乒乓操作原理圖

2.4 圖像數據緩存控制模塊設計

由 于MT9M111工作時鐘為25MHZ,因此圖像數據的接收、格式轉換是在25MHZ時鐘頻率下進行的。而FPGA板上輸入時鐘頻率為50MHZ,因此會產生異步時鐘域問題。設計中采用異步FIFO進行數據緩沖。同理,由于液晶屏輸出像素時鐘頻率為19.28MHZ,SDRAM控制器使用的時鐘為輸入時鐘經過FPGA內部的PLL兩倍頻后的100MHZ,因此在SDRAM控制器與液晶屏顯示控制模塊之間也通過異步FIFO進行數據緩沖。

為了滿足視頻圖像實時采集和顯示的需要,視頻數據的接收和顯示需同時進行。而SDRAM作為單端口器件,不能同時進行數據的寫入和讀出。要實現同時讀寫,必須采用乒乓操作來完成,原理如圖5所示。具體方法是通過設計SDRAM控制器接口和FIFO緩沖接口,輪流對一片SDRAM中的兩塊BANK進行操作,當傳感器發送數據至SDRAM時,寫入BANK0,此時顯示控制可以從BANK1取數據,并且傳感器發送一幀數據的時間與顯示器取出一幀數據的時間相同;當傳感器繼續發送數據時,寫入BANK1,同時顯示控制可以從BANK0取數據,如此不斷循環。這樣就可以有效地利用和節省存儲器資源,并實現視頻圖像的實時采集和顯示。

2.5 顯示控制模塊設計

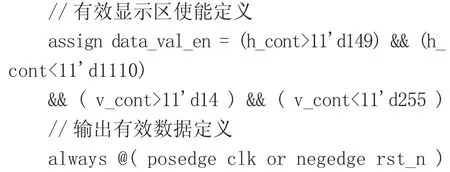

顯示控制模塊LCM Controller用于按照TD036THEA3液晶屏的時序要求,產生輸出幀和行控制信號,通過讀取FIFO中的數據,輸出RGB數據,完成液晶屏的顯示控制。其時鐘頻率為19.28MHZ,是通過對系統時鐘分頻得到的。

部分實現代碼如下:

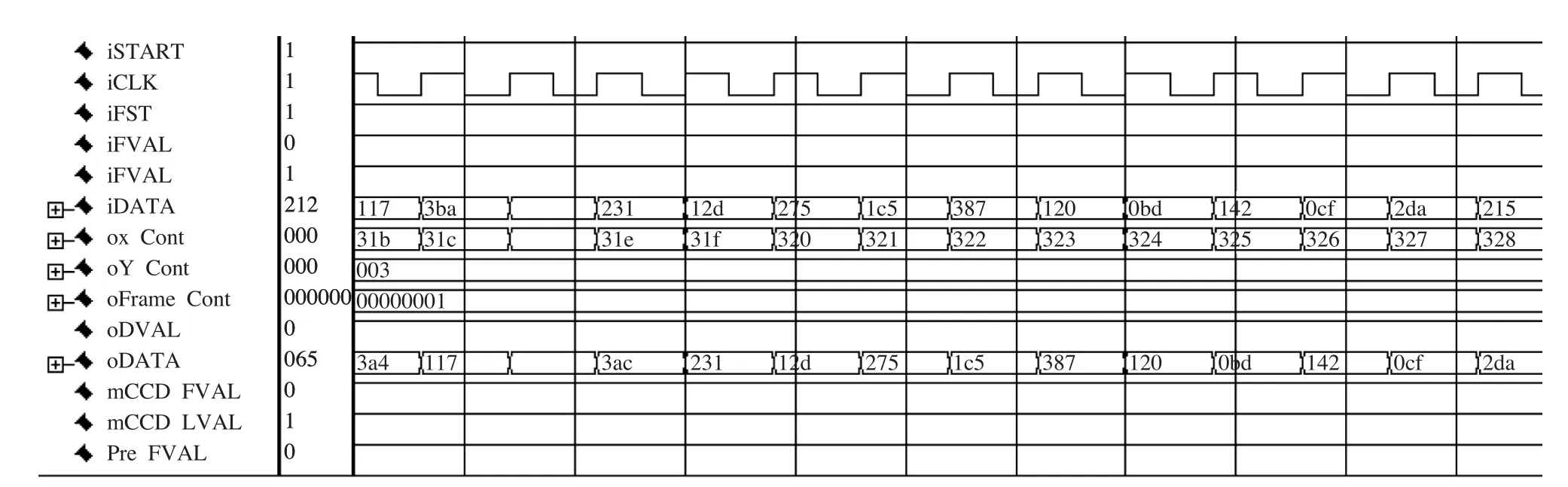

圖6 Image capture模塊仿真測試時序圖

3 系統的測試

通過編寫測試代碼,采用Modelsim仿真工具對整個FPGA中的各個模塊進行仿真測試。圖6為Image capture模塊的仿真測試時序圖,其他模塊的仿真測試方法類似,不再贅述。

Image capture模塊是系統中的關鍵部分,它根據MT9M111圖像傳感器輸入的行有效信號、幀有效信號,采集像素數據,提供給后續模塊進行格式轉換、顯示輸出等。

如圖中所示,輸入時鐘頻率為25MHZ,在系統復位為高的情況下,當幀有效標志和行有效標志均為高時,對輸入數據進行采樣,同時x_cont計數器不斷加一;當一行結束的時候,y_cont計數器加1,完成有效圖像數據的采樣。

通過對整個系統的實際測試,在50MHZ頻率下,達到的指標如下:實時性:25幀/秒;最大功耗:3.5W。連續采集和顯示視頻圖像的質量和穩定性也很高。

4 結論

本文介紹了一種采用FPGA作為核心控制器同時實現外圍部件接口控制邏輯的視頻圖像實時采集和顯示系統實例。敘述了各功能模塊和接口電路的設計方法、測試方法。給出了異步時鐘處理、調用IP核生成移位寄存器、SDRAM存儲器乒乓式操作等FPGA應用設計中的一些難點問題的處理方法。通過仿真測試和實際驗證,該系統在快速性、穩定性及體積、功耗、成本等方面均具有較優越的性能。表明,利用FPGA進行視頻圖像信息采集和顯示系統設計,是降低產品體積、功耗,提高快速性、穩定性的有效途徑。

[1]肖文才, 樊豐.視頻實時采集系統的FPGA設計[J].中國有線電視, 2006(2l)∶ 2104-2108.

[2]韓相軍, 關永, 王萬森.嵌入式視頻采集系統的設計與實現[J].微計算機信息, 2006, 22(1-2)∶ 26-28.

[3]Chris Roven.IP重用和嵌入式SOC開發的邏輯方法[J].電子產品世界, 2005(8)∶ 115-116.

[4]陳朗, 王瑞.MPEG-4系統中基于FPGA實現數據采集及預處理[J].微計算機信息, 2005, 2l(9-3)∶ 109-111.

[5]科夫曼.基于Verilog語言的實用FPGA設計[M].北京∶ 科學出版社, 2000.

[6]孫愷, 程世恒.NiosⅡ系統開發設計與應用實例[M].北京∶ 北京航空航天大學出版社, 2007.

[7]高韜, 趙建濤.視頻壓縮理論及其技術發展.電子技術應用[J], 2007 (11)∶ 3-6.

[8]尹德安, 李欣.基于FPGA的視頻采集控制設計[J].微計算機信息, 2006, 22(9-2)∶ 159-160.