高精度回波飛行時間測量方法及實現

張金,王伯雄,崔園園,柳建楠,張力新

(1.清華大學 精密測試技術及儀器國家重點實驗室,北京100084;2.炮兵學院 電子工程教研室,安徽 合肥230031;3.唐山匯中儀表有限公司,河北 唐山063000)

0 引言

飛行時間是指信號或者物體從發射端通過介質到達接收端所經歷的時間間隔長度,高精度的時間間隔測量在脈沖激光測距、精密聲學定位、高能物理等現代軍事、航空航天及科學實驗領域有著廣泛應用[1-2]。脈沖計數法具有測量范圍大、線性好等優點,是高分辨測時最簡單、最有效的方法,但是測時分辨率較低[3]。模擬內插法理論上可以實現高分辨率,但測量過程耗時較長,易受干擾噪聲、溫度和非線性的影響[3]。Bowman[4]等設計了一種類似于千分尺微差測量原理的測時系統,測時分辨率能夠達到50 ps.但該算法獲得兩個高穩定度的脈沖對相當困難。延遲內插技術利用電子器件單元固定的延時作為標尺來實現對飛行時間的測量。Szplet[6]等基于0.65 μm 的CMOS 工藝在現場可編程邏輯門陣例(FPGA)的內部,構建差分延遲線,得到了LSB為100~200 ps 的測時系統。Zielinski[7]等采用Xilinx 公司Virtex 系列FPGA 芯片XCV300 實現的抽頭延遲線,最小分辨率為100 ps.延遲線法可以實現對微小時間間隔的測量,適用于連續測量,缺點是隨著測量分辨率的提高,要求延遲線長度越來越短,當測量較大時間間隔時,延遲線數量將大大增加[8]。多相采樣技術利用n 路同頻率,相位均勻分布的時鐘信號作為計數時鐘,能夠將測量分辨率提高到參考時鐘Tclk的1/n,但該方法在FPGA 中實現較高倍頻時會導致相移分辨率的降低,高精度測量較困難[2]。

針對以上幾種方法的優缺點,本文提出了一種將脈沖計數法、相位延遲內插技術相結合的回波飛行時間測量方法,并在Xilinx Virtex 5 平臺上實現了以該方法為核心的飛行時間測量系統,具有動態測量范圍大,測量過程耗時短,測時精度較高等優點。

1 飛行時間測量原理

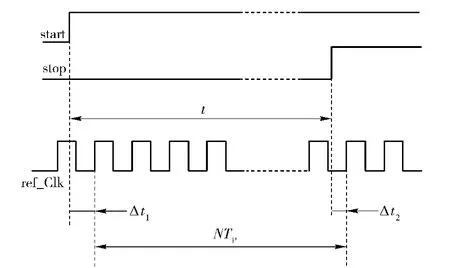

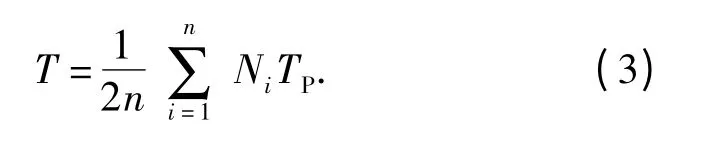

工程上為實現飛行時間測量,通常將其轉換成兩個脈沖信號邊沿之間的時間間隔來完成,其測量原理[8]如圖1所示。被測時間由3 個部分組成,1)脈沖計數法得到的參考時鐘整數倍部分NTP,2)Start 信號上升沿與緊接著的參考時鐘上升沿之間的時間間隔Δt1,3)Stop 信號上升沿與緊接著的參考時鐘上升沿之間的時間間隔Δt2,設被測時間為t,有:

式中:TP為參考時鐘周期;t 為精確的待測回波飛行時間;NTP為脈沖計數法實際測得的飛行時間。Δt2-Δt1為計數量化誤差。

為提高時間測量精度,首先需要盡可能提高參考時鐘頻率,減小計數量化誤差TP;其次是采取用一定的時間插值算法精確測量非整數部分Δt1和Δt2的大小。

圖1 回波飛行時間測量原理示意圖Fig.1 Schematic diagram of echo time of flight measurement

2 基于FPGA 的高精度飛行時間測量

2.1 總體設計思路

基于FPGA 的高精度回波飛行時間測量系統以脈沖計數法為基礎,通過相位延遲技術實現時間插值,提高時間測量精度,系統總體框圖如圖2所示。

圖2 基于FPGA 的高精度飛行時間測量系統框圖Fig.2 System block diagram of high precision time of flight measurement based on FPGA

脈沖計數法量化誤差TP取決于系統能提供的參考時鐘頻率,通過提高計數器時鐘頻率能直接提高測量精度。充分利用Xilinx FPGA 時鐘資源,借助數字時鐘管理/鎖相環技術(DCM/PLL)將33 MHz外時鐘轉換成594 MHz 的高頻、高穩定度、低抖動時鐘,作為時間測量基準參考時鐘,使得計數量化誤差減小到1.683 5 ns.但是要想實現百ps 級的分辨率,其計數頻率要高達GHz,信號進入微波段,不僅難以產生,準確性也無法保證,而且由于分布參數效應,GHz 的高頻計數器在普通電路中不易實現。為此設計雙邊沿計數器,能夠在不提高時鐘頻率的情況下將測時精度減小到計數量化誤差的一半TP/2.

單一的脈沖計數法無論采取何種措施,計數量化誤差總是存在。引入延遲單元對參考時鐘周期做相位內插,得到n 路同頻不同相的參考時鐘分別驅動雙邊沿計數器,對含相位關系的n 路計數器輸出進行數據處理,能夠進一步提高測時精度。

2.2 雙邊沿可控計數器設計

傳統計數器僅對時鐘信號的上升沿或下降沿敏感,表現為單邊沿觸發計數。對于上升沿觸發的同步計數器而言,當時鐘信號clk=1 時,計數器處于計數狀態;當clk=0 時,計數器處于保持狀態,而下降沿觸發同步計數器情況剛好相反。如果將單邊沿觸發的計數器分別設計成上升沿觸發的偶數計數器和下降沿觸發的奇數計數器,并把兩個計數器并聯,則兩個計數器在時鐘clk 的作用下交替處于計數狀態和保持狀態。最后,將奇、偶計數器的輸出端連接至數據選擇器,用clk 作為選通控制信號。這樣,當clk=0 時,奇計數器處于計數狀態,偶計數器處于保持狀態,數據選擇器輸出偶計數器數據;當clk=1時,偶計數器處于計數狀態,奇計數器處于保持狀態,數據選擇器輸出奇計數器數據。于是,在clk 的控制下,輸出端得到完整的計數數據。這種并聯結構的計數器在clk=0、1 時都能實現計數,計數器的狀態在時鐘脈沖的上升沿和下降沿均可以改變,從而實現了雙邊沿觸發計數器的功能[9]。

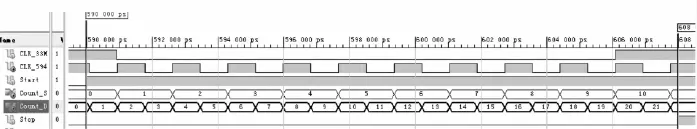

根據上述雙邊觸發計數器的設計思想,在Xilinx 公司的FPGA 器件XC5VLX110T 上進行了硬件實現。仿真與硬件驗證結果表明,設計的雙邊沿觸發計數器具有正確的邏輯功能和實用價值。圖3是單邊沿觸發同步計數器與雙邊沿觸發同步計數器的仿真波形,圖中CLK_33M 為33 MHz 時鐘、CLK_594為經鎖相、倍頻、去抖動之后的高頻時鐘,Start、Stop分別為待測飛行時間的起始和終止信號,Count_S、Count_D 分別表示單邊沿計數器與雙邊沿計數器的輸出。

由圖3可見,在相同時鐘頻率條件下,雙邊沿觸發計數器將計數量化誤差減小了一半。在594 MHz參考時鐘頻率下,理論測時精度達到842 ps.

圖3 單邊沿計數器與雙邊沿計數器時序仿真圖Fig3 Time sequence simulation diagram of single edge counter and double edge counter

2.3 相位延遲內插技術

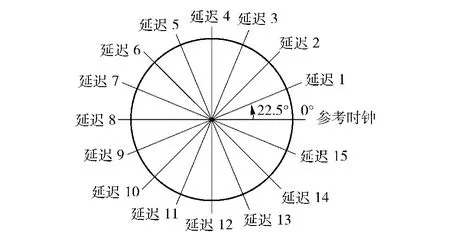

相位延遲內插技術就是利用一組由延遲單元構成的延遲鏈,將參考時鐘作為基準時鐘順序延遲n-1 次,得到規律性相位順延的n 個參考時鐘集{Clk_Refi|1≤i <n},n 次延遲之后,參考頻率信號剛好延遲了一個周期。于是n-1 延遲后形成的n-1 個參考頻率信號和原來基準頻率信號形成了在一個周期內的均勻移相信號。由此可見為了滿足均勻移相的要求,延遲單元的延遲時間τ要求滿足

圖4所示為參考時鐘信號延遲16 次時的相位分布圖。

(2)式是對n 個延遲單元延遲時間一致性的約束,使得每一路計數器的輸出均含有參考時鐘的相位信息,是減少測量誤差的關鍵。

采用n 個雙邊沿計數器在相同計數控制信號(Start/Stop)作用下對參考時鐘集{Clk_Refi|1≤i <n}分別計數,得到n 個計數值Ni,以其算術平均值作為參考頻率計數值。測得飛行時間為

圖4 參考時鐘信號延遲16 次時的相位分布Fig.4 Phase distribution of reference clock for sixteen delay

設Δt2i,Δt1i是服從在[0,Tp)上均勻分布的隨機變量,由此可得測量誤差為

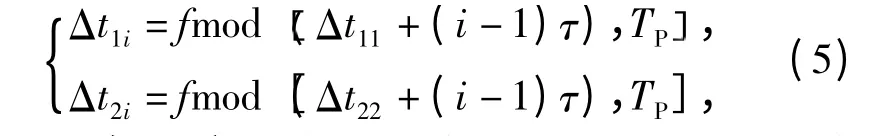

式中,Δτi為第i-1 延遲參考頻率的量化誤差,設已知Δt21,Δt11,由(2)式可得

式中,fmod(x,y)是實數求余運算,返回x/y 的余數。x,y 和返回值均為零或正實數。

將Δt1i(i=1,…,n)按從小到大順序排列,這n個數構成公差為τ 的等差數列,數列的第1 項記為Δt11一定滿足0≤Δt11<τ,于是

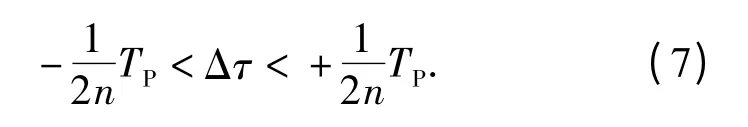

將(5)式和(6)式代入(4)式,可以求得雙邊沿脈沖計數與相位延遲內插相結合的測時方法測量誤差為

值得提出的是,雙邊沿脈沖計數與相位延遲內插相結合的測時方法雖然將n 次測量的計數值進行平均,但并不等同于一般的計數平均法。計數平均法連續或隨機取n 個計數值后平均,因為n 次計數過程沒有任何相關性,所以計算得到的飛行時間值不會有任何測量精度上的提高。

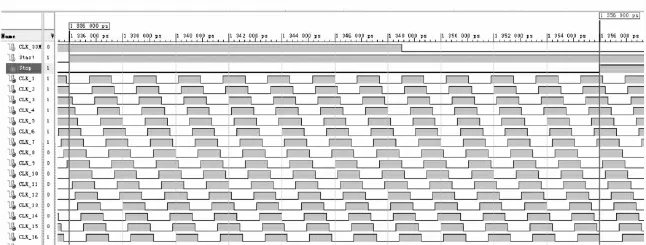

Xilinx 公司FPGA 器件XC5VLX110T 為相位延遲內插技術的實現提供了豐富的DCM 和PLL 資源,對前文得到的594 MHz 參考時鐘進行16 次相位內插,即可得到一組參考時鐘集{Clk_Refi|1≤i <16},在Start/Stop 信號上升沿控制下同時驅動雙邊沿計數器計數,由(3)式即得到待測飛行時間。

16 路相位延遲內插時序仿真結果如圖5所示。圖中CLK_33M、Start、Stop 信號含義與圖4所示相同。本設計16 路相位延遲內插技術理論測時精度達到TP/32=53 ps.

圖5 16 路相位延遲內插時序仿真圖Fig.5 Time sequence simulation diagram of sixteen phase delay interpolation

3 測試實驗及分析

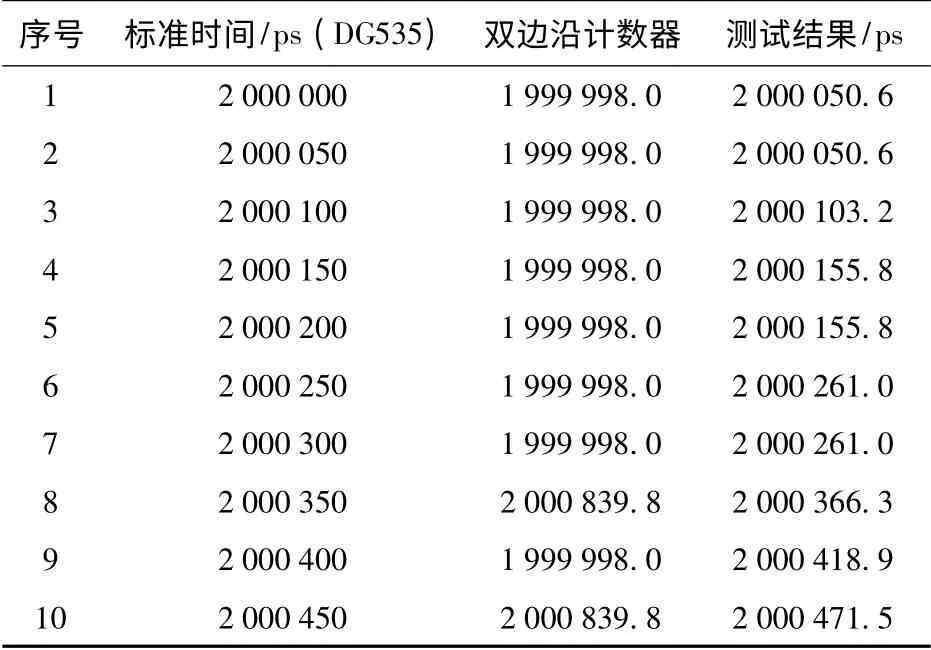

以脈沖計數與相位延遲內插相結合的高精度回波飛行時間測量方法為核心,在Xilinx 公司XC5VLX110T 器件上實現了回波飛行時間測量系統。33 MHz 外時鐘條件下,以高精度數字時間調整器DG535(時間分辨率5 ps)提供標準時間間隔,進行了測試實驗,實驗數據摘錄如表1所示。

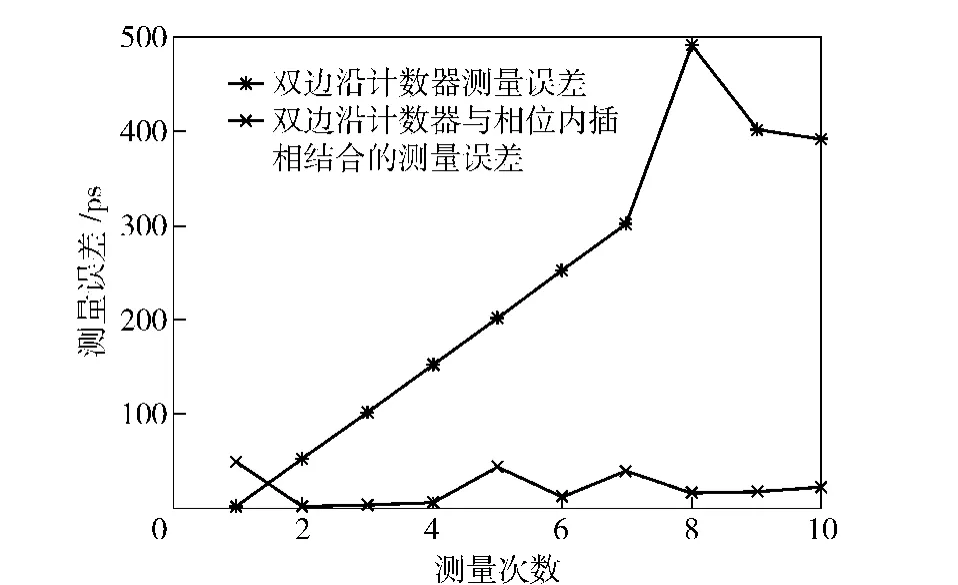

實驗結果誤差分布如圖6所示,設計的雙邊沿計數器能夠準確記錄待測時間間隔內高頻脈沖數,脈沖計數法在33 MHz 時鐘條件下,能夠實現優于842 ps 的時間測量精度,被測飛行時間值越靠近計數周期Tp整數倍時測量誤差越小。16 路相位延遲內插配合雙邊沿脈沖計數器能夠實現優于55 ps 精度的時間測量。

4 結論

本文提出并實現了一種基于雙邊沿計數器的脈沖計數與相位延遲內插相結合的高精度飛行時間測量方法,測量精度優于55 ps.提高參考時鐘頻率(1/TP)以及相位延遲內插數n 均可進一步提高測量精度。

與傳統飛行時間測量方法相比,該方法易于在FPGA 中實現,擴展靈活,集成度高,穩定性好,能夠有效克服溫度、頻率穩定度等隨機噪聲的干擾。可廣泛應用于脈沖激光或雷達測距、精密定位、導航等需要高精度測量時間間隔的領域。

表1 高精度飛行時間測量系統實驗測試數據摘錄Tab.1 Test data extract for high precision time of flight measurement system experiment

圖6 測量結果誤差分布Fig.6 Measurement error distribution of test result

References)

[1] 董明榮,許學忠,張彤,等.空中炸點三基陣聲學定位技術研究[J].兵工學報,2010,31(3):343-349.DONG Ming-rong,XU Xue-zhong,ZHANG Tong,et al.Research on three-array acoustic localization technology for the aerial blast points[J].Acta Armamentarii,2010,31(3):343-349.(in Chinses)

[2] 宋建輝,袁峰,丁振良.脈沖激光測距中高精度時間間隔的測量[J].光學精密工程,2009,17(5):1046-1050.SONG Jian-hui,YUAN Feng,DING Zhen-liang.High precision time interval measurement in pulsed laser ranging[J].Optics and Precision Engineering,2009,17(5):1046-1050.(in Chinses)

[3] 孫杰,潘繼飛.高精度時間間隔測量方法綜述[J].計算機測量與控制,2007,15(2):145-148.SUN Jie,PAN Ji-fei.Methods of high precision time-interval measurement[J].Computer Measurement & Control,2007,15(2):145-148.(in Chinses)

[4] Bowman M J,Whitehead D G.A picosecond timing system[J].IEEE Transactions on Instrumentation and Measurement,2007,26(2):153-157.

[5] Chande P K,Sharma P C.Ultrasonic flow velocity sensor based on picosecond timing system[J].IEEE Transactions on Industrial Electronics,1986,33(2):162-165.

[6] Szplet R,Kalisz J,Szymanowski R.Interpolating time counter with 100 ps resolution on a single FPGA device[J].IEEE Transactions on Instrumentation and Measurement,2000,49(4):879-883.

[7] Zieliński M,Chbaerski D,Grzelak S.Time-interval measuring module with short dead-time[J].Metrology and Measurements Systems,2003,X(3):241-251.

[8] Zieliński M.Review of single-state time-interval measurement modules implemented in FPGA devices[J].Metrology and Measurement Systems,2009,XVI(4):641-648.

[9] 謝建華,葉衛東,韓躍峰.雙邊沿觸發計數器的設計和應用[J].兵工自動化,2006,25(4):71-72.XIE Jian-hua,YE Wei-dong,HAN Yue-feng.Design and application of double edge trigger counter[J].Ordnance Industry Automation,2006,25(4):71-72.(in Chinese)