基于VHDL語言的數(shù)字時(shí)鐘設(shè)計(jì)

李曉敏,田熙燕

(河南科技學(xué)院 機(jī)電學(xué)院,河南 新鄉(xiāng) 453003)

硬件描述語言VHDL是EDA技術(shù)的重要組成部分,也是電子設(shè)計(jì)主流硬件的描述語言之一,它具有很強(qiáng)的電路描述能力和建模能力,極好地反映了EDA設(shè)計(jì)的“自頂向下”的原則。而EDA技術(shù)作為硬件設(shè)計(jì)領(lǐng)域的先進(jìn)技術(shù)已經(jīng)在發(fā)展的過程中充分地顯現(xiàn)出其優(yōu)越性。利用EDA技術(shù)進(jìn)行電子系統(tǒng)設(shè)計(jì)的最后目標(biāo),是完成專用集成電路ASIC的設(shè)計(jì)和實(shí)現(xiàn)[1]。與傳統(tǒng)的設(shè)計(jì)方法相比,EDA技術(shù)可以用VHDL語言對系統(tǒng)進(jìn)行抽象的行為與功能描述,對設(shè)計(jì)的各個(gè)階段進(jìn)行模擬驗(yàn)證,同時(shí)由于VHDL具有與具體電路無關(guān)的特性,使得設(shè)計(jì)者大大節(jié)省了時(shí)間,提高了效率[2]。

1 數(shù)字時(shí)鐘的設(shè)計(jì)方案及框圖

1.1 設(shè)計(jì)方案

系統(tǒng)要完成的主要功能有:

1)數(shù)字時(shí)鐘按24 h制設(shè)計(jì),由6只數(shù)碼管顯示小時(shí)、分鐘、秒;

2)小時(shí)單元和分鐘單元具有復(fù)位功能,當(dāng)按下對應(yīng)按鍵時(shí),小時(shí)單元和分鐘單元復(fù)位為00;

3)動(dòng)態(tài)掃描功能,掃描輸出輪流點(diǎn)亮各個(gè)數(shù)碼管,可用來檢測數(shù)碼管的好壞;

由功能要求可將系統(tǒng)分模塊實(shí)現(xiàn)[3]。將系統(tǒng)分為7個(gè)模塊來實(shí)現(xiàn)。這7個(gè)模塊分別為:

①24進(jìn)制計(jì)數(shù)器;②60進(jìn)制計(jì)數(shù)器;③分頻器;④選擇顯示數(shù)據(jù)模塊:其功能為將輸入的六路信號(時(shí)十位﹑時(shí)個(gè)位﹑分十位﹑分個(gè)位﹑秒十位﹑秒個(gè)位)輪流選中送給七段顯示譯碼器,即在一個(gè)時(shí)間單元內(nèi)只顯示一路信號的值;⑤動(dòng)態(tài)掃描控制模塊:其功能為控制數(shù)碼管電路的亮滅,即完成對6個(gè)數(shù)碼管的掃描控制功能[3];⑥七段顯示譯碼器:完成BCD碼向7段顯示碼的轉(zhuǎn)換;⑦模六計(jì)數(shù)器:用來控制數(shù)碼管的片選信號,同時(shí)作為選擇顯示數(shù)據(jù)模塊的地址產(chǎn)生器。

1.2 系統(tǒng)的模塊框圖

如圖1所示,采用自頂向下的設(shè)計(jì)方法[4],通過對功能框圖的分析,將系統(tǒng)分模塊來進(jìn)行設(shè)計(jì),然后再通過例化語句完成各模塊間的銜接,最終實(shí)現(xiàn)了頂層描述,完成系統(tǒng)預(yù)定功能。

1.3 系統(tǒng)的工作流程描述

如圖1,時(shí)鐘系統(tǒng)具有一個(gè)使能端en、一個(gè)異步清零端clr以及時(shí)鐘脈沖輸入端clk。由6個(gè)計(jì)數(shù)器分別完成小時(shí)、分鐘、秒的計(jì)時(shí),并分別通過數(shù)據(jù)選擇器的6個(gè)輸入端送入選擇器,數(shù)據(jù)選擇器的使能端由一個(gè)模為六的計(jì)數(shù)器控制,輪流選中數(shù)據(jù)選擇器的6個(gè)輸入端,這樣,6個(gè)輸入端口的數(shù)據(jù)在數(shù)據(jù)選擇器的輸出端口就得到了串行輪流的輸出。此輸出作為七段顯示譯碼器的字符輸入端,經(jīng)譯碼后在數(shù)碼管顯示電路上顯示出對應(yīng)字形。數(shù)碼管顯示電路上的6個(gè)數(shù)碼管同樣采用輪流點(diǎn)亮的方式。由于循環(huán)的速度非常快,所以肉眼看起來仍然是同時(shí)顯示的感覺。

圖1 數(shù)字鐘模塊框圖Fig.1 Block diagram of digital clock model

2 各模塊的設(shè)計(jì)實(shí)現(xiàn)

2.1 24進(jìn)制計(jì)數(shù)器和60進(jìn)制計(jì)數(shù)器的實(shí)現(xiàn)

24進(jìn)制計(jì)數(shù)器的功能為完成計(jì)時(shí)電路中小時(shí)單元的計(jì)時(shí)功能[5],并且具有異步清零端clr(低電平有效)﹑使能端en(高電平有效);當(dāng)數(shù)字鐘處于正常計(jì)時(shí)狀態(tài)時(shí),完成小時(shí)計(jì)時(shí),并且受分計(jì)時(shí)模塊(60進(jìn)制)進(jìn)位輸出信號的控制。程序描述如下:

library ieee;--24進(jìn)制計(jì)數(shù)器VHDL語言描述

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity cnt24 is

port(clk,clr,en:in std_logic;

co:out std_logic;

ten:buffer std_logic_vector(3 downto 0);

one:buffer std_logic_vector(3 downto 0));end cnt24;

architecture art of cnt24 is

begin

co<='1'when (ten="0010"and one="0011") else'0';

process(clk,clr)

begin

if(en='1')then

if(clr='0') then

ten<="0000";

one<="0000";

elsif(clk'event and clk='1')then

if(one=3)then

one<="0000";

if(ten=2)then

ten<="0000";

else ten<=ten+1;

end if;

else one<=one+1;

end if;

end if;

else one<="0000";ten<="0000";

end if;

end process;

end art;

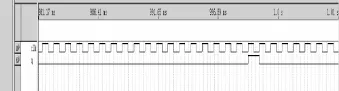

程序的仿真波形如圖2所示,en為使能端,co為計(jì)滿標(biāo)志位輸出。

60進(jìn)制計(jì)數(shù)器功能為完成計(jì)時(shí)電路中分單元和秒單元的計(jì)時(shí)功能,具有異步清零端clr(低電平有效)﹑使能端en(高電平有效)以及進(jìn)位信號co;其程序描述與24進(jìn)制計(jì)數(shù)器類似,其仿真波形如圖3。

2.2 分頻器的實(shí)現(xiàn)

分頻器的功能為將輸入的1 000 Hz的脈沖信號轉(zhuǎn)換為1 Hz的信號送給計(jì)時(shí)電路[6],作為電路的基準(zhǔn)脈沖信號,采用VHDL語言進(jìn)行描述,并利用軟件仿真。其程序描述如下:

library ieee;--分頻器VHDL語言描述

use ieee.std_logic_1164.all;

entity fenpin is

port(clk:in std_logic;

q:out std_logic);

end fenpin;

圖2 24進(jìn)制計(jì)數(shù)器仿真波形Fig.2 The 24 binary counter simulation

圖3 60進(jìn)制計(jì)數(shù)器仿真波形Fig.3 The 60 binary counter simulation

architecture arc of fenpin is

begin

process(clk)

variable cnt:integer range 0 to 999;

begin

if clk’event and clk=’1’ then

if cnt<999 then

cnt:=cnt+1;

q<=’0’;

else cnt:=0;

q<=’1’;

end if;

end if;

end process;

end arc;

仿真結(jié)果如圖4所示。

圖4 分頻器仿真波形Fig.4 The divider counter simulation

2.3 頂層電路設(shè)計(jì)

各個(gè)模塊建立起來后,通過仿真無誤,采用例化語句完成各個(gè)模塊間的銜接,最終完成頂層電路的設(shè)計(jì)。例化語句的具體描述為:

u1:cnt24 port map (clr=>clrc,clk=>b,en=>enc,one=>c,ten=>d);--24進(jìn)制計(jì)數(shù)器例化

u2:cnt60 port map (clr=>clrc,clk=>e,en=>enc,one60=>f,

ten60=>g,co60=>b);--60 進(jìn)制計(jì)數(shù)器例化

u3:cnt60 port map (clr=>clrc,clk=>h,en=>enc,one60=>i,ten60=>j,co60=>e);

u4:mux24_4 port map (ones=>c,tens=>d,onem=>f,tenm=>g,oneh=>i,tenh=>j,sel=>k,bcd=>l); --選擇顯示數(shù)據(jù)模塊例化

u5:seg7 port map(bcd=>l,segout=>shizhongout); --七段顯示譯碼器例化

u6:scan port map(sel=>k,seg6_com=>bcd_control); --動(dòng)態(tài)掃描控制模塊例化

u7:sel port map(clk=>clkc,sel=>k); --譯碼器例化

u8:fenpin port map(clk=>clkc,q=>h); --分頻器例化

以5 s時(shí)刻為例,掃描控制輸出輪流點(diǎn)亮各個(gè)LED數(shù)碼管;(11110-111101-111111-111011-110111-111111-101111-011111-11110---------)

七段顯示譯碼器輸出為 0(0111111),5(1101101),系統(tǒng)仿真波形如圖5所示。

圖5 系統(tǒng)級仿真波形Fig.5 The system simulation

系統(tǒng)的仿真結(jié)果證明,此設(shè)計(jì)能夠完成既定功能,設(shè)計(jì)過程是正確的。

3 結(jié)束語

本文通過電子時(shí)鐘的設(shè)計(jì)表明了VHDL設(shè)計(jì)的一般流程及其顯著特點(diǎn),把其下載到開發(fā)板上與其他外圍電路一起構(gòu)成了數(shù)字鐘的硬件系統(tǒng),并進(jìn)行設(shè)計(jì)測試,得到了良好的效果。同時(shí)表明了EDA技術(shù)“硬件設(shè)計(jì)軟件化”的特點(diǎn),在設(shè)計(jì)過程中不涉及具體硬件電路,這也是電子品設(shè)計(jì)的大趨勢。

[1]潘松,黃繼業(yè).EDA 技術(shù)實(shí)用教程(3)[M].北京:科學(xué)出版社,2006.

[2]艾明晶,金惠華.EDA教學(xué)實(shí)驗(yàn)設(shè)計(jì)實(shí)例——電子秒表電路的設(shè)計(jì)[J].儀器儀表學(xué)報(bào),2011,22(4):141-142.AIMing-jing,JIN Hui-hua.A design example ofEDA Teaching Experiment-the design of electronic stop-watch circuit[J].Chinese Journal of Scientific Instrument,2011,22(4):141-142.

[3]徐曉玲,田亞菲,崔偉.基于EDA仿真技術(shù)的電子時(shí)鐘系統(tǒng)設(shè)計(jì)[J].微計(jì)算機(jī)信息,2010,26(2):139-140.XU Xiao-ling,TIAN Ya-fei,CUI Wei.Electronic clock system design based on EDA simulation technology[J].Microcomputer Information ,2010,26(2):139-140.

[4]徐大詔.基于FPGA實(shí)現(xiàn)的數(shù)字鐘設(shè)計(jì)[J].信息技術(shù),2009(12):102-104.XU Da-zhao.Digital clock design based on FPGA[J].Information Technology, 2009(12):102-104.

[5]包本剛,朱湘萍.基于EDA技術(shù)的多功能數(shù)字時(shí)鐘的ASIC設(shè)計(jì)[J].微計(jì)算機(jī)信息,2008,24(12/2):212-214.BAO Ben-gang,ZHU Xiang-ping.ASIC design of multifunctional digital clock based on EDA technology[J].Microcomputer Information 2008,24(12/2):212-214.

[6]康華光.電子技術(shù)基礎(chǔ):數(shù)字部分(3)[M].5 版.北京:高等教育出版社,2006.