基于Interlaken協議的高速數據流接口設計與性能分析

陳世文, 郭 通,李玉峰,2,王 鵬, 楊柳青,3

(1.解放軍信息工程大學 河南 鄭州450002;2.防空兵指揮學院 信息控制系,河南 鄭州450052;3.中國移動河南信陽分公司 河南 信陽464000)

互聯網鏈路速率的飛速發展對路由器線路接口板的設計不斷提出新的要求。為解決線路接口板中器件間的高速數據交互問題,帶時鐘與數據恢復的新串行技術、差分信號技術等被普遍應用,使器件的數據總線速率從每管腳約100 Mb/s提升到每差分對管腳可達數Gb/s,從而使單個器件的數據流吞吐速率大大提高。在核心路由器40 Gb/s POS線路接口板的設計中,鏈路層處理芯片與轉發、調度處理FPGA間的數據交互速率高,且要求采用8對差分線完成,每對差分線為一個通道,每通道速率需達到6.25 Gb/s。為滿足這一器件間的高速數據流接口設計需求,除了考慮硬件設計工藝外,還必須采用高效率、高可靠的包傳輸互連協議,利用多個串行鏈接,完成具有通道化、流控背壓和數據完整性保護能力的數據通信。系統設計中采用Interlaken協議[1],在FPGA中實現其功能IP核,傳輸時先將數據包切割成一個個突發數據字,前后加入控制字,然后將由數據字與控制字組成的突發按照每8字節一個通道進行條帶化后成幀進行傳輸[2]。通過利用高端FPGA的高速通道和Interlaken IP核[3]設計技術,完成了鏈路層處理芯片與FPGA之間數據包的高速互聯,滿足系統40 Gb/s吞吐率的要求,并就不同應用場景中IP核關鍵參數與控制寄存器的配置進行了探索。

1 高速數據流接口需求分析

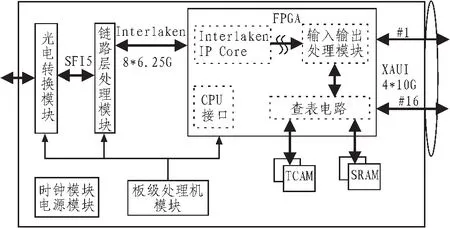

核心路由器40 Gb/s POS線路接口板原理框圖如圖1所示,鏈路層處理模塊采用Cortina公司的CS1999芯片,內含Interlaken硬核。FPGA采用Xilinx V5系列器件XC5VTX240T[4],在FPGA內部實現高速串行連接、Interlaken接口協議與轉發、調度處理等功能。鏈路層處理芯片和轉發、處理FPGA之間按要求采用8對差分線連接,每對差分線速率為6.25 Gb/s。

圖1 40 Gb/s POS線路接口板原理框圖Fig.1 Line interface board block diagram of 40Gb/s POS

2 高速數據流接口設計

2.1 Interlaken協議概述

Interlaken協議采用與SPI4.2[5]類似的簡單包控制字結構和64 B/67 B編碼,支持256個邏輯通道(可擴展至64 k)和帶內、帶外流控模式,串行通道數量與數據速率可擴展性強,具有頻率可編程的連續元幀格式用來保證通道對齊、同步擾碼器、時鐘補償和CRC校驗。由于采用了數據突發層CRC24檢驗、通道層CRC32校驗和數據擾頻器,從而確保了數據完整性和鏈路魯棒性。Interlaken的過程是:在發送端對數據包按一定數量的高速串行通道進行條帶化后組成幀傳送,在接收端由接收器件再重新解幀與組合還原原始數據。

其中,數據條帶化的過程是:將數據包根據參數BurstMax,BurstMin,BurstShort切割成一個個突發數據字,前后加入相應的控制字,然后將由數據字與控制字組成的突發按照每8字節一個通道進行條帶化,每個通道對應一個物理SerDes。

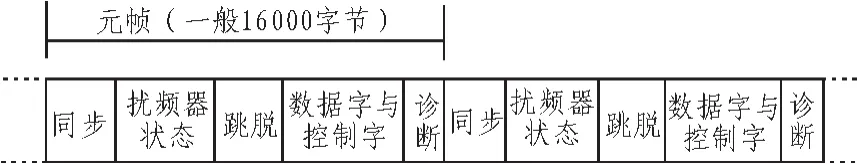

在成幀時,每個通道將條帶化的突發字封裝至其自帶的“元幀”,根據幀長加入1個同步字,1個擾頻器狀態字,1個診斷字,1個或多個跳脫字。元幀結構如圖2所示。

圖2 元幀結構Fig.2 Meta frame structure

傳輸時通常都是發送一個長為BurstMax的突發數據,緊跟著一個控制字。最短突發的執行是通過在下一個突發控制字前加額外的空閑控制字而實現的,最小突發保證的最小間隔示意圖如圖3所示。

圖3 最小突發間隔示意圖Fig.3 Minimum burst interval diagram

2.2 FPGA中的Interlaken IP核

在FPGA中實現的高速通道與Interlaken IP核頂層模塊框圖如圖4所示。

圖4 Interlaken頂層模塊框圖Fig.4 Block diagram of Interlaken top-level module

Interlaken IP核頂層模塊由接收和發送兩個模塊組成。接收模塊從串行通道接收Interlaken比特流,去除Interlaken封裝,并將512位寬原始數據流提交給用戶,供后面的FPGA邏輯處理。發送模塊接收用戶側512位寬包原始數據,按照Interlaken規范封裝數據,并將封裝數據發送至串行通道,通過控制/配置輸入對數據進行封裝。狀態/控制接口用于設置接口特性并監視其操作。包括:接收元幀狀態信號,接收錯誤狀態信號,發送速率限制信號,CRC32診斷檢測信號(用于監測每個通道的工作狀態是否正常),Interlaken接收狀態信息,Interlaken發送狀態信息,發送多重使用比特,接收多重使用比特,發送流控輸入,接收流控輸入,發送FIFO門限等。

2.3 接口時序關系

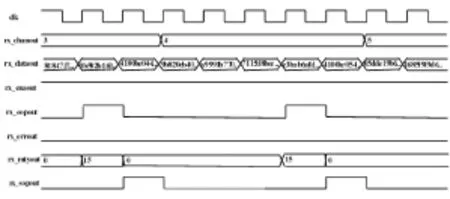

發送端總線接口同步接收任意長度的包原始數據,所有信號都與clk上升沿同步。一個65字節包發送端采樣波形時序示意圖如圖5所示。

圖5 發送波形采樣時序示意圖Fig.5 Timing diagram of the transimitting waveform samples

接收端總線接口同步接收包原始數據。一個65字節包接收端采樣波形時序示意圖如圖6所示。

圖6 接收波形采樣時序示意圖Fig.6 Timing diagram of the receiving waveform samples

3 高速數據流接口實現

3.1 實現方案

按照自頂向下的設計思路,給出發送側硬件電路模塊級設計方案,如圖7所示。

圖7 發送側硬件電路模塊設計示意圖Fig.7 Hardware circuit design module of transmit block

其中,速率調整緩存模塊接收用戶側送來的傳送數據,若用戶側發送速率高于Interlaken傳送速率,則調整該模塊的輸出速率,并對新進入數據緩存;數據切割模塊按照Interlaken協議的切割算法和控制與狀態模塊配置的Burstmax、Burstmin和 Burstshort參數對輸入數據包進行切割;突發字組裝模塊按照8字節數據字格式將切割后的數據組裝成數據字,同時按照控制字格式和控制與狀態模塊的配置信息組裝相應的控制字;CRC24模塊完成協議層CRC24(x24+x21+x20+x17+x15+x11+x9+x8+x6+x5+x+1)[6]計算;突發組合模塊基于CRC24計算結果和突發字組裝結果完成一次突發組合;條帶化模塊將輸入突發字按照條帶數量實施條帶化,每8字節數據輪詢發送至N個條帶;64/67模塊按照64B/67B編碼格式對各個條帶數據進行編碼;同步和跳脫模塊按照同步和跳脫字的結構及下發的控制狀態組成各條帶新幀的同步字和跳脫字;CRC32對各條帶原幀進行CRC32計算并生成新的診斷字,計算多項式[6]為:x32+x28+x27+x26+x25+x23+x22+x20+x19+x18+x14+x13+x11+x10+x9+x8+x6+1

加擾模塊根據當前擾碼狀態字加擾數據流;組幀及對齊模塊根據原幀結構組成原幀,并根據需要決定是否實施通道對齊;serdes模塊是串行/解串行模塊,完成并串轉換,將高速串行數據輸出。控制與狀態模塊對各協議層處理模塊和幀層處理模塊進行控制和配置。

Interlaken協議硬件處理在性能上要以線速轉發處理為目標,對 40字節分組來說,Interlaken接口為 OC-768(40 Gb/s)時,線速分組時間僅為8 ns,可見,要實現對OC-768或者更高速率的Interlaken接口支持,必須引入并行流水線硬件設計技術,由此,上述模塊級設計中遵循兩個原則:

1)次序保證原則 該原則要求在任務劃分過程中,必須保證各串行子任務在處理時間上的順序性,以保證IP分組得到正確處理;

2)并行處理原則 在次序保證原則的基礎上,該原則要求所有可并行處理的子任務作并行處理,以縮短IP分組的處理時間。

遵循上述兩個原則,可進一步對各個模塊內部作更深入的電路設計,本文不再給出。接收流程與發送流程相反,模塊設計也相反,本文也不再給出。

3.2 基于XILINX FPGA的實現思路

目前,高端FPGA普遍支持高速串行/解串行模塊,例如XILINX V5 FPGA[5]的 GTX 可支持 6.25 Gb/s,而 Altera Stratix IV GX FPGA[7]的GTX可支持6.5 Gb/s。下面以XILINX V5 FPGA實現40 Gb/s接口為例,給出Interlaken接口FPGA內部實現思路。

1)根據接口速率選定配置方案,常見的為8×6.25 G和16×3.125 G,其中 8×6.25 G 使用 tile數量是 16×3.125 G 的 1/2,但單對差分線速率達到6.25 G,對PCB設計要求高。確定配置后,即可選定tile,若選擇8×6.25 G則可盡量選擇4個相鄰tile,以便tile時鐘可以公用。

2)設計系統數據寬帶和時鐘方案:若內部總線為32,單個lane內部的處理時鐘需達到6.25 G/32,與GTX的發送和接收時鐘同步;此外,用戶側時鐘和數據配置時鐘和總線既要滿足帶寬需求:>40 G,又要滿足頻率要求:>(8×6.25 G)/32,常見配置為512寬帶或者256寬帶,總線頻率為200 MHz。

3)選擇GTX功能模塊并例化GTX核:PCS部分BYPASS 8 B/10 B,選擇gearbox模塊,并選擇其模式為外部順序控制,PMA部分選擇PISO,并根據需要配置預加重和均衡等。

4)按照2.1實現除serdes之外Interlaken協議處理模塊。

5)將Interlaken協議處理模塊和gTX核對接,完成整個設計。

4 測試數據與性能分析

高速通道硬件設計和Interlaken IP核是滿足系統吞吐率要求的關鍵因素,為驗證系統功能,采用的基本調試與測試方法是:通過上位機單板處理軟件控制鏈路層商用芯片PRBS或固定負載的定長包和變長包作為數據源,發出數據包,由FPGA Interlaken核接收端經FIFO打環再由核發送端送回商用芯片,并對發送包與接收包進行統計對比分析。表1是在40 Gb/s速率下,突發分割參數BurstShort=64,BurstMax=256時,各種數據包長的發送接收傳輸測試數據。

由表1可以看出,當BurstShort=64,BurstMax=256時,40Gb/s速率下,各種包長的數據報環回時無丟包發生。證明高速通道硬件設計滿足要求,相應的Interlaken IP突發配置參數下性能可以達到40 Gb/s的吞吐率。

表1 速率為40 Gb/s時的發送與接收包數據Tab.1 Number of transmiting and receiving packets at 40 Gb/s wire-speed

為驗證Interlaken IP核突發分割參數配置對數據吞吐率的影響,在不同速率下對各種包長的數據包進行了大量測試。其中,特定分割參數(BurstShort=192,BurstMax=256)時,得到的定長數據包在各種速率下的傳輸性能測試數據特性圖如圖8所示。

圖8 不同速率下的數據包丟包率(BurstShort=192,BurstMax=256)Fig.8 Packet loss rate under different Rates(Burstshort is 192 and BurstMax is 256)

由圖8可以看出,當BurstShort=192,BurstMax=256時,在38Gb/s速率以下,各種包長的數據包無丟包發生。在40Gb/s速率時,某些包長的數據包存在丟包現象。說明IP核突發分割參數配置對數據吞吐率有影響,因此需要在應用時優化IP核的參數配置。

5 結束語

在核心路由器40 G POS線路接口板設計任務中,基于Interlaken協議,利用Xilinx V5TX240T FPGA的GTX高速通道完成了鏈路層處理芯片與轉發、處理FPGA之間數據包的高速互聯,采用8個高速通道,每通道速率6.25 Gb/s,滿足了系統40 Gb/s吞吐率的要求。下一步的研究思路是:在實際網絡環境中,綜合考慮數據流的流長分布特征與IP核參數的關系,實現參數的在線可重構配置,基本方法是將數據傳輸效率與正確率的統計結果反饋給單板軟件,利用單板軟件和處理機接口,對Interlaken核的參數進行修改,以數據包的包長分布、數據包流量以及包速率為主要特征,建立應用現場的包分布特征模型,從而實現IP核關鍵參數與控制寄存器的自適應、動態可重構配置。

[1]Cortina,Cisco.Interlaken protocol definition, version 1.2[EB/OL].(2008-10-07).http://wenku.baidu.com/view/90303e 3610661ed9ad51f31a.html.

[2]Cisco.Interlakentechnology:new-generationpachetinterconnect protocol[EB/OL].(2007-03-08).http://read.pudn.com/downloads139/doc/comm/596874/Interlaken_White_Paper-March_2007.pdf.

[3]ASIC Interlaken IP Core.SLE interlaken SLE interlaken IP key features[EB/OL].(2007-01).http://www.siliconlogic.com/pdfs/SLE_Interlaken_IP_Data_Sheets.pdf.

[4]XILINX.Virtex-5 FPGA rocketIO GTX transceiver user GuideUG198[EB/OL].(2009-10-30).http://www.datasheetarchive.com/datasheet-pdf/0100/DSA00219189.html.

[5]Optical internetworking forum.System packet interface level 4(SPI-4)Phase 2:OC-192 system interface for physical and link layer devices[EB/OL].(2001-01).http://www.docin.com/p-213161926.html.

[6]Castagnoli G,Brauer S,Herrmann M.Optimization of cyclic redundancy-check codes with 24 and 32 parity bits[J].IEEE Transactions on Communications,1993,41(6):883-892.

[7]Altera Corporation.Stratix IV device handbook.[EB/OL](2011-04).http://www.altera.com.cn/literature/hb/stratix-iv/stx4_5v4.pdf.