基于高速D/A AD9739的寬帶信號產(chǎn)生*

王 錳,呂衛(wèi)祥

(南京船舶雷達研究所,南京 210003)

1 引言

自雷達問世以來,人們通過雷達看到的所謂“目標”一直都是A/R 顯示器上的“尖頭脈沖”或PPI 顯示器上的“亮點”。但是,人們也一直希望雷達能像“眼睛”一樣看到目標的“形象”,即真正的目標“圖像”,這就需要采用寬帶雷達技術。寬帶雷達能提供高分辨目標距離剖面圖(一維距離像),幫助目標分類識別,提高目標距離測量精度,提高抗干擾能力,降低多路徑效應,并能提供更好的在雜波中目標檢測的能力[1]。寬帶雷達技術與合成孔徑(或逆合成孔徑)技術同時采用,則可形成目標的高分辨二維圖像。

在目前的寬帶雷達中,脈內寬帶線性調頻信號是一種最常用的信號形式。產(chǎn)生線性調頻信號有兩種基本方法,即模擬法和數(shù)字法。模擬法一般是通過線性鋸齒電壓控制壓控振蕩器產(chǎn)生線性調頻信號或者利用SAW(聲表面波)器件作為展寬網(wǎng)絡產(chǎn)生調頻信號。但是,壓控法存在每個脈沖起始的射頻相位不相參的問題,且穩(wěn)定性較差,相位噪聲和諧波分量也比較大;SAW 器件法受SAW 器件物理尺寸限制,產(chǎn)生信號脈寬較短,且不同脈寬的信號需采用不同的聲表面波器件。

隨著大規(guī)模集成電路的發(fā)展,直接數(shù)字合成(DDS)法較多地被應用于寬帶線性調頻信號的產(chǎn)生,使用直接數(shù)字合成技術能產(chǎn)生任意波形,并能對輸出波形的頻率、幅度和相位進行精確的控制。另外,DDS還被應用于頻率合成器中,產(chǎn)生時鐘、倍頻鏈輸入信號等較低頻率的連續(xù)波信號。目前,直接數(shù)字合成法硬件方案主要有兩種,一種是DDS ASIC 芯片法,DDS 芯片內部集成DDS 核及高速D/A 轉換器,利用DSP、FPGA 或CPLD 給DDS 芯片送入控制字,即可得到所需帶寬、脈寬、周期及頻率信號;另一種是FPGA與高速D/A 轉換器結合,由FPGA 完成DDS 核的功能,送高速D/A 轉化器轉換為模擬信號[2]。第一種方法工作時鐘頻率較高,但靈活性欠佳,主要用于連續(xù)波以及簡單脈沖信號的產(chǎn)生;第二種方法靈活性較強,可以用于任意波形的產(chǎn)生,但受限于FPGA的工作頻率,主要用來產(chǎn)生較低頻率的中頻信號。隨著集成電路技術的不斷發(fā)展,F(xiàn)PGA 工作時鐘不斷得到提高,與高速D/A 結合能用于寬帶任意信號及高中頻連續(xù)波信號的產(chǎn)生,本文介紹的即是此種方法。

2 原理分析

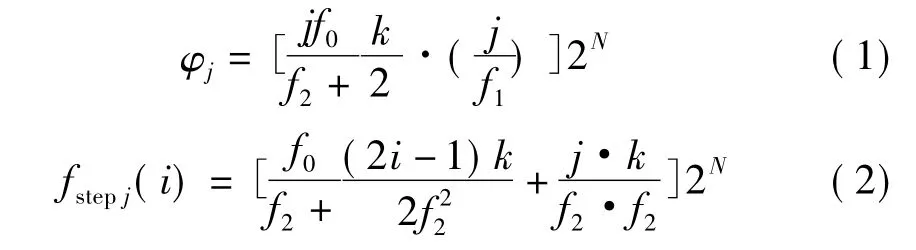

為提高端口傳送速率,時鐘頻率在1 GHz 以上的D/A 芯片通常采用雙沿數(shù)據(jù)傳送(DDR)模式。本文中所采用的D/A為雙輸入數(shù)據(jù)端口,每個端口最高速率為1.25 GSPS,DDR 模式,而FPGA 內部采用普通I/O口傳送方式無法直接輸出如此高速率的數(shù)據(jù),需要采用新型FPGA 提供的ChipSync 特性,通過多通道合成的并串轉換技術來實現(xiàn)。為保證系統(tǒng)工作的穩(wěn)定性,本方案中最終設計FPGA 輸出端口工作在雙路端口速率各為1.2 GSPS,DDR 模式。采用16 通道數(shù)據(jù)合成1 通道的方式為D/A 芯片提供數(shù)字波形數(shù)據(jù),設計D/A 工作時鐘速率為2.4 GSPS。為產(chǎn)生寬帶線性調頻信號,假設其帶寬為B,起始頻率為f0,脈寬τ,根據(jù)文獻[3]的推導,16個通道中第j個通道的初相和第i個采樣時刻的數(shù)據(jù)和頻率步進碼分別為

3 硬件實現(xiàn)

根據(jù)公式(1)、(2)的計算結果,可利用FPGA 產(chǎn)生16個通道的信號數(shù)據(jù),通過并串轉換排序輸出給D/A后,就能得到所需要的信號。

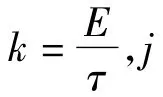

硬件平臺主要包含XILINX 公司的VIRTEX-5 系列FPGA XC5VSX50T,AD 公司的2.5GSPS D/A 轉換器AD9739,NS 公司的時鐘分配芯片LMK01000 及穩(wěn)壓電源芯片等,硬件原理框圖如圖1。

XC5VSX50T FPGA為XILINX 公司基于65 nm 工藝的新一代FPGA,包含288個DSP48E Slices,最大4752 Kb Block RAM 以及最大480個用戶可定義I/O口,其時鐘管理片中包含兩個DCMs和一個PLL,其中DCMs 最高輸入時鐘450 MHz,最高輸出時鐘500 MHz,PLL 最高輸入時鐘645 MHz,內部VCO 最高工作頻率可達1 000 MHz,支持OSERDES技術實現(xiàn)高速IO 口互聯(lián)。

圖1 硬件原理框圖

AD9739為AD 公司一款高速高性能RF 數(shù)模轉換器,內部最高采樣率達2.5 GSPS,雙通道LVDS 數(shù)據(jù)輸入,每個通道數(shù)據(jù)最高速率1.25 GSPS(DDR),當工作在其獨特的“MIX MODE”下時,可將第二或第三奈奎斯特區(qū)的輸出信號直接用作發(fā)射信號,減少混頻環(huán)節(jié),真正以“軟件無線電”的方式實現(xiàn)了上行通道功能。FPGA VHDL 程序設計主要包含時鐘分配,DDS 數(shù)據(jù)產(chǎn)生,并串轉換等。在本例中,F(xiàn)PGA 內部OSERDES 模塊的CLK(串行數(shù)據(jù)時鐘)和CLKDIV(并行數(shù)據(jù)時鐘)分別為600 MHz和150 MHz,受限于FPGA的布局及DCM的最高工作頻率,CLK 及CLKDIV 只能用FPGA內部的PLL 模塊產(chǎn)生。時鐘分配主要是將來自LMK 01000的300 MHz時鐘(為保證時鐘的相參,將AD 9739 工作時鐘的四分頻DCO 輸出用LMK 01000 再二分頻后送FPGA的全局時鐘輸入端)經(jīng)過PLL后,得到150 MHz和600 MHz,其中150 MHz分別作為FPGA的工作時鐘和OSERDES 模塊的CLKDIV,600 MHZ時鐘作為OSERDES 模塊的串行時鐘CLK。DDS 數(shù)據(jù)產(chǎn)生主要是產(chǎn)生16組初相位不同的DDS 數(shù)據(jù),經(jīng)排序后送給FPGA 內部的OSERDES 模塊。并串轉換作用主要是將16組低速并行數(shù)據(jù)轉換為雙14 位串行高速DDR數(shù)據(jù),并同時送出同步數(shù)據(jù)時鐘,在同步時鐘的同步下將數(shù)據(jù)送往AD 9739。

此外,還通過對板載的AT89C 2051 單片機的編程來設置AD 9739和LMK 01000的功能參數(shù)和芯片初始化,以保證其正常穩(wěn)定工作。

4 測試數(shù)據(jù)

4.1 寬帶脈內線性調頻信號測試數(shù)據(jù)

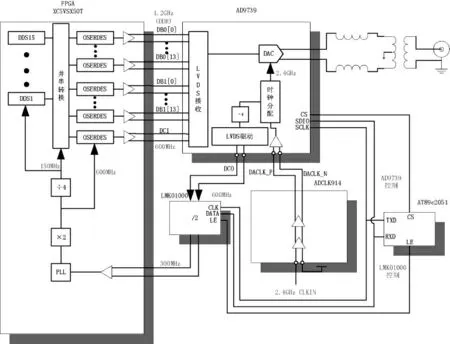

采用微波信號源提供AD 9739 2.4 GHz的工作時鐘,AD 9739 工作于Normal MODE,利用上述硬件平臺產(chǎn)生544 MHz中心頻率,帶寬為200 MHz,脈寬為178 μs的線性調頻信號,其頻譜及時域波形如圖2所示。可見,在未濾波的情況下,帶內平坦度在0.5 dB 內。

圖2 中頻寬帶線性調頻信號頻域及時域圖

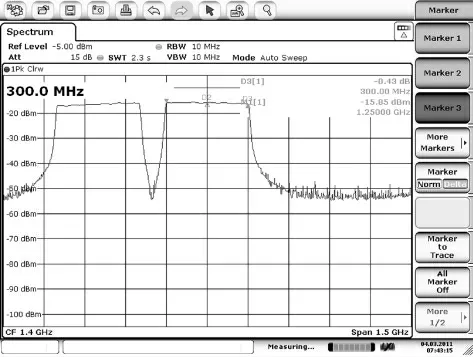

采用微波信號源提供AD 9739 2.4 GHz的工作時鐘,AD 9739 工作于MIX MODE,利用上述硬件平臺產(chǎn)生1 400 MHz中心頻率,帶寬為300 MHz,脈寬為178 μs的線性調頻信號,其頻譜見圖3。可見,在未濾波的情況下,帶內平坦度在0.5 dB 內,這比普通D/A的輸出在第二奈奎斯特區(qū)的大幅度滾降有相當大的改善。

4.2 連續(xù)波信號測試數(shù)據(jù)

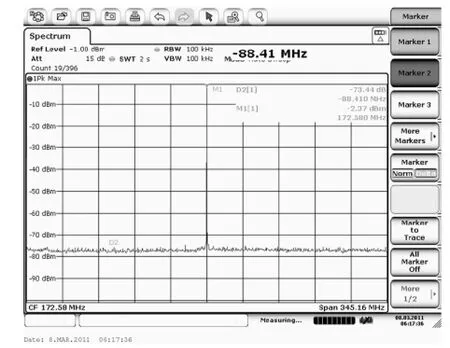

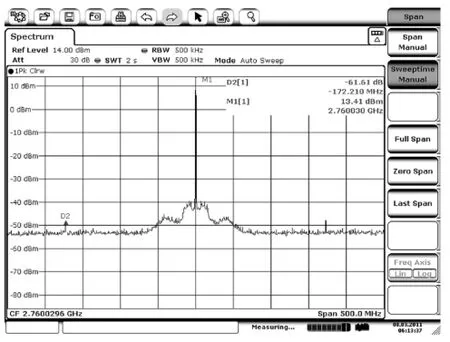

采用微波信號源提供AD9739 2.4 GHz的工作時鐘。AD 9739 工作于Normal MODE,利用上述硬件平臺產(chǎn)生172.5 MHz的連續(xù)波正弦信號,其頻譜圖如圖4所示。可見,雜散可達到-75 dBc 以下,將172.5 MHz濾波后,經(jīng)過十六倍頻得到2760 MHz的微波連續(xù)波信號,其頻譜圖如圖5所示,其雜散可達-60 dBc 以下。

圖3 MIX MODE 下射頻寬帶線性調頻信號頻譜圖

圖4 172.5 MHz 連續(xù)波信號頻譜及波形圖

圖5 2760 MHz 連續(xù)波信號頻譜圖

5 結束語

將FPGA與高速D/A 結合,用DDS 產(chǎn)生544 MHz中心頻率、200 MHz 帶寬的線性調頻信號,再用本振一次混頻得到寬帶通道的微波激勵信號,此方案目前已應用在某型雷達樣機中取代倍頻方案。經(jīng)測試,信號參數(shù)及最終脈壓結果比倍頻方案有較大改善。而利用上述方案產(chǎn)生較低頻率連續(xù)波,經(jīng)倍頻得到微波一本振,雜散指標也比原專用DDS 芯片AD 9858的方案提高了10 dB 以上,可用于高性能數(shù)字式頻率合成器的設計。

目前,限于D/A的工作頻率,輸出信號頻率還比較低,仍需要一次混頻或倍頻才能得到所需要的更高微波頻段信號。隨著模擬和數(shù)字器件工藝的發(fā)展,D/A 及FPGA的工作頻率會不斷得到提高,基于DDS的信號產(chǎn)生方式會得到越來越廣泛的應用,“軟件無線電”也會逐步實現(xiàn)。

[1]費元春.寬帶雷達信號產(chǎn)生技術[M].北京:國防工業(yè)出版社,2002.

[2]A Technical Tutorial on Digital Signal Synthesis[M].Analog Device,Inc.1999.

[3]蔣倜.并串轉換法合成多通道寬帶DDS信號[J].雷達與對抗,2009(4).