高速信號處理終端設備的設計?

李燕春

(中國西南電子技術研究所,成都610036)

高速信號處理終端設備的設計?

李燕春

(中國西南電子技術研究所,成都610036)

針對某寬帶中頻軟件無線電終端設備,提出了一種高速ADC數據的接收方法,實現了多通道高速波形的采集和接收,并通過靈活的功能重構方式實現了終端設備各種復雜的功能,使用可配置的專用芯片產生出滿足各種工作模式下的高速抗干擾模擬中頻波形。這些方法和技術已在實際工程中成功應用。

軟件無線電;DDR接收機;功能重構;中頻數字化

1 引 言

某高速終端設備可以多通道高速采集信息,數據傳輸帶寬可達到兆級,傳輸延遲低,并對信息進行高速實時處理,實現傳感器間互相交換數據和信息共享。中頻信號處理是整個端機的核心部分,它采用寬帶中頻軟件無線電方式[1],以通用的硬件平臺為依托,使用FPGA和DSP對數字化后的各種高速中頻波形進行同步、數字濾波、抽取和內插、信道編解碼、各種波形的數字調制和解調等處理[2]。從實現的功能上看,中頻信號處理終端設備大致可以分成多通道高速ADC及模擬波形數字化采集部分、數字信號處理算法部分、中頻高速DAC及模擬波形產生部分。

本文介紹各部分底層設計的關鍵技術,即高速波形中頻數字化采集、系統功能重構方式和中頻高速波形的產生。

2 實 現原理及工程應用

2.1 高速波形中頻數字化采集

中頻部分傳輸的數據帶寬寬,接收通道有8路,如果采用并行14位輸出的ADC則數據位數為112,會占用FPGA大量的I/O和印制板空間,不能滿足設備小型化要求,因此本文中頻寬帶ADC采用了TI公司的ADS6445,它集成了4通道ADC,最高采樣率125 Msample/s,模擬信號輸入帶寬500 MHz,14位數據輸出,串行LVDS接口,可以設置成單線或雙線的單數據率(SDR)或雙數據率(DDR)方式輸出,數據輸出位數最多32路。可編程LVDS電流和內部端接電阻,此特點可以用來擴張眼圖,提高信號完整性。

ADC輸出數據先送入FPGA處理,因此保證FPGA數據接收正確性,是后續各種數字信號處理算法實現的基礎,也是系統能否實現的關鍵。串行方式減少了數據線但提高了數據傳輸率。ADC采樣率100 MHz,14位數據串化后傳輸時鐘將達到1 400 MHz,時鐘周期只有0.714 ns,因此在PCB布線時對此高速時鐘的走線要求嚴格。另外,FPGA內部走線的時延這時也會對數據正確接收產生至關重要的影響[3]。這么高的速率,它的理想預計數據采樣窗口很窄,而且接收端因為PCB寄生電容電感等影響、采樣時鐘抖動和占空比失真、電源電壓和溫度的變化引起的采樣漂移會使有效數據采樣窗口變得更窄,嚴重時根本無法接收,必要時還需要增加傳感器對電壓和溫度進行實時偵測以增加有效數據采樣窗口寬度,從而增加了系統的復雜性。為了提高系統的可靠性,工程上將ADC數據輸出方式設置成雙線DDR傳輸,每對LVDS差分線傳輸8位數據,這樣傳輸時鐘可降到400 MHz,單線數據傳輸率800 Mbit/s,時鐘周期增加到了2.50 ns,數據采樣窗口變寬,這樣經過一次時鐘采樣點的調整就可實現各種工作環境下的要求。

FPGA選用了Xilinx公司的Virtex-4系列芯片,此系列芯片帶有專門的串并轉換器ISERDES邏輯資源,可以避免在使用FPGA的架構設計高速串并轉換器時遇到的時鐘復雜性問題,便于高速源同步應用的實現。此邏輯資源支持快速的I/O數據率,支持單數據率(SDR)方式和雙數據率(DDR)方式,支持存儲器接口和網絡接口,含有BITSLIP子模塊,在訓練序列的幫助下,可以重新調整數據至字邊界。

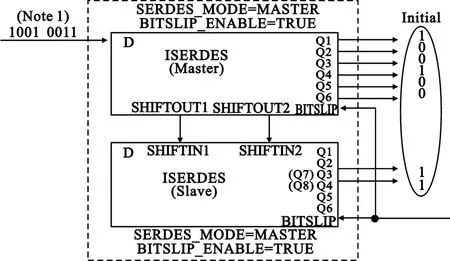

FPGA對高速DDR數據的正確接收可分為位調整和字調整兩個階段,位調整階段就是時鐘采樣點的調整,保證每位數據的正確接收;字調整階段就是調整字里每位數據的排列順序,得到最終的并行數據。單個ISERDES采用DDR接收時,數據寬度最大6位,通過將IO口的兩個ISERDES設置成主從方式,可以將數據接收寬度擴展到8或10。由于一路ADC分成雙線后,其中一個至少7位,所以必須將ISERDES設置成8位主從數據擴展接收方式,如圖1所示。

圖1 ISERDES寬度擴展Fig.1 ISERDESwidth expansion

首先是位調整階段,先要進行DDR源同步中心調整,對FPGA進行綜合布線時,必須對時鐘和數據信號線進行時序約束。在UCF文件中對信號線進行下述的時序約束能夠保證時鐘沿對準數據沿正中:

OFFSET=IN 0.6 25 ns VALID 1.25 ns BEFORE adc-bitclk TIMEGRP adc-bitclk-Rising;OFFSET=IN-0.625 ns VALID 1.25 ns BEFORE adc-bitclk TIMEGRP adc-bitclk-Falling;

這比使用IODELAY邏輯資源方式調整速度更快,以滿足實時性要求。位調整好后,ISERDES能夠正確接收并行數據字的每位,但字的排列順序不同,這時則需要利用ISERDES的BITSLIP子模塊進行字調整。BITSLIP每使能一次,字的排列順序旋轉一次。因為接收字是8位,所以最多只需要8次調整。ADS6445具有發送已知訓練序列和正常采樣兩種工作方式,工程應用中,每次上電時將ADS6445配置成發送已知訓練序列工作方式。FPGA將接收到的并行數據與訓練序列比較,如果不同,則進行一次調整后再比較,直到得到正確的數據。全部調整結束后將ADS6445配置成正常采樣的工作方式。

在中頻接收端輸入固定頻率的中頻正弦波形,用ChipScope Pro Analyzer工具觀察FPGA內ISERDES接收到的數據,圖2是將各采樣點的數據直接連接起來描繪成的波形,可直觀地表明數據接收的正確性。

在工程中,用這種方式設計的高速DDR接收機穩定可靠,最多只需要300 ns就可以完成全部調整,為后續的數字信號處理算法實現奠定了基礎,而且可以檢測每路接收通道是否工作正常,并可將此作為狀態自檢信號上報整機。這種方法同樣也可以用于高速傳輸數據的接收。

2.2 終端設備功能重構的實現

數字信號處理部分采用一片Xilinx公司Virtex -4系列FPGA加兩片TI公司TMS320C6416定點DSP的架構,實現終端設備全部工作方式,是整個端機的核心。采用對FPGA和DSP進行版本動態加載實現功能重構。

FPGA的版本動態加載通過CPLD加FLASH方式實現。多個FPGA的設計版本事先分段燒寫在FLASH中,在CPLD中設計了控制FPGA的*.bit文件加載時序的控制程序,工作時通過拉低FPGA的PROG-B信號啟動配置進程,采用地址映射方式選擇FLASH中FPGA的*.bit文件,讀出配置數據,選擇FPGA的Slave SelectMAP方式加載。最后一幀配置數據傳輸完畢后,如果CRC校驗正確,FPGA進入啟動階段,當DONE信號變高,配置過程結束,FPGA

進入工作狀態;如果CRC校驗不正確,FPGA會拉低INIT-B放棄配置,這時CPLD檢測到INIT-B的下降沿,復位配置控制程序,并將PROG-B信號再次拉低,重新開始配置;如果CPLD連續檢測到5次INIT-B下降沿,則放棄配置,上報錯誤信息。每個版本的加載時間大約要200 ms。

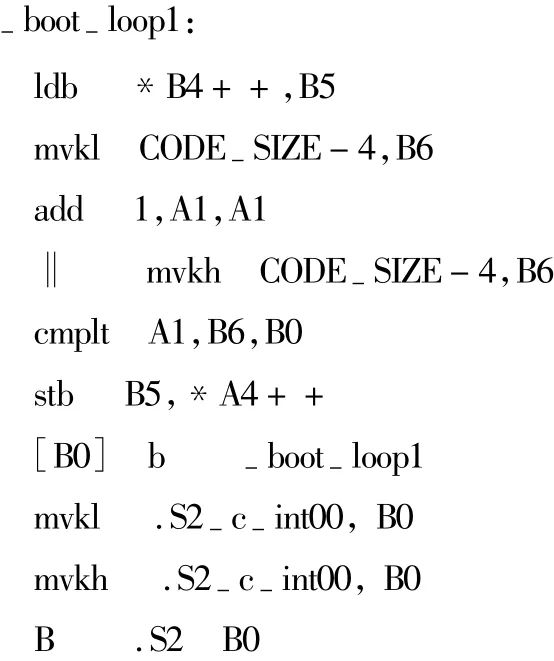

DSP軟件重構利用二次自舉程序實現。當TMS320C6416選擇了從EMIFB自舉時,DSP復位信號釋放后,CE1空間開始的1 kyte數據以EDMA方式自動傳送到內存地址0,塊傳輸結束后,CPU從“停止”狀態釋放出來,從內存地址0開始執行程序[4]。

用戶程序一般都大于1 kbyte,因而需要自行設計二次自舉程序,將用戶程序拷貝到內存中。二次自舉程序必須固化在FLASH中前1 kbyte內,而用戶版本程序則分段固化在1 kbyte地址以后。DSP每次復位后,二次自舉程序首先被自動拷貝進內存,接著二次自舉程序拷貝用戶程序到內存中,完成后用戶程序入口地址被賦給CPU程序指針,于是CPU開始執行用戶程序。通過在CPLD中作地址映射,將用戶程序在FLASH中的地址轉換成對應二次自舉程序相同的起始地址,這樣就可以根據工作方式選擇不同的DSP程序版本。下面是二次自舉程序的源代碼:

工程上,利用上述方法穩定可靠地實現了多種工作方式的切換。

2.3 中頻高速波形的產生

各種抗干擾抗截獲高速模擬中頻波形的產生采用美國AD公司近期推出的一款雙路16 bit數據寬度、數據采樣率高達1 Gsample/s的TxDAC+專用芯片AD9779實現。它將內插濾波器、正交調制器、DAC轉換器、鎖相環倍頻器集成在同一芯片內,并且可以通過芯片內的數字控制器對它們進行不同的組合,因而使該芯片工作方式靈活多樣,具有DAC轉換后直接發射的特性。

外部基帶數據可以通過內插后直接調制在片內的本振頻率上,也可以將已調制數字載波內插后與片內的本振頻率進行混頻以實現數字上變頻,最后得到的數字中頻信號通過16 bit DAC轉換成模擬中頻發射信號。AD9779內部正交調制器也可以被旁通而直接將外部數字信號轉換成模擬信號。AD9779具有反sinc濾波器,以補償平頂采樣所造成的失真。AD9779產生的模擬中頻發射信號的驅動電流大小可以在8.7~31.7mA范圍內調整。

AD9779共有32個控制寄存器,其中26~31保留未用,其它0~25用來設置各種工作方式。

例如要將7 MHz數字中頻信號上變頻到102 MHz再發射出去,可以將7 MHz數字中頻信號的采樣率設為95 MHz,AD9779片內用760 MHz的采樣時鐘產生95 MHz的數字本振頻率,這樣在7 MHz數字中頻信號8倍內插后與數字本振頻率相乘混頻[4],就可將其數字上變頻到102 MHz的數字中頻,然后將其DAC后就能輸出102 MHz的模擬中頻載波信號。

工程上,已經用AD9779實現了多種中頻調制波形的發射。AD9779由于能靈活地配置,具有良好的性能,是通用硬件平臺設計一個很好的選擇。

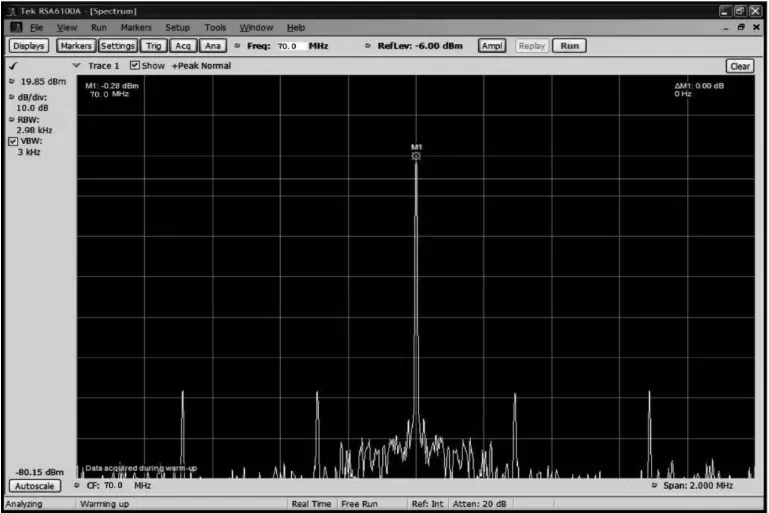

圖3是用Tektronix RSA6114A頻譜儀測得的70MHz單載波中頻發射信號的頻譜,可見信噪比可以達到58 dB。

圖3 70 MHz中頻發射信號頻譜圖Fig.3 Transmitted 70 MHz intermediate frequency signal spectrum

3 結束語

高速DDR接收機的正確設計保證了高速ADC數據的可靠接收,為終端設備高速性能的實現打下了堅實的基礎。終端設備功能重構的實現方式具有很高的靈活性,只要有容量足夠的存儲器件,就可使終端設備實現對應其硬件平臺的多種功能,并可以無限地增加,為設備功能的實現和擴展提供了強有力的支撐。多種功能集成DAC芯片的靈活使用也保證了各種高速抗干擾模擬中頻波形的產生。

[1]楊小牛,樓才義,徐建良.軟件無線電原理與應用[M].北京:電子工業出版社,2002. YANG Xiao-niu,LOU Cai-yi,XU Jian-liang.Software Defined Radio Theory and Application[M].Beijing:Publishing House of Electronics Industry,2002.(in Chinese)

[2]貝耶爾,劉凌.數字信號處理的FPGA實現[M].北京:清華大學出版社,2011. Meyer-Baese U,LIU Ling.Digital Signal Processing with Field Programmable Gate Arrays[M].Beijing:Tsinghua University Press,2011.(in Chinese)

[3]何賓.FPGA數字信號處理實現原理及方法[M].北京:清華大學出版社,2010. HE Bin.FPGA Digital Signal Processing Theory and Method[M].Beijing:Tsinghua University Press,2011.(in Chinese)

[4]StevenW Smith,張瑞峰,詹敏晶,等.實用數字信號處理:從原理到應用[M].北京:人民郵電出版社,2010. Steven W Smith,ZHANGRui-feng,ZHANMin-jing,etal. Digital Signal Processing A Practical Guide for Engineer and Scientists[M].Beijing:People′s Posts and Telecommunications Press,2010.(in Chinese)

Design of a High Speed Signal Processing Term inal Equipment

LIYan-chun

(Southwest China Institute of Electronic Technology,Chengdu 610036,China)

According to the requirement of a broad band intermediate frequency(IF)software-defined radio(SDR)terminal equipment,a high speed ADC data receivingmethod is proposed to implementmulti-channel high speed wave sampling and receiving.The versatile functios of terminal equipmentare realized by flexible reconfiguration.High speed anti-jamming analog IFwaves in various operationmodes are generated by using reconfigured ASIC.These technicalmethods have been applied in practical engineering successfully.

software-defined radio;DDR receiver;function reconfiguration;IF digitization

?收的數字中頻波形 Fig.2

digital intermediate frequency wave

TN802;TN911

A

10.3969/j.issn.1001-893x.2011.08.014

李燕春(1969—),男,北京人,2004年獲電子科技大學信號處理專業碩士學位,現為工程師,主要研究方向為通信系統終端設備設計。

1001-893X(2011)08-0066-04

2011-03-31;

2011-07-01

LIYan-chun was born in Beijing,in 1969.He received the M.S.degree from University of Electronic Science and Technology of China in 2004.He is now an engineer.His research concerns the design of communication system terminal equipment.

Email:qulifine@hotmail.com