可變參數(shù)數(shù)據(jù)采集控制電路的FPGA實(shí)現(xiàn)

李 媛,王 暢,郭建新,劉尚峰③

(①空軍工程大學(xué) 電訊工程學(xué)院,陜西 西安 710077;②華北水利水電學(xué)院,河南 鄭州 450011;③空軍雷達(dá)學(xué)院,湖北 武漢 430019)

0 引言

數(shù)據(jù)采集處理技術(shù)是現(xiàn)代信號處理的基礎(chǔ),廣泛應(yīng)用于雷達(dá)、通信、遙測遙感等領(lǐng)域。隨著信息科學(xué)的飛速發(fā)展,人們面臨的信號處理任務(wù)愈來愈繁重,對數(shù)據(jù)采集處理系統(tǒng)的要求也愈來愈高[1]。數(shù)字采集卡[2]是現(xiàn)代數(shù)字通信接收機(jī)和信號分析處理的常用設(shè)備,其基本功能就是對接收到的模擬信號進(jìn)行受控采樣,獲得滿足要求的數(shù)字信號。常用的數(shù)據(jù)采集方案往往采用單片機(jī)(MUC)或數(shù)字信號處理器(DSP)作為控制器,以控制模數(shù)轉(zhuǎn)換器(AD)、存儲器和其他外圍電路的工作,但因單片機(jī)自身指令周期及處理速度的影響,很難達(dá)到多通道高速數(shù)據(jù)采集系統(tǒng)的要求,雖然 DSP可以實(shí)現(xiàn)較高速的數(shù)據(jù)采集,但在提高其速度的同時(shí),也增加了系統(tǒng)成本[3]。由于FPGA[4]技術(shù)具有工作頻率高,設(shè)計(jì)靈活,可編程性好,適合于時(shí)序、組合邏輯電路應(yīng)用等特點(diǎn),使得FPGA在實(shí)現(xiàn)數(shù)據(jù)采集上有著不可比擬的優(yōu)勢。基于FPGA平臺,運(yùn)用VHDL語言[5]設(shè)計(jì)并實(shí)現(xiàn)數(shù)據(jù)采集控制電路系統(tǒng),最大限度地提高信號采集和處理能力。

1 設(shè)計(jì)需求

系統(tǒng)的設(shè)計(jì)需求如下:

①采樣率:20 MHz和20.32 MHz可選,通過外部選擇信號控制;

②采樣位寬:12 bits;

③采樣開始條件:支持軟件軟觸發(fā)和外部硬觸發(fā);

④采樣批次控制:通過控制可以實(shí)現(xiàn)一次采1、2、4、8或16批數(shù)據(jù);

⑤采樣深度控制:每一批深度可分別為128、256、512、1024、2048、4096、8192、16384。

⑥采樣時(shí)延控制:接收到采樣開始命令后,要延時(shí)規(guī)定時(shí)間才能進(jìn)行采樣,延時(shí)時(shí)間為 16、32、64、128、512、1024、2048、4096個采樣時(shí)間。

2 實(shí)現(xiàn)方案

2.1 系統(tǒng)組成與總體流程

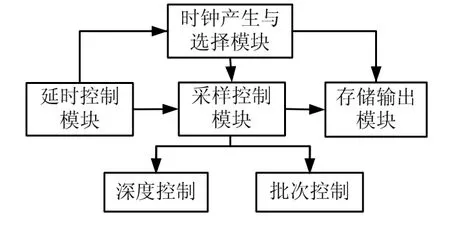

采用自頂向下的設(shè)計(jì)思路,將控制電路各功能對應(yīng)到各個具體設(shè)計(jì)模塊,將系統(tǒng)劃分為以下4個模塊:時(shí)鐘產(chǎn)生與選擇模塊、延時(shí)控制模塊、深度和批次控制模塊、存儲輸出模塊。其組成如圖1所示。

圖1 系統(tǒng)組成

其中,時(shí)鐘產(chǎn)生與選擇模塊的主要功能是對外部輸入的2個時(shí)鐘信號源進(jìn)行選擇,并輸出其中一個作為整個控制系統(tǒng)的主時(shí)鐘;時(shí)延控制模塊的主要功能是接收到觸發(fā)脈沖后,對其進(jìn)行規(guī)定時(shí)長延遲處理后,輸出使能信號至采樣深度和批次模塊;深度和批次控制模塊的主要功能是在時(shí)延控制模塊使能信號的控制下,按照規(guī)定深度和批次對信號進(jìn)行采樣,并產(chǎn)生寫地址、讀地址和存儲輸出使能控制信號至存儲和輸出控制模塊;存儲和輸出模塊的主要功能是在深度和批次控制模塊寫地址、讀地址和存儲輸出使能信號的控制下,對輸入采樣信號進(jìn)行緩存和輸出。

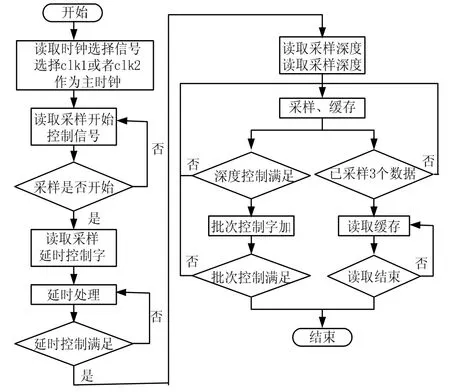

系統(tǒng)工作流程如圖2所示,可歸納為4步。①讀取時(shí)鐘選擇信號,進(jìn)行主時(shí)鐘選擇;②等待采樣觸發(fā)信號,收到,系統(tǒng)跳入下一步,否則等待;③讀取采樣延時(shí)控制字,并延時(shí)處理,滿足控制要求跳入下一步,不滿足則繼續(xù)延時(shí)處理;④讀取采樣深度和批次控制字,對輸入信號進(jìn)行采樣、緩存、讀取處理,滿足控制要求停止操作轉(zhuǎn)入初始等待狀態(tài),不滿足則繼續(xù)處理。需要指出的是,存儲操作和讀取操作之間有3個時(shí)鐘差,外部表現(xiàn)為RAM存儲操作第3個采樣數(shù)據(jù)后,讀取操作開始。

2.2 各模塊實(shí)現(xiàn)方案

2.2.1 時(shí)鐘產(chǎn)生與選擇模塊

該模塊在設(shè)計(jì)時(shí)采用模塊庫中的ALTCLKCTRL元件。其工作原理是通過時(shí)鐘選擇器通過電平變化控制20 MHz和20.32 MHz時(shí)鐘輸出。

2.2.2 延時(shí)控制模塊

延時(shí)控制模塊的工作原理是接收到采樣使能信號后,通過比較器對計(jì)數(shù)結(jié)果與延時(shí)控制字進(jìn)行比較后,到達(dá)延時(shí)規(guī)定時(shí)間時(shí)產(chǎn)生采樣開始使能信號,并輸出至后續(xù)模塊,延時(shí)時(shí)間為16、32、64、128、512、1024、2048、4096 個采樣時(shí)間。

圖2 系統(tǒng)總體流程

2.2.3 深度和批次控制模塊

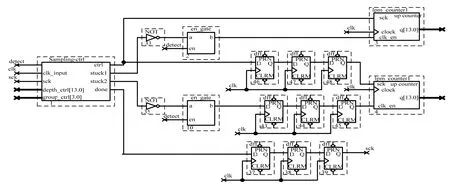

如圖3所示是深度和批次控制模塊的設(shè)計(jì)原理圖,可看到該模塊由深度和批次控制部分、寫地址產(chǎn)生器、讀地址產(chǎn)生器3部分組成。

圖3 深度和批次控制模塊

深度和批次控制部分由非門、D觸發(fā)器、“sampling_ctrl”和 “en_gate”塊構(gòu)成。現(xiàn)對“sampling_ctrl”4 個輸出端口的功能進(jìn)行簡要說明:①“ctrl”:當(dāng)完成1個批次的采樣后,輸出一個脈沖,對地址產(chǎn)生器進(jìn)行清零。完成全部批次采樣后,保持高電平“1”;②“stuck1”:經(jīng)過非門和“en_gate”處理,產(chǎn)生寫計(jì)數(shù)器和寫存儲器的使能信號“wren”;③“stuck2”:經(jīng)過非門、“en_gate”和延遲處理,產(chǎn)生讀計(jì)數(shù)器和讀存儲器的使能信號“rden”;④“done”:采樣結(jié)束后,產(chǎn)生清零脈沖,輸出至延時(shí)計(jì)數(shù)、地址計(jì)數(shù)、存儲輸出等模塊。

地址產(chǎn)生器,利用模塊庫中的LPM_COUNTER元件,將時(shí)鐘、使能和清零信號“ctrl”分別接入對應(yīng)端口,實(shí)現(xiàn)對存儲輸出模塊的地址選擇。

2.2.4 存儲輸出模塊

該模塊采用模塊庫中的LPM_RAM_DP元件,其工作原理是在寫地址、讀地址和存儲讀取使能信號的共同控制下,對端口輸入的采樣數(shù)據(jù)進(jìn)行緩存和讀取輸出。

3 實(shí)驗(yàn)驗(yàn)證

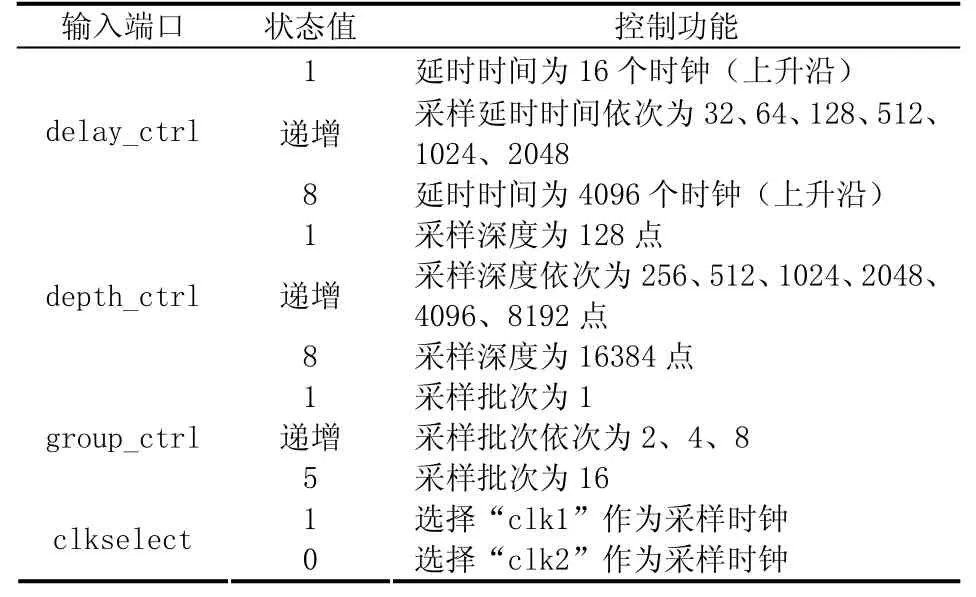

采用Quartus Ⅱ[6]Simulator進(jìn)行時(shí)序仿真和功能驗(yàn)證。如表1所示。

表1 主要控制端口功能說明

通過對上述控制端口的選項(xiàng)進(jìn)行逐個測試,時(shí)序仿真結(jié)果均滿足預(yù)定的各項(xiàng)要求。

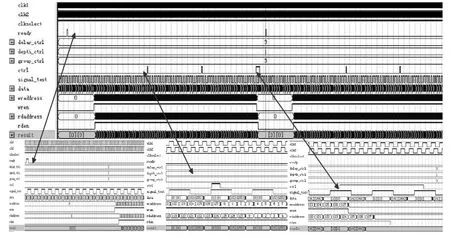

現(xiàn)選擇時(shí)鐘“clk1”,延時(shí)64個時(shí)鐘、深度控制128點(diǎn)、批次控制3為例進(jìn)行仿真驗(yàn)證。結(jié)果如圖4所示,在對“ready”觸發(fā)脈沖進(jìn)行 64個時(shí)鐘延遲后,采樣控制電路對測試信號進(jìn)行采樣存儲操作,經(jīng)過3個時(shí)鐘的延遲處理后,對存儲的采樣數(shù)據(jù)進(jìn)行同步讀取。

在每批次完成后,寫地址和讀地址計(jì)數(shù)器分別進(jìn)行清零操作,值得注意的是由于讀地址計(jì)數(shù)器計(jì)數(shù)開始時(shí)間稍晚于寫地址計(jì)數(shù)器,故其清零也較寫地址計(jì)數(shù)器有所延遲。最后,在所有采樣緩存、讀取操作完成后,各控制端口收到清零信號,恢復(fù)等待狀態(tài)。

圖4 系統(tǒng)時(shí)序仿真驗(yàn)證

對其他參數(shù)做了相應(yīng)仿真驗(yàn)證,實(shí)現(xiàn)了此控制電路的各項(xiàng)功能,限于篇幅,不再贅述。

4 結(jié)語

基于FPGA平臺,采用原理圖設(shè)計(jì)輸入和硬件描述語言設(shè)計(jì)輸入相結(jié)合的方式,實(shí)現(xiàn)了可變參數(shù)數(shù)字采集器的多采樣率、多深度、多批次以及多采樣時(shí)延控制功能。電路的設(shè)計(jì)提高了數(shù)據(jù)采集的直觀可控性,參數(shù)調(diào)節(jié)方便,有重要的應(yīng)用價(jià)值,進(jìn)一步可增加其他如顯示、繪圖、打印的功能并可實(shí)現(xiàn)可視化的人機(jī)界面。實(shí)際測試和應(yīng)用表明,可廣泛應(yīng)用各種過程控制和自動化過程中。

[1] 牛國朋,袁洪,范建軍.一種基于FPGA和DSP的高性能PCI數(shù)據(jù)采集處理卡設(shè)計(jì)[J]. 《微計(jì)算機(jī)信息》(嵌入式與 SOC)2006(22):137-139.

[2] 朱志亮,邱紹峰.基于FPGA的STM-1數(shù)據(jù)采集卡的硬件設(shè)計(jì)[J].通信技術(shù),2007,40(11):262-264.

[3] 王永水,任勇峰,焦新泉.基于FPGA的160路數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)[J].國外電子元器件,2008(10):4-5.

[4] 樂健,陳紹偉,吳婷婷.基于FPGA的PCI接口的設(shè)計(jì)與實(shí)現(xiàn)[J].信息安全與通信保密,2010(05):41-43.

[5] 姜立東.VHDL語言程序設(shè)計(jì)及應(yīng)用 [M]. 第2版.北京:北京郵電大學(xué)出版社,2004:152-168.

[6] 褚振勇 齊亮.FPGA設(shè)計(jì)與應(yīng)用 [M].第2版.西安:西安電子科技大學(xué)出版社,2006:139-179.