基于DSP Builder的自適應濾波器的模型搭建

孟莎莎,董會寧,董 健

(重慶郵電大學 應用物理研究所,重慶 400065)

0 引言

飛速發展的數字信號處理技術(DSP,Diginal Signal Processing)在通信、醫學、圖像處理、多媒體系統、便攜式電子設備中得到了廣泛的應用。

在過去的一段時間內,DSP處理器是DSP應用系統核心器件的唯一選擇,DSP Processor主要是指目前最常用的基于CPU架構的器件,通過軟件指令的方式完成DSP算法[4]。近年來DSP器件在硬件結構上不斷改進,性能有了很大的提高,但是并沒有擺脫傳統CPU的工作模式。DSP處理器的靈活性只是表現在軟件更改的容易性以及對各種算法的處理和復雜算法的實現上,而對于系統硬件本身的更改,DSP是沒有任何靈活性可言的。

現代大容量、高速度的FPGA能夠克服DSP處理器的諸多不足,在這些FPGA中,一般都內嵌有可配置的高速RAM、PLL、LDVS、LVTTL以及硬件乘法器等DSP模塊。FPGA做為數字信號處理的新硬件平臺,在并行性和速度問題上突顯出獨特的優勢,而且其靈活的可重構特性,使用FPGA搭建DSP系統非常易于實現、易于測試及硬件升級。

Altera推出的 DSP Builder工具箱提供了一個從MATLAB/Simulink直接到FPGA硬件實現的設計接口。它極大地簡化了DSP功能的硬件實現流程,并提供了系統級仿真測試功能,并且DSP Builder提供模塊化的門電路,使得算法更容易實現,這樣就能極大地縮短開發周期。

本文在DSP Builder軟件平臺上,搭建了一個以四階濾波器模塊為基礎的自適應濾波器,該濾波器通過級聯,可以簡單地轉換為8階、12階、16階等的自適應濾波器,通過Simulink模擬仿真,驗證了該設計的的合理性,為硬件的實現打下了基礎。

1 自適應濾波算法的選取

自適應濾波器是指能夠根據環境的改變,使用自適應算法來改變自身濾波器參數和結構的濾波器[3]。它一般由2部分組成:①是濾波器模塊;②是濾波器系數更新模塊,即自適應算法模塊。對于自適應算法的選取一般從2個方面考慮:①是算法的復雜度;②是算法的收斂性。

在自適應濾波器的設計中,自適應算法的選取尤其重要,算法的選取一般從兩個方面進行考慮,一個是自適應算法的復雜度,一個是算法的收斂性能[6]。

由Widrow和Hoff提出的最小均方誤差(LMS)算法,因其具有結構簡單、計算量小、魯棒性強、易于實現等優點而在硬件設計中被廣泛采用。該算法的計算公式描述如下:

(1) FIR濾波器運算

(2) 濾波器系數計算

根據LMS算法的計算公式,建立一個LMS算法復雜度表,如表1,設濾波器的長度為L,那么LMS算法在一次迭代中只需要2L+1乘法和2L次加法,也就是說LMS算法的復雜度為O(L),與濾波器的階數L呈線性增長。計算復雜度低是LMS一個顯著有點,因此LMS算法在實際中得到廣泛應用奠定了基礎。

表 1LMS算法復雜度

自適應算法的收斂性一般由參數μ決定,LMS算法簡單,只有一個參數μ,因而必須選擇合適的μ,來保證算法的收斂性。另外μ還是控制收斂速度穩態誤差的常量,選擇大的μ可以產生很快的收斂速度,但是當收斂到維納解附近后將在一個比較大的領域內抖動而無法進一步收斂;選擇較小的步長可以收斂到維納解附近的小領域,但是它的收斂速度是非常緩慢的。這就是LMS算法的一個明顯弱點:高速收斂和小穩態誤差不可兼得,而調和此矛盾的參量就是步長因子μ。為了保證算法收斂性,對步長因子的穩定邊界定義如下:

其中maxS是輸入()xn的功率譜密度的最大值。

2 算法的模塊劃分

在本設計中,把自適應濾波器劃分為幾個獨立的模塊,這樣可以保持各個模塊的相對獨立性,若要改變自適應算法,只需要改變算法模塊即可,其它的模塊可以不變,并且各個模塊的恰當分割大大地增加了系統的靈活性,有利于硬件實現。

根據自適應LMS算法的計算公式,把計算分為了FIR濾波器運算和濾波器系數計算兩步,相應地,把自適應濾波器的結構劃分為橫向FIR濾波器模塊和濾波器系數更新模塊,即自適應算法模塊,如圖1所示為給出的2個模塊的結構圖。因為輸出誤差計算模塊只有一個加法運算,那么可以把這個加法運算合并到其它的2個模塊進行建模。

圖1 自適應濾波器的分割結構

3 基于DSP Builder的建模

DSP Builder是Altera公司推出的一個面向DSP開發的系統工具。它是作為Matlab/Simulink的一個工具箱出現的。DSP設計可以方便地利用Simulink與DSP Buider提供的豐富的功能塊和IP核進行設計。DSP Buider包括比特和周期精度的 Simulink模塊,還涵蓋了諸如算法和存儲功能基本模塊以及 IP庫中的許多復雜的功能模塊。電路中的功能塊和 IP的技術參數、數據格式和總線寬度都可以直接設置。電路模型設計完成后,可以進行系統功能仿真。仿真通過后可以運行Signal Compiler,將模型轉化成RTL級的VHDL代碼和Tcl腳本語言。調用QuartusⅡ進行編譯,QuartusⅡ根據網表文件及設置的優化約束條件進行布線布局和優化設計的適配,最后生成編程文件和仿真文件。

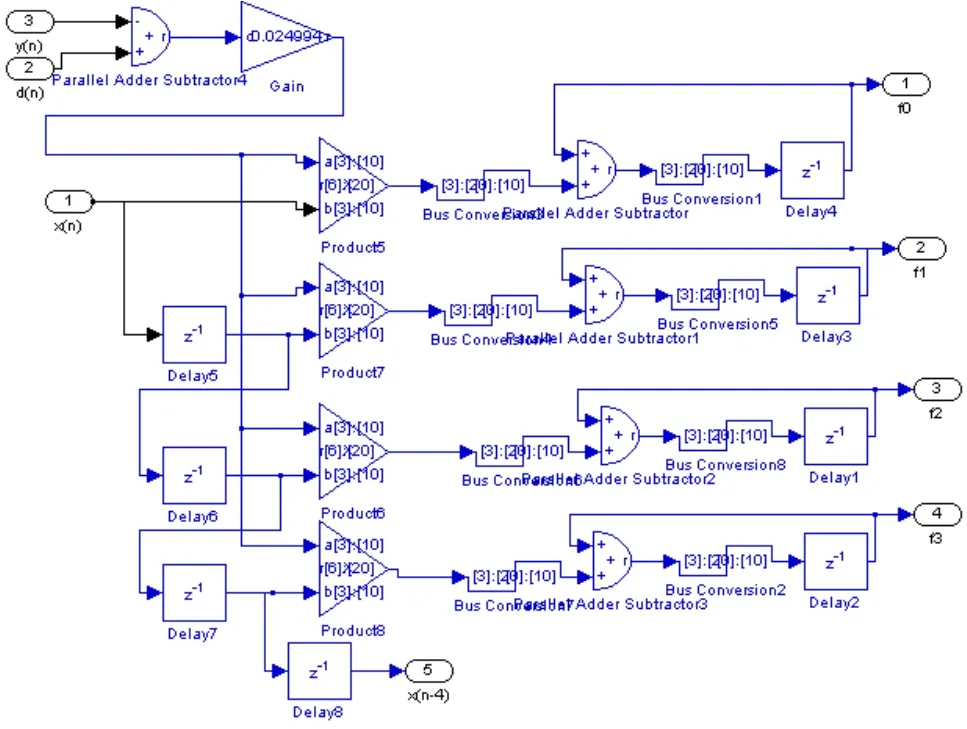

通過上面的自適應濾波器結構和自適應濾波算法的分析,可知該設計有大量的乘法、加法和延遲算法,那么在Matlab的Simulink工具箱DSP Buider模塊組里面,調出設計所需的乘法器、加法器、延遲單元,還有總線控制模塊,完成頂層設計。用以完成算法級到功能級的實現。

鑒于以上的設計,需要對 DSP Buider中的幾個模塊進行說明:

①Product:乘法器;

②Parallel Adder Subtractor:加法器;

③Gain:增益模塊;

④Bus Coversion:總線類型轉換模塊;

⑤Dalay:延遲單元。

根據模塊劃分思想,進行模型搭建,設計一個四階的濾波器模塊和一個四階的濾波器系數更新模塊。在實際應用中,低階數的濾波器往往很難達到合理的濾波器效果,所以對設計的模塊封裝,那么再進行模塊級聯,就可以調整濾波器的系數,靈活地實現8階,12階,16階及更多階的自適應濾波器。如圖 2所示,為一個四階為單元組合而成的 16階的自適應濾波器設計圖,其中子模塊4fir為四階FIR濾波器模塊,子模塊l ms為4階系數調整模塊。通過子模塊間的級聯,建立一個16階的自適應濾波器。圖3為自適應算法子模塊的結構圖。設定時鐘信號周期為 20 ns,輸入信號是在正弦信號的疊加一個隨機噪聲信號 1,參考信號為一個和隨機噪聲信號1相關的噪聲信號2,步長因子μ設定為0.025。開始Simulink模型仿真,其仿真結果如圖4所示,第一條輸出波形為正弦信號和隨機噪聲的疊加,第二條波形為誤差號的輸出,第三條波形為輸出信號。

由此得出結論:

①輸出信號達到了比較理想的效果;

②誤差信號得到了收斂,且收斂速度較快。

圖2 16階自適應濾波器的結構

圖3 系數調整模塊結構

圖4 自適應濾波器仿真

4 結語

本文基于DSP Builder設計軟件,完成了自適應濾波器的模型搭建,這樣的設計流程,包括從系統描述直至硬件實現,可以在一個完整的設計環境中完成,同時構成了一個自定而下的典型的設計流程。通過仿真,驗證了設計的合理性,并且模塊劃分的思想使設計簡單易行,極大地縮短了開發周期,并且Simulink所具有的圖形界面也能幫助提高開發效率。

使用DSP Builder工具箱可以明顯地提高數字信號處理系統的開發效率,并且設計者可以不必懂硬件描述語言,也能進行DSP系統的硬件開發。DSP Builder應用于數字信號處理有很高的應用價值。

[1] 李昕,李艷,李波. DLMS濾波器的 FPGA實現[J]. 元器件與應用,2009,21(09):41-46.

[2] 張銀行,楊小雪. 子帶分解的自適應濾波器的 FPGA實現[J]. 現代電子技術, 2010,33(08):13-18.

[3] 袁江南,徐敏. 基于DSPBuilder的LMS自適應濾波器設計[J]. 計算機應用 2009, 29(12):338-340.

[4] 楊東,王建業,蔡飛. 基于DSP開發工具的自適應濾波器[J].探測與控制學報, 2010,6(08):67-70.

[5] DAVIS B. Adaptive Noise Cancellation Using LMS and Optimal Filtering[J]. University of Florida. 2003,13(09): 23-30.

[6] 秦志強,張水蓮,孫萍. 階數可變的成形濾波器FPGA實現[J]. 通信技術,2009,42(03):261-265.

[7] 王云,李惠光,隋明森. 模糊LMS算法主從濾波器的設計及應用[J].通信技術,2009,42(05):74-76.

[8] 邵寧,陳萬培,陳俊晟. 一種基于維納濾波器抗MAI的新方法[J].通信技術,2010,43(05):134-138.