基于FPGA的視頻采集與顯示系統設計

李江輝,王景存

(武漢科技大學 信息科學與工程學院,湖北 武漢 430081)

責任編輯:任健男

0 引言

如今視頻監控領域迅速發展,各種格式的視頻信號需要在不同的媒體上播放,而各種播放媒體普遍較貴,并且各種播放媒體采集和傳輸的視頻、音頻信號的格式不盡相同,在眾多的顯示媒體之間還沒有一個統一的標準接口來實現音、視頻信號的顯示和播放。筆者設計了一種PAL轉VGA接口的視頻信號傳輸與顯示控制器,簡單地實現了一種顯示格式到另一種顯示格式的轉換。

1 系統方案設計

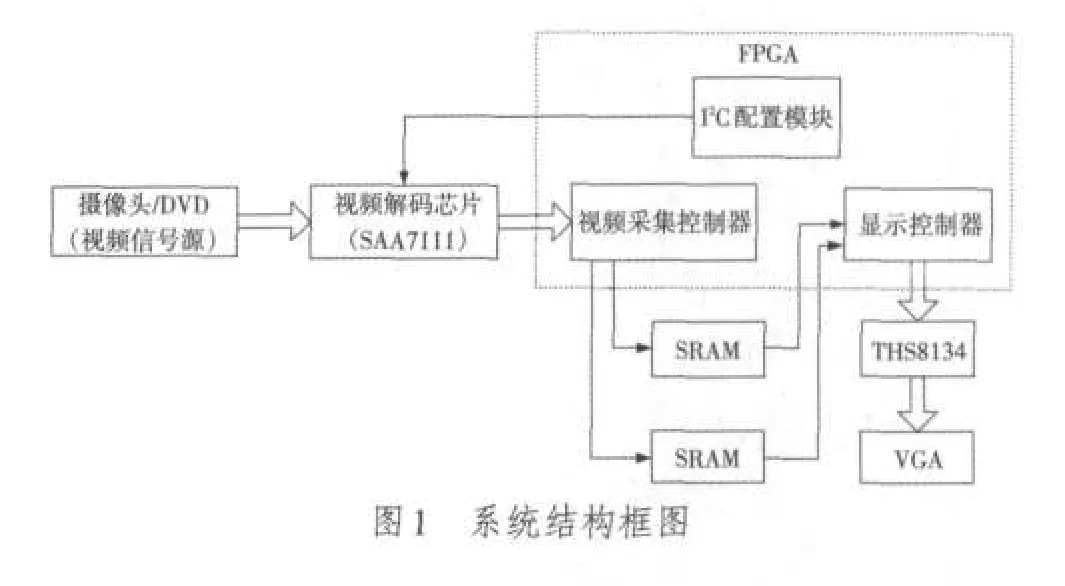

本系統是基于FPGA的視頻顯示系統,不僅具有攝像頭或DVD視頻信號采集功能,還具有視頻格式轉化和實時顯示功能。首先在FPGA內部設計I2C配置模塊來配置片外SAA7111[1],攝像頭/DVD輸出的模擬視頻信號經過SAA7111后得到RGB格式的數字信號,視頻采集控制器采集到該數字信號后,送入片外的2片SRAM進行乒乓操作來完成幀頻,顯示格式的轉換,顯示控制器讀取SRAM中的數據送入THS8134進行D/A變化,從而形成完整的數據流。D/A變化后的數據送入CRT顯示器實時顯示。系統結構框圖如圖1所示。

2 視頻信號采集與存儲

2.1 I2C配置模塊

由于視頻解碼芯片SAA7111需要合理配置后才能完成視頻數據的采集和相應格式的數據輸出。對其配置即是對其片內寄存器進行設置,它具備I2C總線接口,有32個控制寄存器,其中20個可編程。窗口大小、A/D轉化速度、幀/場模式等參數都可以在工作過程中對相應的寄存器進行設置,從而實現對SAA7111的實時控制。

在對SAA7111進行配置時需要注意,寫完一個字節后,一定要等應答后開始下一個字節。用I2C總線配置SAA7111時,系統時鐘頻率不能太快,如果太快會使SAA7111來不及響應。一般系統時鐘頻率采用400 kHz,配置可靠。I2C總線的時鐘與數據要嚴格按時序的邏輯編寫。在開始與停止時,時鐘高電平間數據可以變化;在傳送數據時,時鐘高電平期間數據不能發生變化。SAA7111初始化流程圖如圖2所示。

2.2 視頻采集模塊

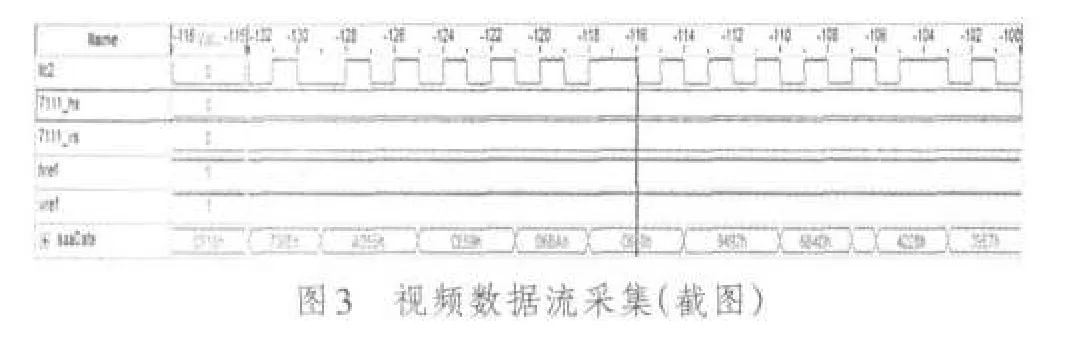

SAA7111通過I2C配置模塊初始化完成后,FPGA便可以采集到SAA7111輸出的像素時鐘、行同步、場同步、16 bit RGB信號、行參考、場參考、奇偶場識別等信號。視頻數據流采集如圖3所示。

其中,llc2為SAA7111輸出的像素時鐘,且llc2為13.5 MHz,SAA7111在該像素時鐘的節拍下輸出像素點的RGB數據信號。7111_hs為輸出視頻流的行同步信號,7111_vs為場同步信號,href為行參考,vref為場參考信號,saaData即為16 bit RGB數據信號,R∶G∶B=5∶6∶5格式,并且該視頻流的分辨力為720×572。

2.3 視頻幀合成模塊

PAL制式視頻信號具有隔行掃描的特性,因此采集的視頻數據被分為奇數場和偶數場,而在實時顯示的CRT顯示器是需要完整的視頻幀[2-5]。所以需要將奇偶場的視頻數據進行合成。當一幀開始時,首先是第1,3,5行等奇數行的數據進行緩存,然后在第2,4,6行等偶數行的數據采集進來時,結合奇場數據,根據PAL視頻數據格式合成幀數據,如此便能形成完整的視頻幀用于處理。1幀數據由2個部分組成:偶場地址=基地址E+偏移地址E;奇場地址=基地址O+偏移地址O。視頻幀合成如圖4所示。

本設計中通過行列計數器按照完整視頻的數據格式,產生地址計數,然后將這些地址計數送到SRAM的地址總線上,這樣就可以在采集視頻的時候,實時地將每一個采樣數據送入到SRAM中進行存儲,保證數據的完整性。實質上就是對每一個視頻數據通過行列計數器分配了唯一的地址,然后通過這些地址從SRAM中對視頻數據進行讀寫,而僅僅是在FPGA內部對數據進行了地址編碼,這樣就大大節省了FPGA內部資源,同時也提高了系統的實時性。

2.4 SRAM乒乓操作模塊

乒乓操作處理流程可以描述為:輸入數據流選擇單元等時地將數據流分配到兩個數據緩沖模塊;而數據緩沖模塊可以是任何的存儲模塊,雙口RAM、單口RAM和FIFO均可以用來進行數據緩沖。把乒乓操作模塊當作一個整體,從這個模塊的兩端看數據流,輸入數據流和輸出數據流都是連續不斷的,沒有任何停頓,因此它非常適合本設計中視頻流不間斷的要求。

將上述由奇場、偶場合成的每一幀視頻數據存入到SRAM的同時,為保證視頻流不間斷,就要完成幀與幀之間的交替。因為每一幀都對應一個SRAM的讀寫,所以幀與幀之間的交替變化為2個SRAM之間讀寫的切換。本設計中設置了1個狀態變量enable,當enable為0時寫SRAM1,同時讀 SRAM2;當enable為1時 讀 SRAM1,同 時 寫SRAM2。當然 enable的初值為0,其他是根據幀頻變化中是否完成了讀SRAM所要求的1.2個計數周期,不斷取反得到。圖5為乒乓操作控制流程圖。

3 D/A及顯示控制模塊

因為本設計中采用CRT顯示器作為顯示輸出,要在該顯示屏上連續顯示一幀一幀的圖像,需要按照標準的VGA接口規范來控制時序。而VGA接口上主要包括了行同步、場同步、RGB三基色信號。并且VGA接口上的行同步、場同步是數字信號,FPGA可以直接控制,而該接口上的RGB三基色信號是模擬信號,所以FPGA從片外SRAM讀出的視頻流需要經過幀頻及分辨力變化,D/A轉化后才能送到VGA接口上顯示。

3.1 幀頻及分辨力變化

該攝像頭輸出PAL制式圖像,規定場頻為50 Hz,圖像的分辨力為720×572,而本設計用的VGA接口標準為800×600@60 Hz。不同的格式顯示,需要進行幀頻和分辨力的變化。幀頻變化具體實現:當SRAM進行乒乓操作時,當向進行寫操作的SRAM寫入1幀原始信號時,從另一個SRAM讀出數據,完成當前幀輸出后再從進行寫操作的SRAM首行起讀出數據(多讀0.2個計數周期),開始新一幀輸出。即讀SRAM行地址計數器從原值繼續計至行最大值后再從0開始重新計數。共完成寫SRAM 1個計數周期,讀SRAM 1.2個計數周期后,再進行SRAM的讀寫切換。每經過5次這樣的乒乓操作切換(1個循環),便能完成幀頻變換。

而對于分辨力的變換,因為分辨力增加后,每場行數增加,每行像素點也增加,故每場需要產生新的行數據,每行需要產生新的像素值。而采用均勻插值的方式,即對原始信號中的某些行進行重復讀取,對所有行的某些像素進行重復讀取,可以很好地完成分辨力的變化。

3.2 VGA控制模塊

該模塊從乒乓操作的SRAM中讀出處理好的數據以后,需要按照VGA接口的時序送到THS8134。這里的時序需要產生行同步、場同步信號(即CRT顯示器的消隱信號)。另外要在非消隱期將處理好的視頻數據送出去。其中clk1為時鐘,rst為復位信號,daa為從SRAM讀入的數據,da為輸出的數據,hs1和vs1為行場同步信號。圖6為VGA接口控制時序圖。

3.3 D/A變化

THS8134芯片為TI公司主要應用于圖像方面的D/A芯片。THS8134的ths_m1和ths_m2用于配置輸入圖像的數據格式,該芯片可以配成輸入4種不同的數據格式,分 別 為 RGB 3x8b-4∶4∶4;YPbPr 3x8b-4∶4∶4;YPbPr 2x8b-4∶2∶2和YPbPr 1x8b-4∶2∶2。本系統輸入的圖像數據格式為RGB 3x8b-4∶4∶4格式。而ths_blank用來控制輸出消隱,ths_sync_t控制三電平同步的正同步頭寬度,ths_sync控制D/A輸出信號同步的寬度。THS8134配置模塊如圖7所示。

由于THS8134每次接收24 bit數據再進行D/A,在該模塊中還需要將VGA模塊輸出的16 bit RGB轉化為24 bit RGB。在本設計中采用低位補零的方法來實現的。即當輸入格式R∶G∶B=5∶6∶5時,給R,G,B總線的低位分別補3 bit的0、2 bit的0、3 bit的0即可。該方法雖不是很精確,但可以滿足本系統設計要求。

4 小結

本設計以FPGA為核心,實現了PAL轉VGA接口的視頻流顯示。詳細介紹了隔行轉逐行,幀頻、分辨力轉化,SRAM讀寫,乒乓操作等方法。實驗驗證,該設計實時顯示效果良好,設計簡單,具有較高的實用價值。

[1]SAA7111 Enhanced Video InputProcessor(VIP)[EB/OL].[2010-10-20].http://www.datasheetdir.com/SAA7111+Video.

[2]夏宇聞.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2007.

[3]劉凌.數字信號處理的FPGA實現[M].北京:清華大學出版社,2002.

[4]徐洋,黃智宇.基于Verilog HDL的FPGA設計與工程應用[M].北京:人民郵電出版社,2009.

[5]龍在云,武斌.DVI數字視頻圖像數據的實時截取方法[J].電視技術,2010,34(2):32-33.