基于OMAP-L138處理器的AD模塊設計

梁 龍,翟守忠,李富偉

(長沙礦山研究院, 湖南長沙 410012)

0 引言

2009年德州儀器(TI)推出了具有無與倫比連接選項和浮點功能的OMAP-L138處理器,它構建于工作頻率為300 MHz的TMS320C6748處理器和ARM9處理器基礎之上的雙內核處理器,適用于全面外設接入;并且擁有很低的功耗,在不同使用情況下總功耗為440 mW,待機模式功耗為15 mW。但OMAP-L138處理器內部未集成模擬數字轉換器(ADC),需外擴ADC芯片實現模擬信號的采集。

ADS8556是一款6路16位逐次逼近寄存器型(SAR)ADC,具有真正的雙極輸入。每路包含了采樣保持電路,允許同時對多路模擬信號進行高速采集,其并行接口模式的數據速率高達630 kSPS,總線寬度8~16位可選;串行接口模式數據速率高達500 kSPS。ADS8556的工作電壓±12 V,具有高達91.5 dB 的信噪比(SNR)。

1 系統總體框圖設計

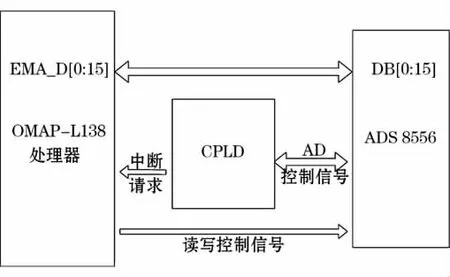

ADS8556利用OMAP-L138處理器的DSP端的外部存儲器接口(EMIFA)實現6路模擬信號采集。輸入通道分為3個組(分別為A0、A1,B0、B1,C0、C1),且每組可并行采集信號,每個通道的轉換都由獨立的轉換開始信號控制。由于CPLD的時序嚴格,速度較快等優點,AD模塊的控制信號選擇用可編程器件CPLD XC95144編譯產生,系統結構見圖1。

2 硬件電路實現

2.1 電源模塊設計

圖1 系統總體框架

在電源電路設計方面,由于OMAP-L138處理器的DSP端內核電壓為1.2 V,IO口電壓為3.3 V。ADS8556需要4個獨立的供電電源,分別為:5 V的ADC的模擬供電(AVDD)電壓,用于ADC內部供電;3.3 V的數字IO接口的供電(BVDD)電壓,用于驅動IO緩沖器;DSP內核電壓1.2 V及±15 V模擬輸入的高壓供電(HVDD和HVSS)電壓,由外部±15 V電源直接供電。選用TI的具有兩個降壓轉換器和3個低輸入電壓LDO的5通道電源管理芯片TPS65053,最多可實現5路電壓輸出。設置其電壓范圍上限均為5 V,分別輸出1.2 V、3.3 V、3.3 V_RTC及1.8 V(供給外圍器件),如圖2所示,降壓轉換器及3路LDOs的輸入電壓都連接到+5 V電壓,并與地之間需接1 μF去耦電容。輸出根據分壓原理對R1~R8選擇合適的電阻值。

2.2 ADC模塊硬件接口電路設計

圖3為基于ADS8556芯片的ADC模塊硬件接口設計電路,其中將引腳PAR/SER和HW/SW置為低電平,實現并行模式下的信號采集;數據總線DB[0∶15]連接到處理器OMAP-L138的EMIFA數據端,實現數字轉換結果的輸出;BUSY/INT作為AD中斷信號經 CPLD輸出到 OMAP-L138的GPIO口,實現對模擬信號采集的控制;ADS8556使能內部參考電壓源,對每一路信號提供緩沖參考電壓。

圖2 電源供電原理

圖3 AD模塊接口電路

3 軟件設計

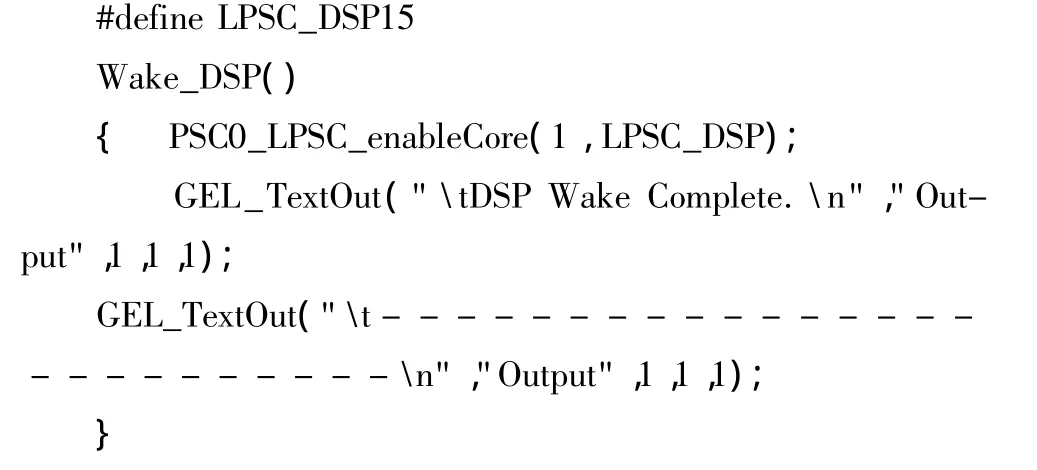

3.1 喚醒程序

設計OMAP-L138作為一種快速、低功耗的處理器,由于其特殊的結構,DSP端必須在需要時由ARM喚醒,通常DSP端處于睡眠狀態。所以,首先要編寫一段鏈接程序從ARM端喚醒DSP。OMAP-L138處理器具有統一的管理外設和CPU供電的模塊(PSC模塊),PSC0的PD1用來控制DSP的L1和L2存儲器的休眠狀態。喚醒子程序如下:

其中PSC0_LPSC_enableCore為LPSC中使能DSP的子函數,即給DSP上電。

3.2 主程序設計

對AD采樣使用中斷控制方式,在編寫中斷控制子程序之前需配置相應的中斷控制寄存器及處理器對應引腳的功能。具體軟件模塊如下。

(1)初始化模塊,OMAPL138_init;OMAPL138RAM_init;EMIFA_init;AD_init。其中 OMAPL138的初始化實現Power and Sleep控制器的設置及時鐘的配置;RAM初始化模塊實現SDRAM的初始化及其上電,時鐘的配置;EMIFA初始化配置了AD模塊數據總線與地址總線及相關的控制總線;AD模塊初始化開啟AD中斷,等待中斷信號。

(2)EDMA3配置模塊(DMAconfig)。將GP2[0]作為DSP對AD中斷信號的接受端,則GPIO中斷使能寄存器BINTEN的bit2=1;使能GP2[0∶15]的中斷請求信號,復位相關寄存器。

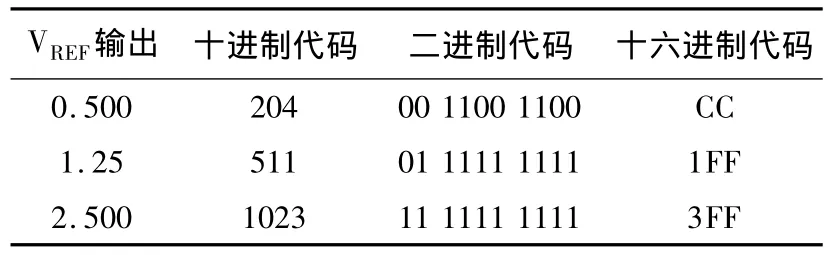

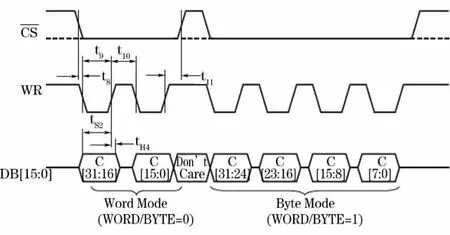

(3)AD測試模塊(TEST_ad),將參考電壓選為2.5 V,其 CR(控制寄存器)默認為 0x000003FF,如表1所示。并行接口模式下控制寄存器的改變在WR的上升沿有效。并行接口模式下從模擬通道讀數據和給CR控制寄存器寫入數據的時序邏輯如圖4和圖5。ADS8556在整個轉換周期中CONVST_x應當始終保持為高電平,且每個通道組的模擬輸入在對應的CONVST_x信號的上升沿保持,在讀模式下,片選端CS為低電平時,在RD每個下降沿開始讀取數據,6個周期讀取6通道的數據。在寫模式下,以字方式寫入時,在每個WR的下降沿先寫入高16 位(C[31∶16]),再寫入低 16 位(C[15∶0]),在WR信號的2個周期內完成;當以字節方式寫入,在每個WR的下降沿寫入8字節,完成一次寫入需要4個周期。

表1 DAC設置(2.5 V)

測試程序流程如圖6所示。

4 試驗結果及分析

通過實驗,當輸入為300 Hz、±10 V的方波和鋸齒波信號時,其幅值誤差在±0.1 V范圍內,頻率誤差在±1 Hz范圍內,具體見表2。

圖4 并行模式讀時序

圖5 并行模式寫時序

圖6 程序流程

用集成ARM與DSP的雙核處理器OMAP-L138和多通道A/D轉換器ADS8556組成了并行AD轉換功能模塊,采樣速度快(最高可達630 ksps),實時性能好,精確度高(與實際模擬信號幅值誤差1%,頻率誤差0.3%),并且可完成多路模擬信號的同時采集。

表2 試驗結果及分析

[1]Texas Instruments.OMAP - L138 data sheet[Z].June 2009.

[2]Texas Instruments.ADS8556 data sheet[Z].August 2009.

[3]Texas Instruments.TMS320C674x DSP Cache[Z].February 2009.

[4]谷重陽,汪 渤,龍殊穎.并行模數轉換器 ADS8364與TMS320F2812 的接口設計[J].微計算機信息,2006,(1).

[5]張雄偉,陳 亮,徐光輝.DSP芯片的原理與開發應用(第3版)[M].北京:電子工業出版社,2003.