一種基于FPGA實現(xiàn)的改進語音端點檢測算法

歐陽玲,宋 克

(1.中原工學(xué)院,鄭州 450007;2.國家數(shù)字交換系統(tǒng)工程技術(shù)研究中心,鄭州450002)

一種基于FPGA實現(xiàn)的改進語音端點檢測算法

歐陽玲1,宋 克2

(1.中原工學(xué)院,鄭州 450007;2.國家數(shù)字交換系統(tǒng)工程技術(shù)研究中心,鄭州450002)

介紹了一種基于FPGA硬件實現(xiàn)的語音端點檢測算法,該算法以短時平均能量和短時平均過零率為基礎(chǔ),具有硬件實現(xiàn)簡單、資源占用量低、檢測效果良好等特點;給出了算法的流程與硬件實現(xiàn)模塊,以及采用FPGA綜合和仿真的結(jié)果.

FPGA;語音端點檢測;短時平均能量;短時平均過零

在語音信號系統(tǒng)中,數(shù)字語音信號是由語音、靜音和各種背景噪音混合組成的.在這種信號中將語音和各種非語音信號時段區(qū)分開來,準確地確定出語音信號的起止點,被稱為端點檢測.語音信號的端點檢測在語音信號處理中非常重要.實驗表明,端點檢測是否準確對語音信號的識別率具有非常重要的影響;另外,準確地檢測出語音信號的端點還可以減少后續(xù)處理的計算量,提高芯片的處理能力.

端點檢測的算法很多,如基于自相關(guān)極大值、基于小波變換、基于頻帶方差、基于倒譜特征、基于信息熵、基于 HMM等等端點檢測算法[1],然而這些算法由于算法復(fù)雜、計算量大、實時性差,很難應(yīng)用于ASIC硬件實現(xiàn).本文介紹一種改進的基于短時平均能量和短時平均過零率的端點檢測算法,并將其在ASIC上實現(xiàn),性能良好.

1 算法描述

基于短時平均能量和短時平均過零率的端點檢測算法是一種基于時域的語音端點檢測方法.其基本思想是采用測試信號的短時能量或短時對數(shù)能量、聯(lián)合過零率等特征參數(shù)及雙門限判定法來檢測語音端點[2],即利用過零率檢測清音,用短時能量檢測濁音,兩者相配合.首先為短時能量確定2個門限[3]:一個是較低的門限,數(shù)值較小,對信號的變化比較敏感,短時能量比較容易超過該門限,但當(dāng)短時能量超過低門限時,測試信號未必是語音的開始,有可能是很短的噪聲引起的,這時需要配合過零率來判斷是否是語音幀;另一個是比較高的門限,數(shù)值較大,當(dāng)短時能量超過高門限時,則直接判定語音信號為語音幀.

整個端點檢測可分為4段:靜音段、過渡段、語音段、結(jié)束.在靜音段,如果短時能量超過低門限且過零率超過門限值,或者短時能量超過高門限,就開始標記起始點,進入過渡段;在過渡段,如果連續(xù)3幀語音被判定為語言幀,即認為進入語音段,否則,將當(dāng)前狀態(tài)恢復(fù)到靜音段;在語音段,如果短時能量超過低門限但過零率未超過門限值,或者短時能量低于低門限,就開始進入過渡段,如果連續(xù)3幀語音被判定為靜音幀,即認為語音結(jié)束,否則,將當(dāng)前狀態(tài)恢復(fù)到語音段,繼續(xù)檢測下一幀語音數(shù)據(jù).

2 算法實現(xiàn)與流程

定義幀平均幅度(短時能量):

為第n幀語音信號的平均幅度;n為幀的編號;N為每幀的點數(shù).

定義幀語言信號的短時平均過零率:

Zj為幀語音信號的短時平均過零率.

首先,為幀平均幅度確定2個門限:一個是較低的門限(AL),數(shù)值較小,對信號的變化比較敏感,很容易被超過;另一個是比較高的門限,數(shù)值較大(AH).當(dāng)幀平均幅度超過低門限時,進行過零率檢測,超過高門限時直接判定為語言幀.

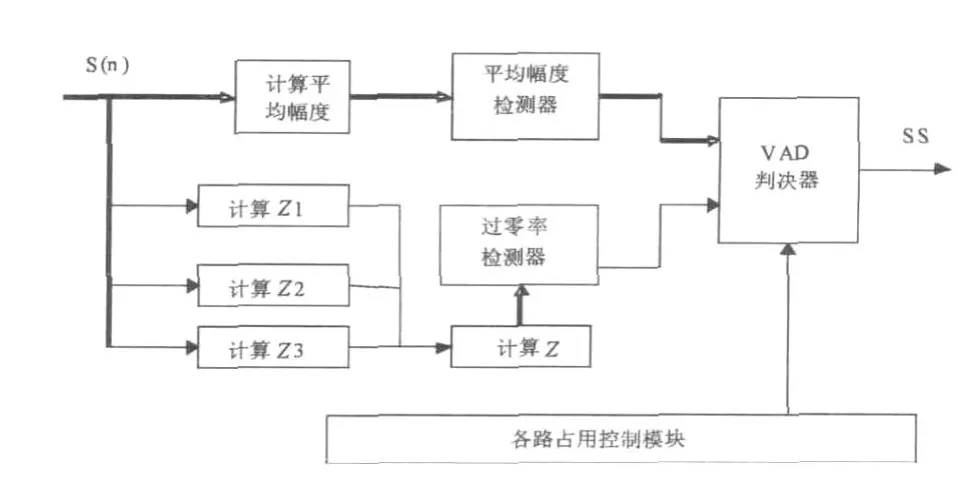

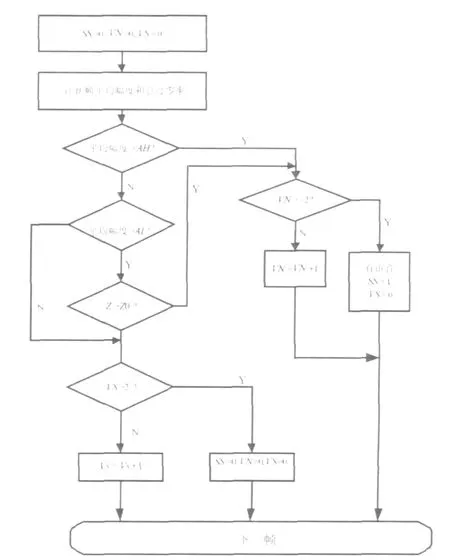

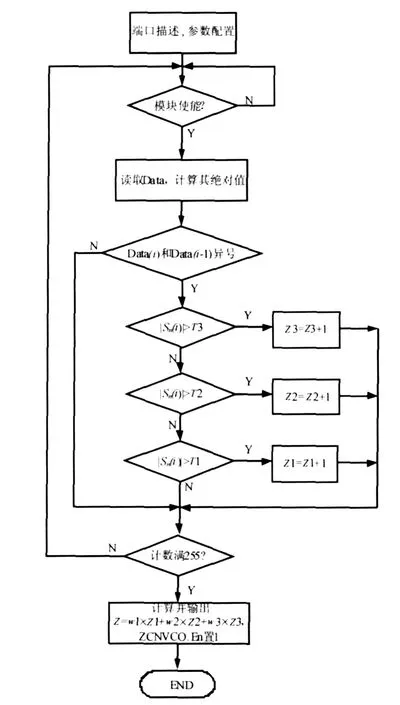

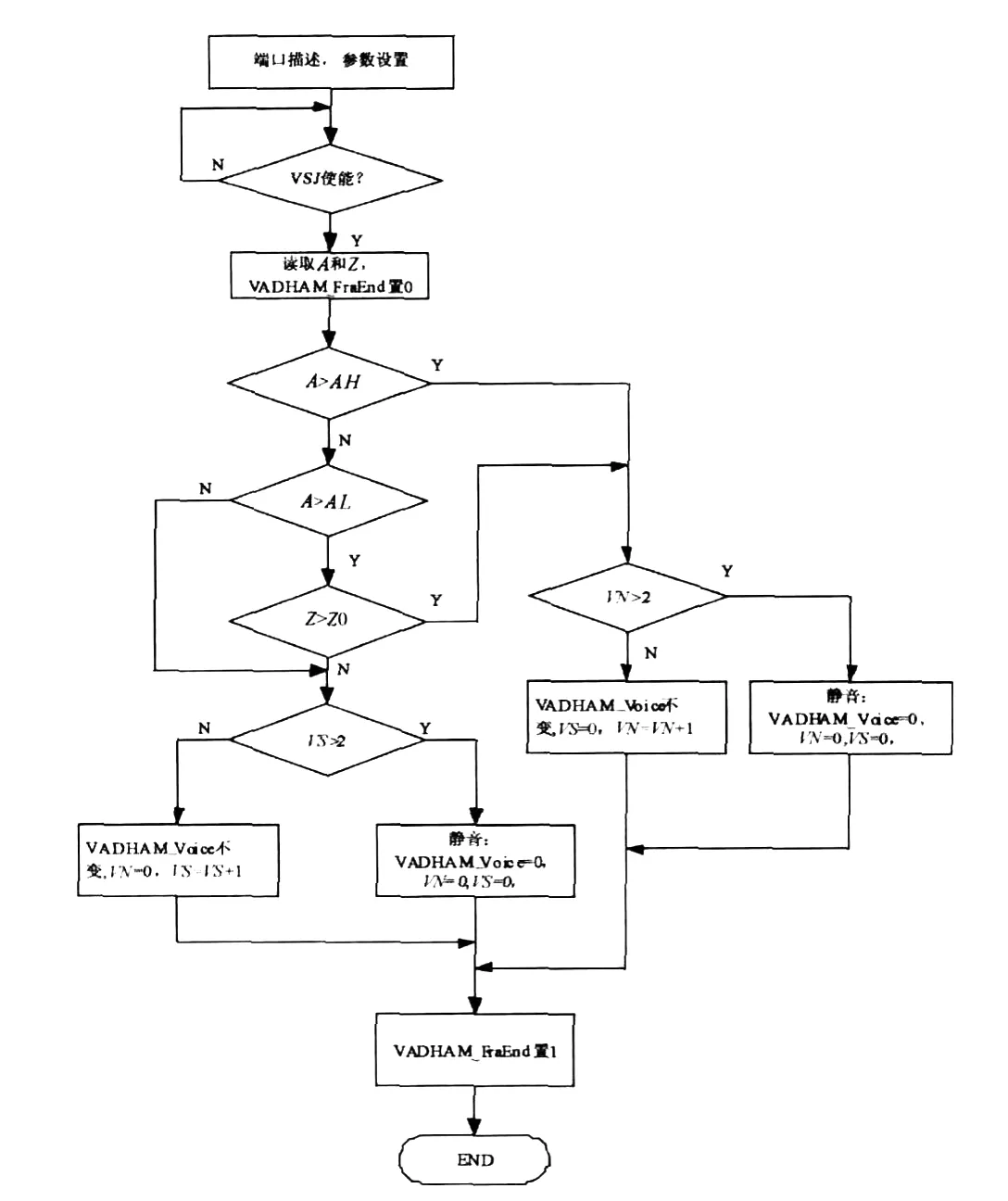

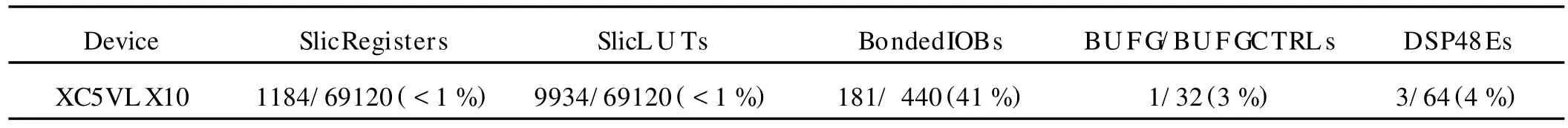

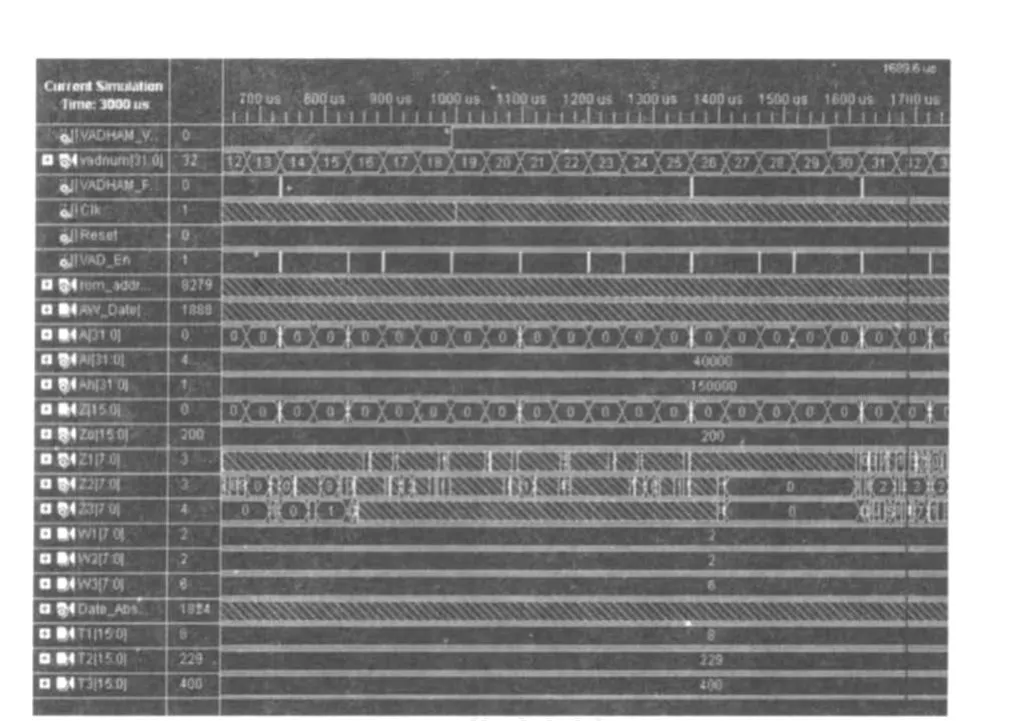

其次,定義3個短時平均過零率門限T1、T2、T3,T1 只要門限值T1、T2、T3和權(quán)值w1、w2、w3選得合適,語音幀信號的Z值明顯大于靜音幀的Z值.通過試驗找出一個分界值Z0,當(dāng)Z>Z0時,判定該幀為語音幀;當(dāng)Z 算法實現(xiàn)框圖和流程圖分別如圖1和圖2所示. 其中:SS=0,表示靜音;SS=1,表示語音;VN為連續(xù)檢測記錄是語音的幀數(shù);VS為連續(xù)檢測記錄是非語音的幀數(shù). 圖1 算法實現(xiàn)框圖 圖2 算法實現(xiàn)流程圖 本設(shè)計的輸入為每幀256點16位的有符號語音數(shù)據(jù),分別計算每幀語音數(shù)據(jù)的平均幅度(為簡便起見,這里采用幅值和代替)和幀短時平均過零率.然后根據(jù)計算結(jié)果和設(shè)定的各門限值按照一定的規(guī)則進行判決,輸出每幀語音信號的檢測結(jié)果(靜音或語音).硬件結(jié)構(gòu)框圖如圖3所示: 圖3 FPGA硬件結(jié)構(gòu)圖 當(dāng)VAD使能信號有效時,計數(shù)獲取每幀256點語音數(shù)據(jù),計算每點語音數(shù)據(jù)的幅值(絕對值),并進行累加.當(dāng)每幀256點數(shù)據(jù)處理完成,產(chǎn)生該幀幅值后,送給VSJ模塊并置位ARC完成信號. 輸入信號:Data(0:15)(16位語音信號);Start(VAD使能信號);CLK100M(工作時鐘);RESET(復(fù)位信號). 輸出信號:A(幀幅度值);ARCVCO_En(ARC完成信號,當(dāng)該信號為1時,使能下一級操作). 當(dāng)VAD使能信號有效時,計數(shù)獲取每幀256點語音數(shù)據(jù),計算過零率Z(Z=w1×Z1+w2×Z2+w3×Z3).當(dāng)每幀256點數(shù)據(jù)處理完成,產(chǎn)生該幀過零率后,送給VSJ模塊并置位ZCN完成信號. 輸入信號:Data(0:15)(16位語音信號);Start(VAD使能信號);CL K100M(工作時鐘);RESET(復(fù)位信號);T1、T2、T3、w1、w2、w3(16位門限值). 輸出信號:Z(過零率);ZCNVCO_En(ZCN完成信號,使能下一級操作).該模塊流程如圖4所示. 圖4 ZCN模塊算法流程圖 將ARC和ZCN模塊輸出的幀數(shù)據(jù)處理完成的信號進行與操作,生成VSJ模塊使能信號,然后進行判決. 輸入信號:ARCVCO_En(ARC完成信號,使能下一級操作);ZCNVCO_En(ZCN完成信號,使能下一級操作). 輸出信號:VCOVSJ_En(VSJ使能信號). 讀取每幀語音數(shù)據(jù)幅值和過零率,判斷該幀是否為語音,并根據(jù)最近3幀的判決結(jié)果輸出語音/靜音判決信號及VAD幀處理完成信號. 輸入信號:A(幀幅度值);Z(過零率);AL、A H、Z0(32/16位門限值);VCOVSJ_En(VSL使能信號);CL K100M(工作時鐘);RESET(復(fù)位信號). 輸出信號:VADHAM_Voice(有無語音標志,VADHAM_Voice=1,表示有語音;VADHAM_Voice=0,表示靜音);VADHAM_FraEnd(VAD幀判決完成信號). 該模塊流程如圖5所示. 圖5 VSJ模塊算法流程圖 采用Xinlix公司的Virtex-5系列FPGA對本算法的設(shè)計實現(xiàn)進行綜合,綜合工具為ISE10.1.03,得到的結(jié)果如表1所示. 表1 FPGA硬件資源占用率 由表1可以看出,本算法的設(shè)計在硬件上占用的資源較少,因此可以很容易地與其他數(shù)字語音處理模塊一起構(gòu)成完整的語音處理芯片. 為驗證本算法的檢測結(jié)果,特選取如下一段實際語音進行仿真測試,其中標記部分為有話幀(18幀到28幀),其余均為噪聲,如圖6所示. 圖6 實際語音波形圖 仿真結(jié)果如圖7所示,其中檢測為有話幀是19幀到29幀,其余為無話幀. 圖7 語音端點檢測仿真波形圖 本文介紹了一種基于短時平均能量和短時平均過零率的端點檢測算法的硬件實現(xiàn)方法. 通過仿真,可以看出該設(shè)計可以較好地實現(xiàn)話音信號中的噪音分辨,能夠作為預(yù)處理部分的端點檢測模塊,應(yīng)用于各種語音處理芯片的設(shè)計. [1]王炳錫,屈丹,彭煊.實用語音識別基礎(chǔ)[M].北京:國防工業(yè)出版社,2005:265-269. [2]李祖鵬,姚佩陽.一種語音段起止點端點檢測新方法[J].電訊技術(shù),2000(3):68-71. [3]徐大為,吳邊,趙建偉,等.一種噪聲環(huán)境下的實時語音端點檢測算法[J].計算機工程與應(yīng)用,2003(1):115-117. A Improved Algorithm of VAD Based on FPGA Realizing OU YANG ling,SONG Ke This paper introduces a kind of Voice Activity Detection(VAD)algo rithm based on FPGA realizing.The algorithm that based on short-term average energy and short-time average zero-crossing rate,has the virtuesof simp le hardware imp lementation,low resources use and good detection effect.The algorithm p rocess and the realization of hardwaremodulesand FPGA comp rehensive and simulation resultsare given in the paper. FPGA;VAD;sho rt-term average energy;sho rt-time average zero-crossing rate TN912 A 10.3969/j.issn.1671-6906.2011.01.019 1671-6906(2011)01-0070-04 2011-01-20 歐陽玲(1978-),女,安徽池州人,講師,碩士.

3 算法硬件實現(xiàn)模塊

3.1 幅值計算模塊ARC

3.2 過零率計算模塊ZCN

3.3 控制信號模塊VCO

3.4 語音/靜音判決模塊VSJ

4 FPGA綜合與仿真結(jié)果

5 結(jié) 語

(1.Zhongyuan University of Technology,Zhengzhou 450007;2.China National Digital Sw itching System Engineering&Technology R&D Center,Zhengzhou 450002,china)