基于實時數字信號處理的寬帶單比特瞬時測頻接收技術

王坤達

(船舶重工集團公司723所,揚州 225001)

0 引 言

傳統的瞬時測頻(IFM)接收機瞬時帶寬寬,測頻時間短,動態范圍寬,但是由于其體制原因靈敏度進一步提升潛力受限,同時到達信號適應能力較差(同時到達的2個輸入信號功率相差較近,不能正確測量)。模擬信道化接收機具有較高的靈敏度,且具備一定的同時到達信號處理能力,但是要做到寬的瞬時帶寬(例如2~10 GHz),則無論其設備量、體積、重量、造價都難以承受。而傳統的數字化接收機雖然具有較高的靈敏度和良好的復雜信號適應能力,但是其瞬時帶寬受到限制,大量復雜的數學運算導致其實時信號處理壓力較大,信號測量時間較長。如果要實現大的瞬時帶寬,只有通過多通道拼接來覆蓋全頻段。若采用多個窄帶多位模數轉換器(ADC)去拼接來滿足大的瞬時帶寬,除了龐大的數據采樣電路,還需要配備龐大的微波變頻電路。此時其體積、重量、功耗、成本代價都相當高。為實現寬帶瞬時帶寬、高靈敏度和實時信號處理(適應高信號密度)等主要性能,同時還必須考慮體積、重量、功耗等因素,筆者提出了基于實時數字處理的寬帶單比特瞬時測頻接收技術。

1 系統組成

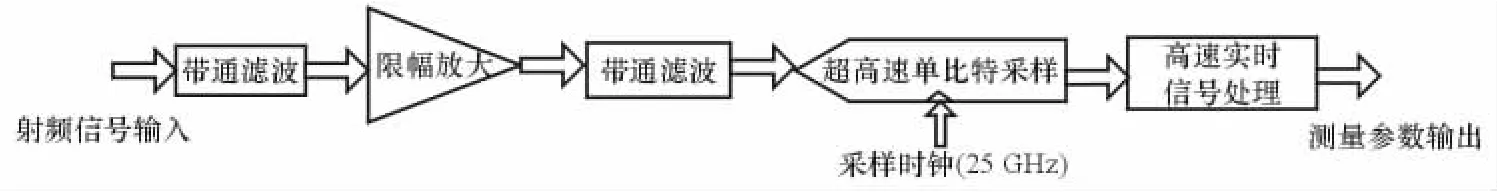

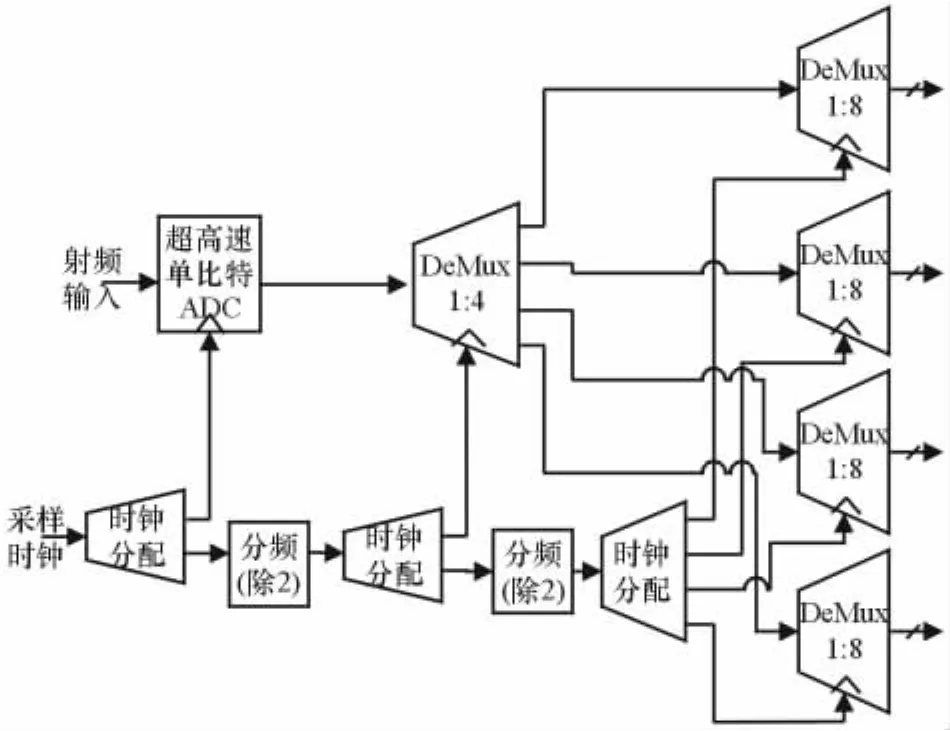

系統組成示意框圖如圖1所示。

超高速單比特采樣電路的采樣率為25 GHz,輸入射頻信號瞬時帶寬覆蓋2~10 GHz。射頻信號經帶通濾波、限幅放大后,通過超高速單比特采樣電路實現對寬帶射頻信號的超高速采樣,憑借高效快速的寬帶數字瞬時測頻算法和高速實時信號處理硬件平臺,完成對信號的快速實時測量。

圖1 系統組成示意框圖

2 寬帶數字瞬時測頻算法構成

圍繞大帶寬高速采樣的實時快速處理,寬帶數字瞬時測頻算法主要由單比特接收算法、滑動FFT算法、瞬時頻率測量算法構成。

2.1 單比特接收算法

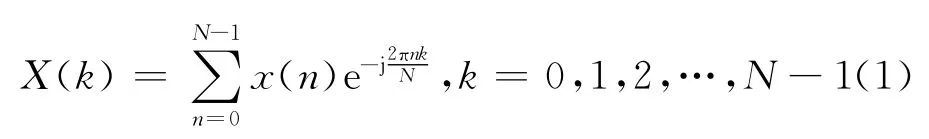

最早提出單比特接收算法的目的是通過消除FFT過程中的乘法運算來降低FFT硬件實現的復雜性。一個簡單的消除乘法運算的方法就是使用1位的ADC,產生的輸出只有±1(對應位的1、0態),即FFT的輸入數據只有+1和-1 2種情況。離散博里葉變換(DFT)可以表示為:

式中:x(n)為輸入數據;為Kernel函數。

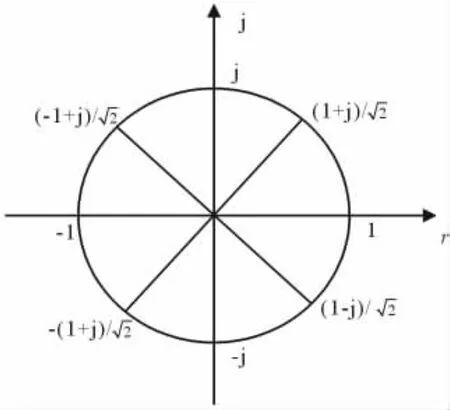

如果輸入x(n)為±1,則輸入數據與Kernel函數之間就不需進行乘法運算。如果FFT只需要作加法和減法,則所需的運算復雜度大大降低。另一種避免FFT進行乘法運算的途徑是把Kernel函數的比特數減到1。Kernel函數是一個復函數,因此它不能用1位的實數來表示。表示Kernel函數最簡化的方法是用1位表示實部,l位表示虛部。數學上可以表示為:

Kernel函數的值可以等于式(2)中4個值中的1個。在這種條件下,FFT運算也無需乘法。

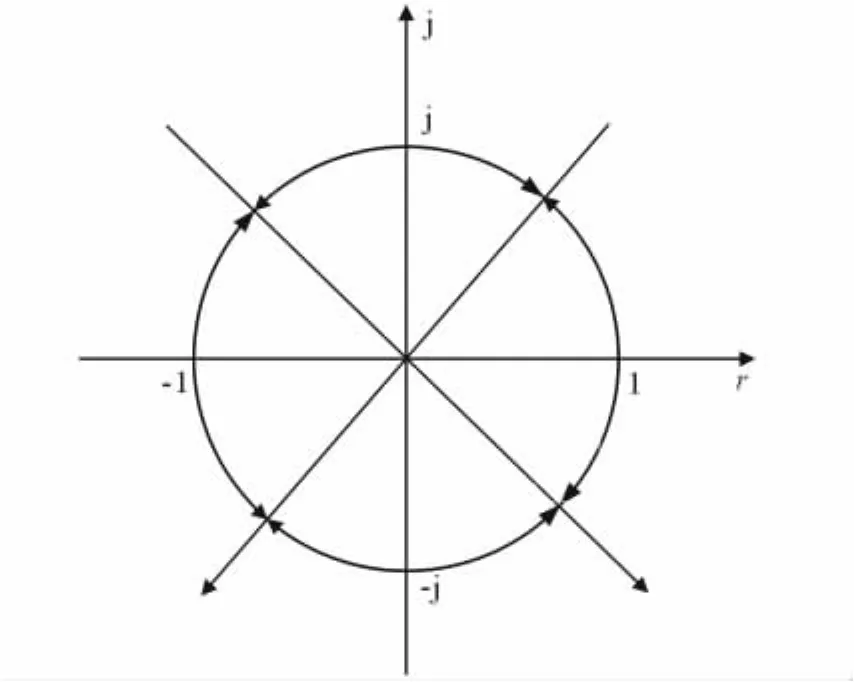

Kernel函數的取值分布在復平面的單位圓上,如圖2所示。Kernel函數的取值從1開始,并且相鄰2點之間間隔2π/N角度,這里N為FFT的點數。圖2表示的是N=8時的情況。在圖3中,Kernel函數的取值采用1位表示實部,1位表示虛部,則可以認為Kernel函數在7π/4≤θ<π/4范圍內的值量化為1;在π/4≤θ<3π/4范圍內的值量化為j;在3π/4≤θ<5π/4范圍內的值量化為-1;在5π/4≤θ<7π/4范圍內的值量化為-j。

圖2 N=8時FFT的Kernel函數

最終通過減少運算復雜度達到提升硬件處理能力,從而實現瞬時計算的目的。由于單比特量化的非線性,單比特接收機存在較高的旁瓣電平,Kernel函數取值的適當增加對單比特接收機頻率響應中的旁瓣電平抑制有一定的改善作用。基于FFT的各種算法(例如基2和基4算法)以及分裂基算法都很成熟,這里就不再贅述。

這里要特別指出的是,本方案之所以采用單比特接收算法而沒有用數字信道化算法處理是因為,雖然數字信道化處理方式在多位ADC輸入處理領域有著較大的優勢,但在單比特輸入信號的處理上并不具有優勢,原因如下:

圖3 實部和虛部都量化成1位的Kernel函數

(1)單比特信號本身的量化過程是一個強非線性過程,該過程中所產生的交調和諧波(及諧波的折疊鏡像)較多,與輸入信號之間的頻率關系沒有規律可循,如這些信號和原信號處于一個信道,對原信號測頻和信號檢測的影響較大,嚴重時可能無法正常工作。

(2)數字信道化的信道帶寬的選取比較困難,如選擇較少的信道,每個信道的后處理將需要大量的邏輯,無論是在時域還是在頻域,所消耗的邏輯資源將與直接使用單比特FFT沒有優勢可言;如選擇較多的信道,資源的消耗同樣較大,與單比特處理同樣沒有優勢;因此超高速單比特ADC前端采用了單比特FFT算法。

2.2 滑動FFT算法

對數字信號的檢測方法常見的有時域檢測和頻域檢測2種。時域檢測實時性好,消耗硬件資源少。頻域檢測的主要優點是:作用于大量數據點上的FFT可以把信號從噪聲中提取出來。缺點是要進行大量FFT運算。鑒于單比特接收算法簡化蝶形運算中的乘法運算為加法運算,大大減少了資源消耗,以及本接收機方案中的寬帶數字瞬時測頻過程本身就需要對采樣數據進行并行、流水構架的FFT算法,系統擬采用滑動FFT頻域檢測完成對信號包絡的檢測。

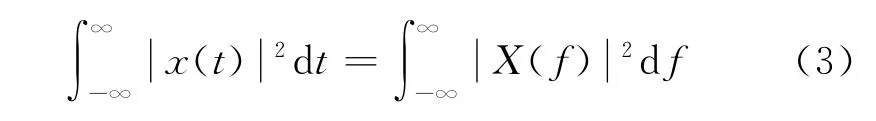

對于脈沖調制雷達信號而言,在脈沖到達之前,采樣獲得的信號是偵察接收機的熱噪聲。一般認為接收機的熱噪聲是白噪聲。傅里葉變換的帕斯瓦爾(Parseva1)定理指出,給定一個信號x(t),時域總能量等于頻域總能量,這一關系可以寫成:

式中:X(f)為信號x(t)的傅里葉變換。

數字信號處理中,所分析的雷達信號都是經過采樣量化后的離散時間序列。若x(n)是信號x(t)經采樣量化后的離散時間序列,且X(n)是x(n)的離散傅里葉變換,則帕斯瓦爾定理可以寫成:

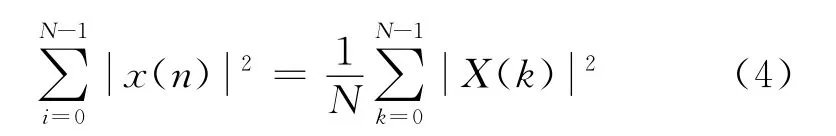

根據這一原理,下面闡述系統提取脈沖包絡方法。設如圖4所示的N點離散時間序列x(n)包含一個雷達脈沖。不失一般性,設脈沖在第k點到達,則對x(n)計算M點數據的滑動FFT,對每次滑動FFT結果,按照式(4)計算其頻域總能量。根據帕斯瓦爾定理,信號的時頻域能量守恒。則在第0點至第k-1點之間,脈沖沒有到達,序列中沒有脈沖存在,其頻域能量主要體現為熱噪聲能量En。在第k點至第k+M-1點之間,用于計算滑動FFT的序列中脈沖不斷積累,直到包含全部脈沖。在第k+M點以后至脈沖下降沿到達前,用于計算滑動FFT的序列中總是包含脈沖。通過滑動FFT計算得到的頻域總能量就是一條雷達脈沖信號的功率譜密度變化曲線。

圖4 滑動FFT原理示意圖

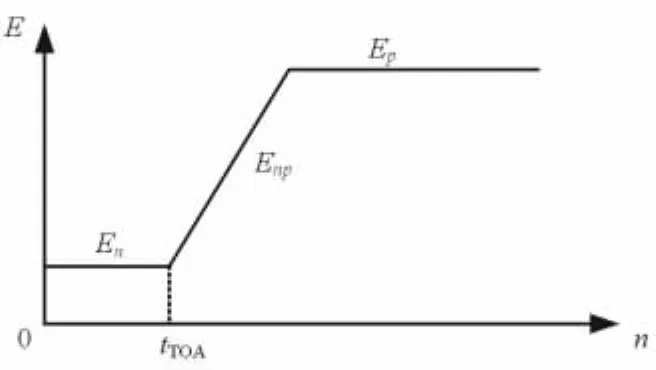

對于單頻脈沖來說,其功率譜密度變換曲線如圖5所示。脈沖到達時間(TOA)就是圖5所示拐點的對應時間。

圖5 脈沖到達時間計算原理

圖5中,En為噪聲頻域能量;Enp為脈沖到達期間用于計算滑動FFT序列的頻域能量;Ep為脈沖和噪聲的頻域能量。

當然,為滿足實時處理,不可能對采樣數據逐點進行滑動FFT運算,滑動的點數和FFT的長度需要結合系統的各項指標以及硬件特性等綜合考慮。通過采用單比特接收算法并結合滑動FFT算法,能夠滿足對超高速單比特采樣模塊輸出的高速采樣信號進行實時流水快速測量的要求。

2.3 瞬時頻率測量算法

瞬時頻率測量算法可以對FFT得到的頻率值做進一步的精估計,瞬時頻率測量法與模擬IFM接收機的原理類似,FFT的結果含有此時輸入信號的瞬時相位信息,2次滑動FFT的時間間隔是固定的,則通過瞬時相位差就能得到此時的瞬時頻率,數學表達如下:

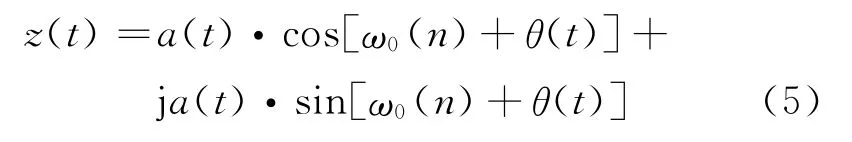

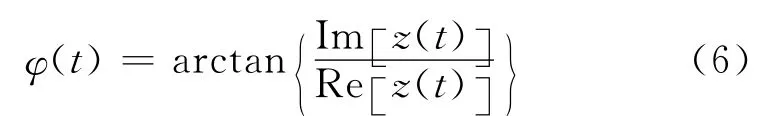

一個信號的復解析形式為:

式中:Re[z(t)]=a(t)·cos[ω0(n)+θ(t)],為信號的實部(信號的同相分量ZI(t));Im[z(t)]=a(t)·sin[ω0(n)+θ(t)],為信號的虛部(正交分量ZQ(t))。

瞬時相位表達式為:

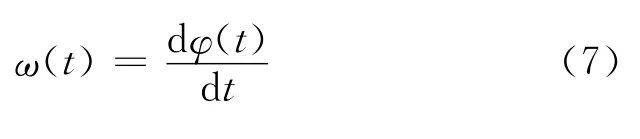

瞬時角頻率為:

3 硬件實現

3.1 超高速單比特采樣

超高速單比特采樣通過采樣頻率為25 GHz的時鐘信號對輸入頻帶為2~10 GHz的射頻輸入信號進行不間斷的連續采樣,最終通過同步降速處理,將超高速串行數據流轉換成后級處理模塊能夠適應的高速并行數據流(數據率為781.25 MHz的32路并行數據)。圖6為超高速單比特采樣模塊示意圖。

高速單比特采樣模塊設計要充分考慮其傳輸線效應和信號完整性等問題,盡量避免或減小板間各種信號之間的干擾和相互“污染”。為盡可能降低板上時鐘頻率,降速器件(De Mux)均工作在雙沿采樣(DDR)模式。整個印制電路板(PCB)設計過程借助有效的電磁仿真軟件達到信號完整性要求。

對超高速單比特采樣電路進行實測數據聯合仿真分析是必不可少的。因為單比特ADC相當于一個限幅器,輸入信號的幅度信息受到損失,是非線性器件。實際的量化噪聲,虛假響應很難進行準確估算,再加之同時出現多信號情況下會顯示出來捕獲效應(所謂捕獲效應就是強信號會抑制弱信號,這種效應同時還會在頻域上產生很多諧波分量,使頻域檢測容易虛警);所以,在進行設計時需要對實際量化數據進行采集,把采集數據輸入到計算機中進行處理,以便得到對超高速單比特采樣電路的性能評估,從而為后級信號檢測模塊中的第1級信號檢測門限選擇提供依據。

圖6 超高速單比特采樣模塊示意圖

3.2 高速實時信號處理

結合指標要求,該系統選擇基于現場可編程門陣列(FPGA)的方案實現寬帶數字瞬時測頻算法。

目前用FPGA實現的FFT處理器結構大致分為4種:遞歸結構、級聯結構、并行結構和陣列結構。遞歸結構只利用一個蝶形運算單元對數據行規律的循環計算,使用硬件資源較少,但運算時間較長;級聯結構每級均采用一個獨立的蝶形運算單元來處理,相對遞歸結構速度上有所提高,不足之處是增加了延時用的緩存器使用量;并行結構對一級中的蝶形單元并行實現,陣列結構是將每級的蝶形運算單元全部并行實現。考慮到系統算法輸入數據的大位寬、并行快速數據流實時處理等特性,該系統采用陣列結構的FFT處理器。

FPGA內部信號處理框圖如圖7所示。

從超高速單比特采樣模塊送來的高速并行數字信號,經數據預處理形成低速的格式化并行數據,經過移位寄存器處理送往陣列結構FFT處理器,移位寄存器的移位級數乘以移位數據寬度為后級FFT處理的數據長度,移位寄存器的數據寬度決定了滑動FFT的滑動點數。陣列結構FFT處理器輸出數據經信號檢測模塊檢出信號包絡,并為參數形成模塊提供第2級門限數值,參數形成模塊接收陣列結構FFT處理器的輸出數據,并結合信號檢測模塊提供的信息完成頻率參數提取。

以每次滑動128點(時域間隔5.12 ns)的4 096點FFT為例,FPGA內部數據處理時序示意圖如圖8所示。數據預處理模塊接收超高速單比特采樣模塊下來的數據率為781.25 MHz的32路并行數據,經過4倍同步降速,輸出數據率為195.312 5 MHz的128路并行數據(系統工作時鐘頻率即為195.312 5 MHz),經32級移位寄存處理進FFT處理器完成4 096點FFT處理。

陣列結構FFT處理器若用基2FFT算法實現,級數則為12。由于省去了乘法,每個蝶形單元的運算量在一個系統工作時鐘周期就能完成,則FFT處理器12個時鐘周期就能出結果,加上前級數據預處理4個時鐘周期和移位寄存32個時鐘周期,整個數字輸入到FFT處理出結果僅需245.76 ns((12+4+32)×5.12 ns),保證了測頻時間的瞬時性。

由于采樣時鐘為25 GHz,FFT處理長度為4 096點,那么FFT處理結果的頻率分辨率為6.1 MHz,再通過瞬時頻率測量法對FFT得到的結果做進一步的精估計,可近一步提高頻率分辨率(即提高測頻精度)。滑動時域間隔5.12 ns保證了到達時間提取的精度以及對窄脈沖的適應性。

4 仿真分析

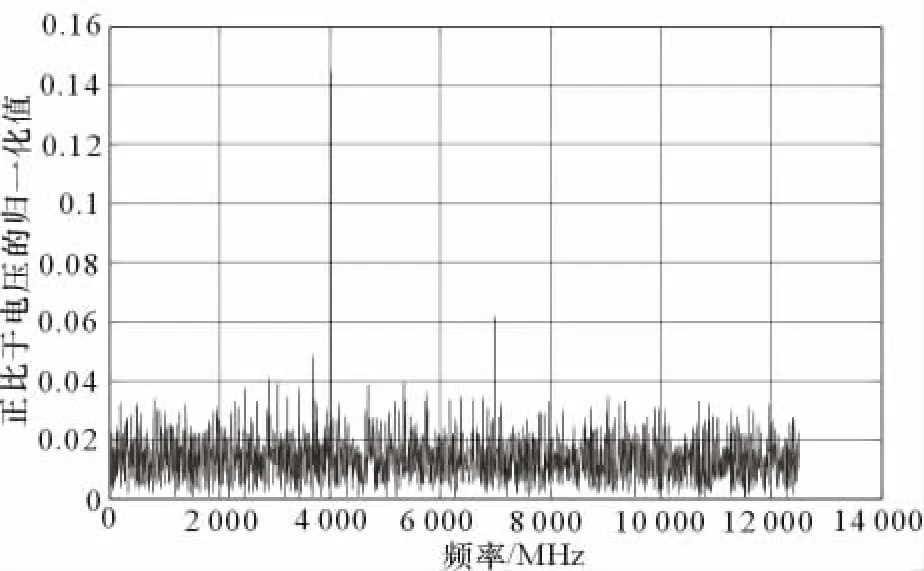

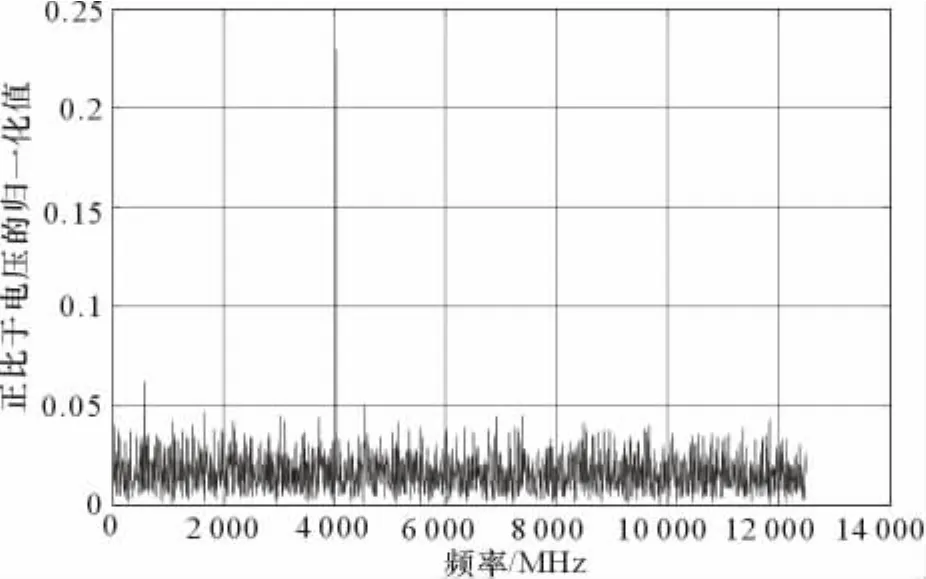

該算法能達到的檢測靈敏度,以及Kernel函數的簡化是否會引起FFT結果產生較大的誤差都是關鍵問題。圖9為信噪比S/N= -10 dB,Kernel函數取4個點的4 096點FFT功率譜;圖10為S/N=-10 dB,Kernel函數取8個點的4 096點FFT功率譜。

圖9 Kernel函數取4個點的4 096點FFT功率譜

圖10 Kernel函數取8個點的4 096點FFT功率譜

仿真結果表明,Kernel函數簡化的FFT頻譜主峰位置不變。Kernel函數取8點)和Kernel函數取4點相比,頻率響應中的旁瓣電平抑制有一定的改善。如果再增加Kernel函數的點數(大于8)意義不大(對旁瓣電平的抑制幾乎不會再有改善)。

圖11為同時輸入2個幅度相等的信號,2個信號頻率分別落在FFT離散頻率點上和FFT 2個離散頻率點正中,S/N= -10 dB,Kernel函數取4個點的4 096點FFT功率譜。

可以看出雖然S/N= -10 dB的信號能被檢測,但是考慮到輸入信號頻率分別落在FFT離散頻率點上和FFT 2個離散頻率點正中,功率譜是有差異的,以及整個帶內幅頻特性的不平衡等因素,要降低虛警,最終檢測所需要的最低信噪比(S/N)d優于-5 dB。當然,增加FFT點數(即提高處理增益),(S/N)d還可進一步降低。

圖11 不同頻點等幅信號,Kernel函數取4個點,4 096點FFT功率譜

5 結束語

綜上所述,這種基于實時數字處理的寬帶單比特瞬時測頻接收技術,采用超高速單比特采樣技術對輸入信號進行寬開的超高速采樣,全數字處理方式完成信號的快速實時處理和測量,實現了具有大寬帶、高靈敏度、實時處理且體積小巧的瞬時測頻接收機,大幅改善了傳統瞬時測頻接收機同時到達信號適應能力差,尤其是同時到達的2個輸入信號功率接近時輸出亂碼的問題,并且大幅提高了檢測靈敏度。數字化處理方式的靈活性和可擴展性,使其性能還有進一步提高的余地。基于上述優點,該接收機在電子戰領域具備廣泛的應用前景。

[1]James Tsui.寬帶數字接收機[M].楊小牛,陸安南,金飚譯.北京:電子工業出版社,2002.

[2]胡廣書.數字信號處理(理論、算法與實現)[M].北京:清華大學出版社,2003.

[3]周濤.電子戰中的單比特數字化接收機技術[J].電子對抗,2006,5(1):6-10.

[4]常虹,趙國慶.高效寬帶數字信道化單比特接收機[J].沈陽工業大學學報,2010,32(2):212-216.

[5]劉剛,植強,呂鏡清.一種提取雷達到達時間的方法[J].電子對抗,2003(4):10-13.