基于DRFM的卷積干擾技術研究

蔣平虎,蘇萍貞,黎明也,翁永祥

(中國電子科技集團公司51所,上海 201802)

0 引 言

脈沖線性調頻信號是現代雷達常采用的一種信號體制,雷達接收的寬脈沖回波信號經壓縮處理后形成窄脈沖,獲得較高的處理增益,較好地解決了雷達脈沖峰值功率受限與距離分辨率之間的矛盾[1]。

隨著數字技術和大規模集成電路的飛速發展,脈沖壓縮比越來越高、控制方式更加靈活。大時寬脈壓技術的采用,給基于數字射頻存儲器(DRFM)的相干干擾形成假目標的密集度帶來了巨大的壓力,因此需要研究新的干擾樣式來實現對線性調頻體制雷達的干擾。

本文基于DRFM提出了一種新的干擾樣式產生技術,分析了卷積算法在干擾樣式產生技術中的運用,并分別從原理和工程上對該技術進行了分析與設計,通過半實物仿真驗證該技術的有效性。

1 卷積干擾原理

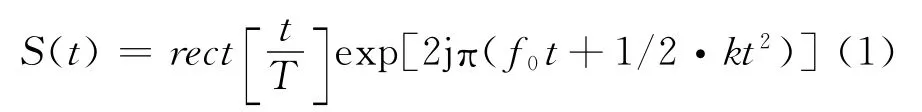

設雷達調頻信號為:

式中:f0為信號載頻;k=B/T為調頻率,B為信號帶寬,T為脈沖寬度。

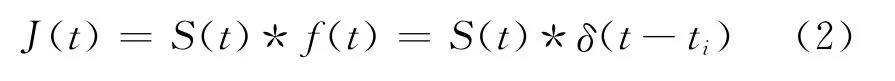

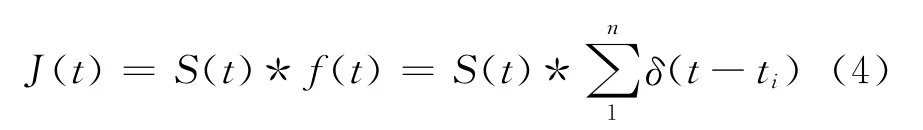

干擾機接收到雷達照射信號S(t)與調制信號f(t)(本系統設計時調制信號采用δ(t-ti))卷積后轉發出去。那么干擾信號J(t)為:

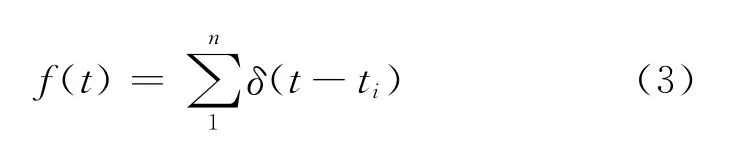

該式的物理意義為:信號經過延時系統延時量為ti的信號。若要進行多次延時,可以卷積以下函數:

那么匹配濾波器的干擾輸入信號為:

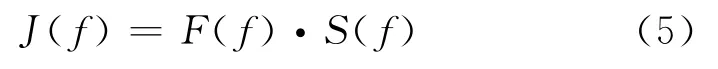

設S(t),f(t)的頻譜分別為S(f),F(f),則:

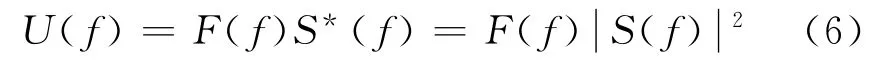

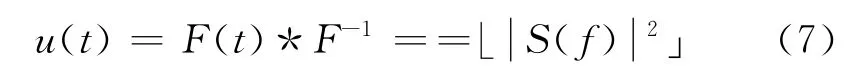

經匹配濾波后輸出的頻譜為:

對應時域輸出為:

上式表明干擾信號取決于參與卷積信號f(t),即任一函數與線性調頻信號卷積,其脈沖壓縮輸出信號為該函數與點擴展函數的卷積,且獲得了脈沖壓縮處理增益。這就是卷積干擾可以降低干擾功率的理論依據[3]。

2 系統設計與實現

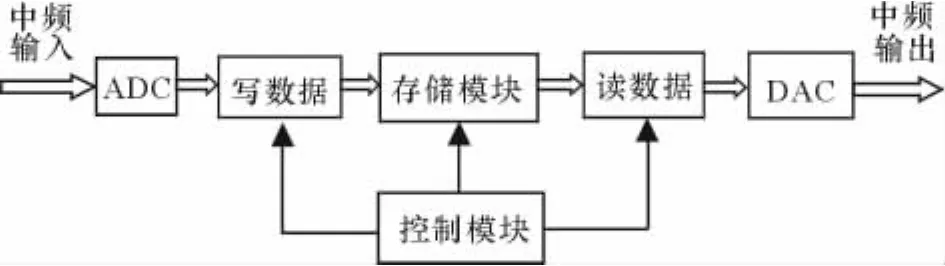

在具體討論卷積延時技術實現之前,先簡單介紹一下DRFM(8 bit)的工作原理,DRFM將雷達射頻信號變頻后的中頻信號直接存儲,保留了原始信號的幅、相信息,使存儲信號與原始信號有相干性,具有相參捕獲及高精度復制威脅信號的能力,能夠對脈沖壓縮、脈沖多普勒和相位編碼等雷達信號提供有效的相參信號。

中頻信號經模數轉換(ADC)采樣變成低壓差分信號(LVDS)電平的高速數據,經數據處理后,形成并行的64位數據流,在主控電路的控制下,準確地存入靜態隨機存儲器(SRAM)中。當需要讀出時,SRAM中的64位并行數據經升速轉換成8位的串行數據流,通過數模轉換(DAC)實現中頻存儲信號的復制。

圖1為DRFM板卡的組成框圖。

圖1 DRFM板卡組成框圖

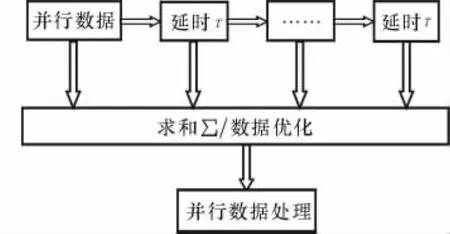

在數字儲頻技術的基礎上,對從存儲模塊中讀出的數據進行卷積延時處理,即采用寄存器流水線方式,對并行數據進行固定延時τ后,再并行做加法運算,具體框架如圖2所示。

圖2 卷積疊加算法組成框圖

由于采用寄存器流水線方式對數據進行運算處理,因此數據流無縫連接達到實時要求。

采用對雷達信號卷積延時的方式可以最大限度地保證雷達脈沖信號的完整性,同時假目標的個數取決于延時間隔,這種設計方式可在雷達重復周期內產生n(n=雷達重周/延時間隔)個信號,雷達通過相關接收后出現n個點跡。

本系統中延時間隔為8μs,對于某典型雷達,重復周期最小為2 ms,脈寬最大為100μs,這樣雷達上出現的點跡將增加到250個,可達到密集覆蓋要求和掩護真實目標的效果。

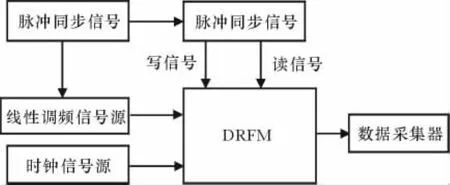

為了測試卷積延時算法的實際效果,建立實驗測試平臺,其分為2種架構,一是直接在單板(DRFM)上進行測試驗證;二是對接收到的雷達信號利用該算法檢測其干擾效果。

圖3 系統測試組成框圖

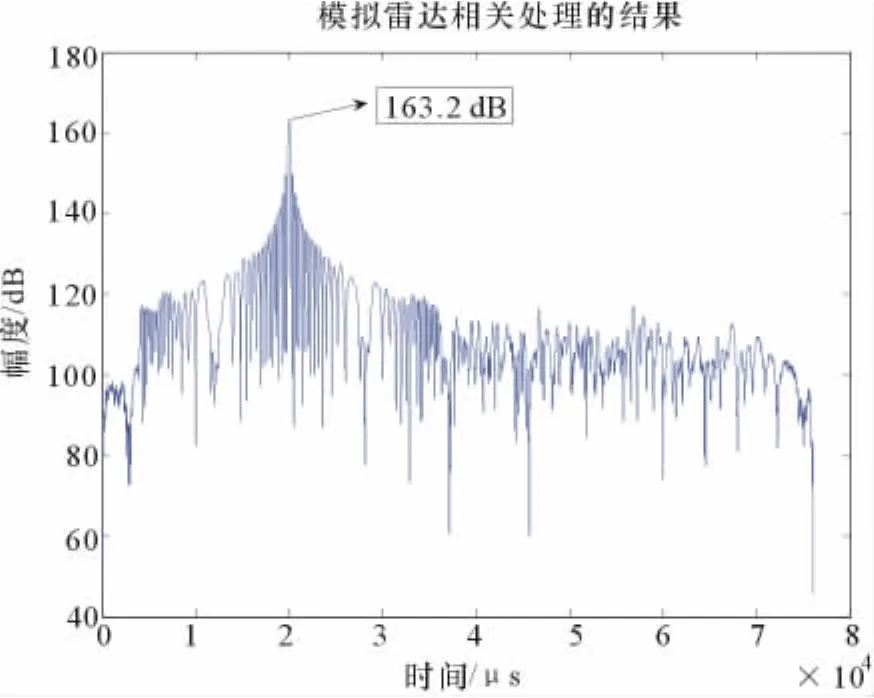

通過分析,進行相應的半實物仿真試驗,即模擬實際雷達接收到干擾信號后的處理結果。仿真時的參數設置盡量與實際器件水平相匹配。仿真雷達參數:脈寬為32μs,帶寬為2 MHz(130~132 MHz);干擾控制節拍為延時間隔(8μs)。

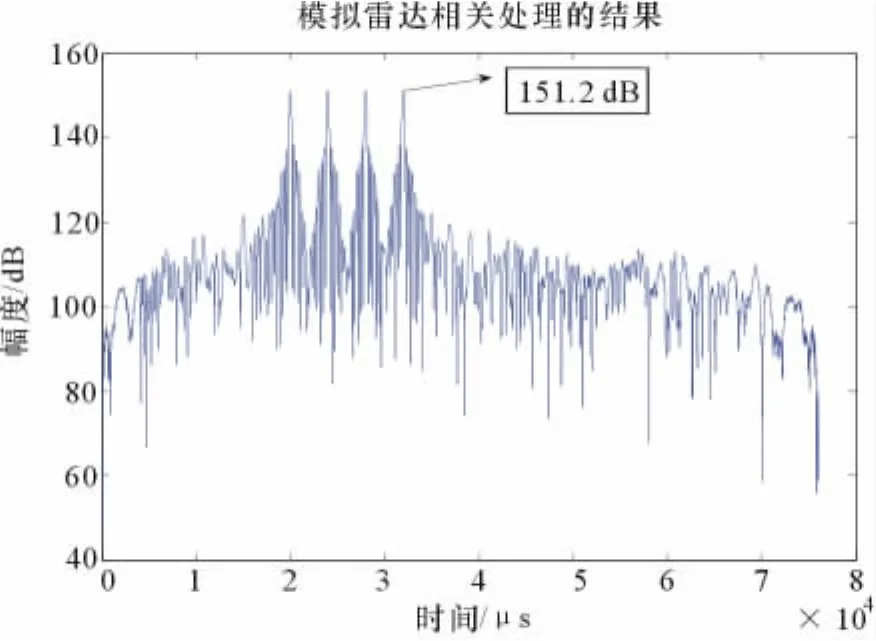

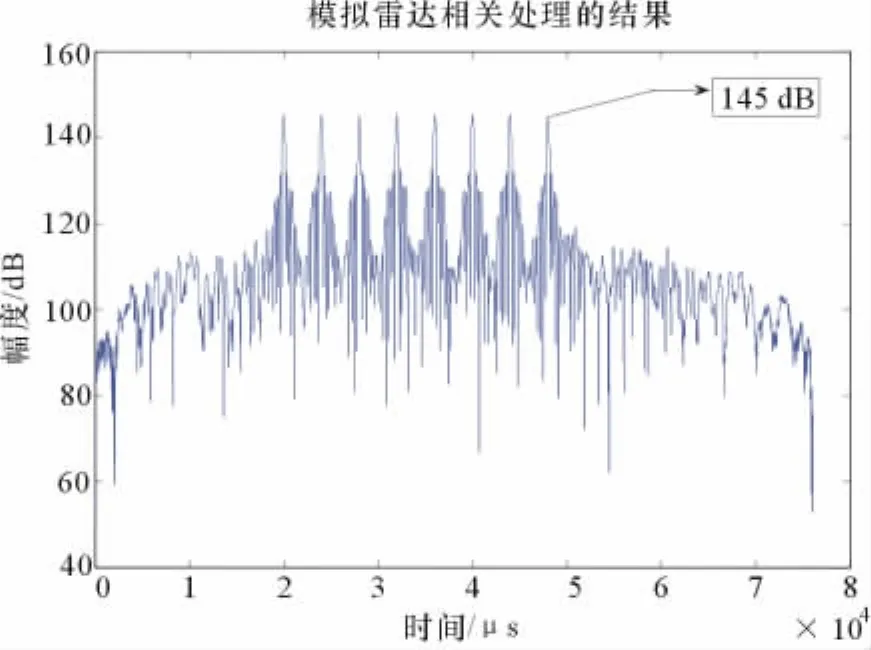

圖4~圖7為模擬雷達收到干擾波形后相關處理的仿真結果。

圖4 信號卷積延時1次

圖5 信號卷積延時2次

通過上述圖形可以發現經過卷積延時后的干擾信號數量可隨設計的目標增加,目標間的間距為所設計的延時量程,因此可產生密集的假目標群。

3 結束語

本文對基于DRFM的卷積干擾樣式對大時寬線性調頻雷達有效干擾的信號產生進行了理論的分析,并在工程上實現該干擾樣式產生的硬件方案,同時利用半實物仿真驗證了理論分析的正確性。通過這一技術可實現對大時寬線性調頻雷達實現高密集度的假目標干擾。

圖6 信號卷積延時4次

圖7 信號卷積延時8次

[1]Skolnik Merrill A(美).雷達手冊[M].王軍,林強,米慈中,等譯.北京:電子工業出版社,2003.

[2]保針,邢孟道,王彤.雷達成像技術[M].北京:電子工業出版社,2005.

[3]張煜,楊紹全.對線性調頻雷達的卷積干擾技術[J].電子與信息學報,2007,29(6):1408-1411.