基于SPU的雷達信號處理技術

王曉華

(船舶重工集團公司723所,揚州 225001)

0 引 言

雷達技術的迅速發展對其測距精度和測速精度提出了越來越高的要求,測距精度和距離分辨力取決于信號的頻率結構,提高測距精度和距離分辨力,要求信號具有大的帶寬。而測速精度主要取決于信號的時間結構,為了改善速度分辨力,信號必須有大的時寬[1]。雷達發現能力、測量精度和分辨力等因素要求具有大時寬、帶寬乘積的脈沖壓縮信號完成正常及動目標檢測功能,這對信號處理硬件平臺和軟件設計提出了苛刻的要求。

近年來,隨著超大規模集成電路技術迅猛發展以及數字技術的日益成熟,雷達數字信號處理由視頻向中頻乃至更高頻率邁進。尤其是數據處理能力不斷增強、性能指標不斷提高的數字信號處理器(DSP)相繼出現,以及超大規模可編程邏輯陣列(FPGA)的問世,為雷達信號處理數字化、軟件化實現提供了充分的條件和有力的工具。DSP本身性能的提高使得雷達信號處理設計更為靈活,而采用FPGA設計使得雷達信號處理速度大大提高,兩者既密切結合又相互獨立。

本文的設計基于SPU電路板硬件平臺,載板集成2片TMS320C6455DSP和1片EP2S90FPGA以及雙口隨機存儲器(RAM)和其他外圍接口,子板由4片模數轉換采集芯片和1片EP2S90構成,子板與載板之間通過32位并行數據以及8對低壓差分信號(LVDS)傳輸。

1 基于SPU板雷達信號處理構架

SPU板構架框圖如圖1所示。

圖1 SPU板構架框圖

本文信號處理采用1塊通用四通道中頻采集子板和1塊通用信號處理平臺SPU作為主要硬件平臺,該平臺具有超大規模的FPGA、快速先進的DSP以及大容量的存儲器,對于完成實時性要求較高的信號處理,具有較好的適應能力和靈活性。SPU板為一塊雙DSP、單FPGA的載板(以下簡稱載板),載板上可棧接一塊多路采集子板,本分機設計采用一塊通用四通道中頻采集子板(以下簡稱子板),該子板上有4路模數轉換器(ADC)和1片超大規模的FPGA,以滿足多通道同時采集、數字下變頻等功能的資源要求。SPU板用以實現各種動目標處理、正常以及恒虛警處理等功能。

2 實時信號處理實現

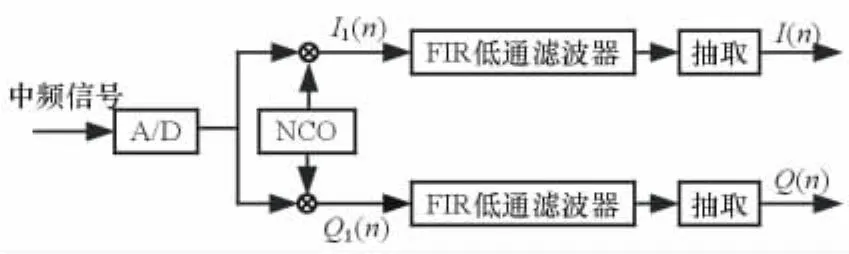

2.1 信號數字中頻接收

雷達信號中頻數字接收功能(如圖2所示)在SPU子板實現,主要完成中頻信號數字采樣以及數字下變頻處理,數字下變頻由數控振蕩器(NCO)、數字混頻器、有限持續時間沖激響應(FIR)低通濾波器及抽取器等構成,數字下變頻功能均在FPGA內實現。采用相參80 MHz時鐘對中頻60 MHz信號進行欠采樣,由于信號帶寬較寬,因此后級的變頻濾波采用高階復數低通濾波器實現。子板4路ADC和1塊FPGA可以同時完成信號采集、數字下變頻、脈壓和抗異步等功能的資源要求。

2.2 脈沖壓縮系統實現

脈沖壓縮的主要功能是對回波作匹配濾波壓縮處理以恢復距離分辨力和提高信噪比。脈沖壓縮能讓雷達系統發射寬度相對較寬而峰值功率相對較低的脈沖,但可獲得和窄脈沖、高峰值功率系統一樣的距離分辨率的探測性能[2]。

圖2 中頻數字接收功能框圖

數字脈沖壓縮的工程實現有2種方法:時域的卷積法和頻域的快速傅里葉變換(FFT)法。由于早期硬件的約束,使時域的卷積法無法實現,多采用頻域的FFT實現方法,利用FFT的算法優勢,以較少的資源實現大時寬信號的數字壓縮,但必須先對信號進行FFT變換、加權,然后進行反FFT變換,其間信號的緩沖、FFT點數的選取、時序的控制等相對復雜。

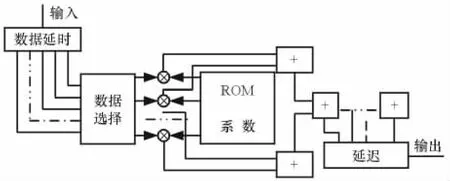

隨著硬件技術的高速發展,采用時域卷積法成為可能,將多種時寬信號時寬擴展為最長的一種,以等階數的FIR濾波器來設計硬件,雖然耗費芯片資源比較多,但帶來的好處是對雷達波形的設計不受時寬限制,脈沖壓縮匹配濾波器實現如圖3所示。

圖3 時域卷積濾波器結構圖

由于本系統最長碼型64μs,信號進行脈壓時是低速(5 MHz)流水進行,濾波器階數為320階,即需要1 280個16×16乘法器,而目前最新FPGA也無法提供如此多乘法器資源,因此采用多路復用乘法器提高其速率,減少資源。若乘法器速度提高到80 M,即是原來結構速率的16倍,則濾波器所需的乘法器減少16倍,資源利用效率顯著改善。設計改進濾波器結構如圖4所示[3]。

圖4 改進濾波器結構圖

2.3 動目標檢測

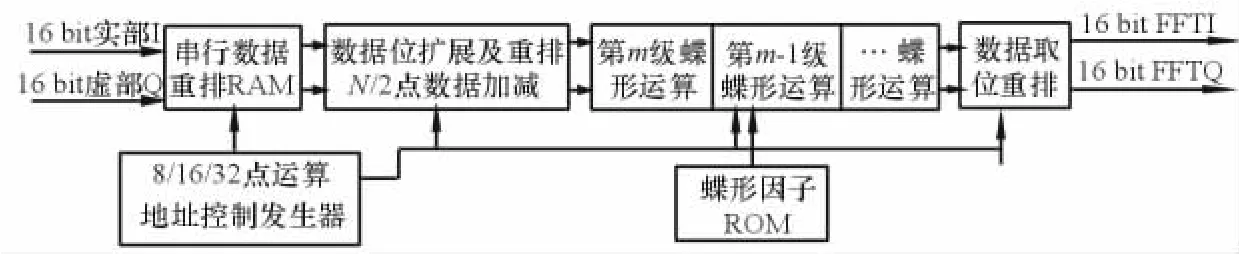

動目標檢測(MTD)是雷達信號處理的一個重要功能,即從運動目標回波和雜波中提取運動目標,抑制固定雜波。動目標檢測的主要方法是應用FFT算法。搜索雷達的8/16點FFT是單滑動的,必須在一個距離單元時間0.2μs內完成8/16點FFT。C6455DSP(目前市場上主流產品),1 G主頻,使用TI公司提供的優化算法,不計算數據存取讀寫時間,完成一次16點FFT需3.48μs,不能滿足系 統 需 求,因 此 采 用 FPGA 實 現 8/16/32點FFT。

Altera公司提供FFT核,但不是免費使用的,且一些電路設計受限。通過自行設計的FFT模塊實現,FFT的FPGA實現通常有2種方法:一種是并行流水結構,以16點FFT為例,輸入16路數據同時并行完成加窗、蝶形等運算,其優點是計算速度快、數據吞吐率大,缺點是占用資源太多;另一種是串行結構,其加窗、蝶形等運算按時鐘節拍串行完成,最大優點是資源利用率高,同樣單一16點FFT邏輯資源是并行方式的1/5,DSPblock資源是并行方式的1/3,運算速率、動態范圍等指標均能滿足系統要求。8/16/32點串行FFT變換的FPGA實現如圖5所示,FPGA芯片使用的是EP2s90,該芯片具有豐富的邏輯、乘法器、隨機存儲器(RAM)等資源。完成8/16/32點FFT變換所用乘法器32×32位的共12個,占資源25%;存儲器M512共25個,占資源5%;自適應查找表(ALUT)約1 000個,占資源不到1%;整個模塊因系統需大動態范圍采用32×32位的乘法器,占用較多乘法器資源,運行速率可達250 MHz。

圖5 串行8/16/32點FFT變換的FPGA實現框圖

2.4 非相參積累模塊

非相參積累的主要功能是完成方位向回波幅度的滑動積累,提高信噪比,積累結果輸出作為背景輸出,積累結果恒虛警處理后作為正常視頻,受動顯/正常視頻選擇控制輸出。

非相參積累在SPU處理板的DSP內實現(如圖6所示),再將經脈壓處理后的回波數據按時間順序存入到雙口RAM中,DSP將根據脈壓后的數據讀入片內緩存,根據不同積累點數選擇不同的積累窗長,執行相應的積累程序。

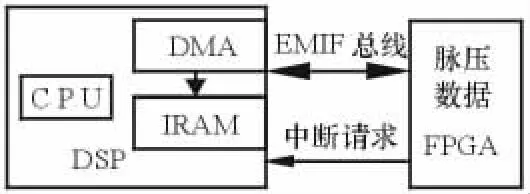

其特征在于:由DSP和FPGA互相配合實現非相參處理;在FPGA中斷請求下,數據通過外部存儲器接口(EMIF)總線完成FPGA與直接存儲器存取(DMA)之間傳輸,DMA再傳輸給DSP的內部隨機存儲器(IRAM),由CPU完成變點數積累。

使用DMA提高了數據傳輸的速率和吞吐率,而且傳輸過程不占用CPU資源;同時利用DSP設計模式多變、運算功能復雜的模塊,而FPGA設計功能相對單一、實時性要求高的模塊,通過DSP、FPGA資源合理應用、互相取長補短完成雷達信號處理等各種功能。

圖6 非相參積累實現框圖

3 結束語

本文采用SPU信號處理硬件平臺實現雷達信號處理功能,根據某雷達系統應用表明該平臺實時處理能力強,通用性高,且減少了信號處理硬件設備量。

[1]林茂庸,柯有安.雷達信號理論[M].北京:國防工業出版社,1984.

[2]王希勤.近程低空雷達數字信號處理系統幾個關鍵技術問題的研究與實現[D].北京:清華大學,1996.

[3]王曉華.基于FPGA的多波形脈沖壓縮系統研究與實現[A].中國電子學會電子對抗分會第十五屆學術年會論文集[C].揚州,2007:526-530.