FPGA跨時鐘域亞穩態研究

廣東工業大學自動化學院 周 偉 杜玉曉 楊其宇 張育俊 曾 浩

FPGA跨時鐘域亞穩態研究

廣東工業大學自動化學院 周 偉 杜玉曉 楊其宇 張育俊 曾 浩

在FPGA電路設計中,一個系統可能包含了很多跨時鐘域的時鐘信號,當其目標域時鐘與源域時鐘不同時,如何在這些不同域之間傳遞數據成為了一個重要問題。特別是在中心模塊與外圍電路芯片的通信設計中,容易導致亞穩態的跨時鐘域就不可避免。針對FPGA設計中的亞穩態問題,本文給出了一系列行之有效的解決方法,很好地抑制亞穩態,提高系統可靠性。

亞穩態;建立時間;保持時間;異步FIFO;握手協議

1.引言

在FPGA同步時序電路設計中,即所有時鐘寄存器的時鐘共享一個時鐘,可以有效地消除亞穩態。然而,許多實際應用要求在同一個可編程邏輯器件內采用多個時鐘,且核心模塊與外設的通信設計也涉及跨時鐘域的數據傳遞。跨時鐘的異步時序電路含有的多個時鐘源,它們存在頻率和相位的差異,當它們用作寄存器的輸入時鐘時,就可能違背建立時間和保持時間的要求,出現亞穩態[1-5]。亞穩態問題是跨時鐘域異步數據傳輸過程面臨的主要問題。

在FPGA設計中,每種觸發器都有時序要求。“建立時間”(Setup time)是指在時鐘沿到來之前,觸發器輸入信號必須保持穩定的時間。“保持時間”(Hold time)則是指在時鐘沿之后,信號必須保持穩定的時間。這些指標通常比較保守,以應對不同的PVT(工藝、電壓、溫度)環境下時序各有差異的情況。如果一個設計滿足了這些時序要求,則觸發器出現錯誤的可能性可以忽略不計。

亞穩態是當信號在跨時鐘的異步電路中或是無關的時鐘域之間傳輸時導致數字系統失效的一種現象。為了使觸發器能夠正確捕獲并輸出數據,FPGA的信號傳輸數據信號都會有一定的時序要求,為了確保可靠的操作,輸入寄存器的數據信號必須在時鐘沿的某段時間(寄存器的建立時間Tsu)之前保持穩定,并且持續到時鐘沿之后的某段時間(寄存器的保持時間Th)之后才能改變。寄存器的輸入反映到輸出則需要經過一定的延時(時鐘到輸出的時間Tco)。如果數據信號的變化違反了Tsu和Th的要求,那么寄存器的輸出就會處于亞穩態[6]。此時,寄存器的輸出會在高電平1和低電平0之間盤旋一段時間,這也意味著寄存器的輸出達到一個穩定的高或者低電平的狀態所需要的時間會大于Tco。

隨著跨時鐘域設計的愈發常見和復雜化,只要系統中存在跨時鐘域,亞穩態就是無法避免的,因此設計的電路首先要減少亞穩態導致錯誤的發生,其次要使系統對產生的錯誤不敏感。前者要靠同步來實現,而后者根據不同的設計應用有不同的處理辦法。

2.FPGA設計中的亞穩態

2.1 亞穩態

在FPGA設計中,數據信號在不同時鐘域間傳遞,最容易產生亞穩態,即觸發器無法在時序要求的規定時間段內達到一個可確認的狀態。數據信號在傳輸過程中觸發器的建立時間或保持時間不滿足時序要求,即信號在穩定前的狀態,一般是由于時序余量不夠,使得電路的輸入電平無法上升或下降到所需邏輯電平1或0。

2.2 亞穩態分析

跨時鐘異步輸入信號可以在任何時間點翻轉,它與下級同步采樣信號沒有必然聯系。此外,在數據翻轉前,設計者無法預知該被采樣信號的時鐘沿或翻轉順序,也就不能保證信號滿足建立時間。無法保證穩定的采樣,給跨時鐘域的FPGA設計帶來難題。

跨時鐘域的轉換的核心就是要保證下級時鐘對上級時鐘數據的采樣的Tsu和Th時間。如果觸發器的Tsu時間或Th時間不能滿足,就可能產生亞穩態,此時觸發器輸出端Q在有效時鐘沿之后較長時間處于不確定狀態,在這段時間內Q端產生毛刺并不斷振蕩,最終固定在某一個值,這個值不一定等于原來數據輸入端口D的數值,這短時間稱為判決時間(Resolution time),經過Resolution time之后Q端經穩定到0或1上,但究竟是0還是1,是隨機的。與輸入沒有必然的聯系。

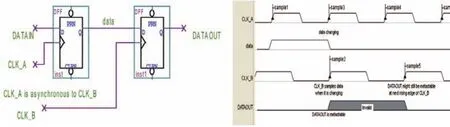

如圖1所示,時鐘CLK_A在上升沿時采樣數據DATAIN,數據信號data是時鐘CLK_A同步產生的,輸入信號data對下一級的觸發器的時鐘CLK_B是跨時鐘的異步信號,由于data的變化與CLK_B時鐘域時鐘的采樣邊沿太接近,未滿足采樣建立時間,造成的亞穩態周期。輸出DATAOUT傳遞到后面的組合邏輯會產生不定狀態,若在進入下一級采樣前還沒有進入穩定狀態,就會導致系統混亂。

圖1

圖2

圖3 握手協議

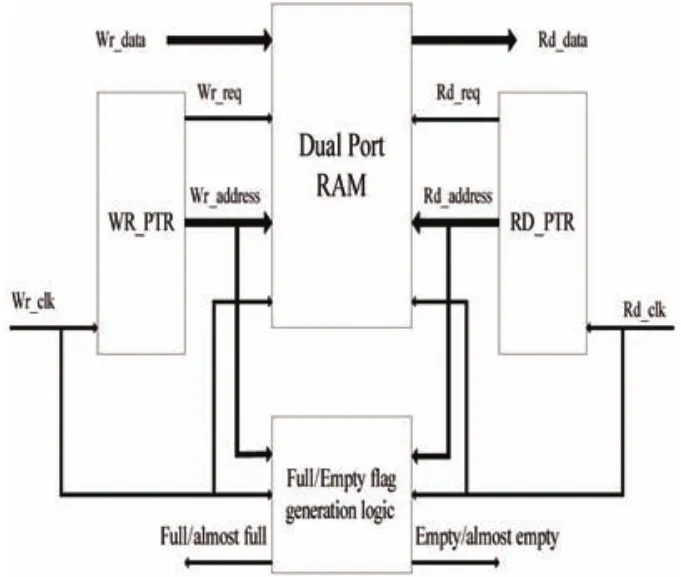

圖4 異步FIFO

亞穩態的危害主要是破壞系統的穩定性。由于輸出在穩定前可能有毛刺、振蕩、固定的某一電壓值,因此亞穩態將導致邏輯誤判,嚴重的情況輸出0~1之間的電壓值還會使下一級產生亞穩態,即亞穩態的傳播。邏輯誤判導致功能性錯誤,而亞穩態傳播則擴大故障面。另外,在亞穩態下,電源干擾、環境噪聲、工作溫度等細微的擾動都可能導致更惡劣的狀態不穩定,這時系統的傳輸延遲增大,狀態輸出錯誤。

3.FPGA跨時鐘解決方案

FPGA設計中,要減少亞穩態導致的錯誤并使系統對產生的錯誤不敏感,就要正確定義和處理FPGA內部與外部時鐘之間的接口。對于異步或無關時鐘域間傳輸的信號,在FPGA本地時鐘域使用該信號前,必須對其進行同步。同步器的功能是采樣異步輸入信號,使產生的輸出信號滿足同步系統對建立時間和保持時間的要求,從而抑制亞穩態對電路的影響。在許多應用中,跨時鐘域傳送的不只是簡單的信號,數據總線、地址總線和控制總線都會同時跨域傳輸,這些復雜的情況,就需要應用握手協議和異步FIFO的手段來處理這些情況。因此處理跨時鐘域常用的方法有兩級觸發器同步法、握手協議和異步FIFO法3種。

3.1 兩級寄存器同步法

為了避免進入亞穩態,通常采用的方法是使用兩級寄存器,即一個信號要進入另外一個時鐘域之前用另一時鐘域的時候進行兩次寄存,在圖2中,左邊為異步的輸入端,經過兩級觸發器采樣,在右邊的輸出與時鐘CLK_B同步,而且該輸出基本不存在亞穩態。其原理是即使第一個觸發器的輸出端存在亞穩態,經過一個CLK時鐘周期后,第二個觸發器D端的電平仍未穩定的概率非常小,因此第二個觸發器Q端基本不會產生亞穩態。理論上如果再添加一級寄存器,是同步采樣達3級。則末級輸出為亞穩態的概率幾乎為0。因此使用兩級寄存器采樣可以有效地減少亞穩態繼續傳播的概率。

使用圖2所示兩級寄存器采樣不僅能降低亞穩態的概率。但是并不能保證第二級的輸出的穩定電平就是正確的電平。前面說過經過Resolution time之后寄存器輸出電平是一個不正確定的穩態值。也就是說這種處理方法不能排除采樣錯誤的產生。這時就要求所設計的系統對采樣錯誤有一定的容忍度。有些應用本身就對采樣錯誤不敏感,有些系統對錯誤采樣比較敏感,可以采用一些糾錯編碼手段完成錯誤的糾正。

3.2 握手協議

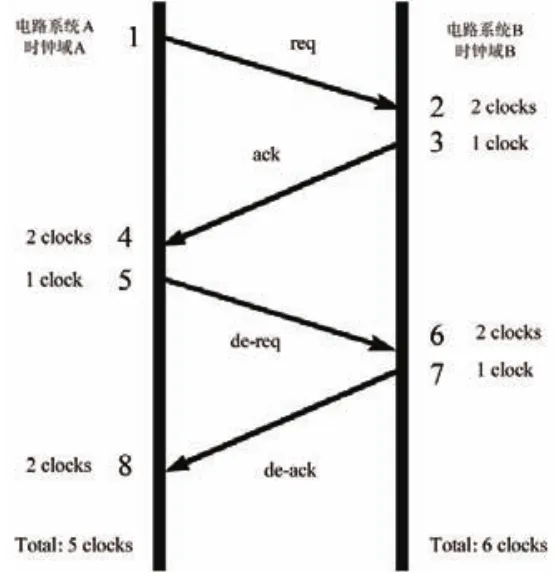

握手協議是實現總線數據跨時鐘域通信的一種有效方法,它能在避免亞穩態傳播的同時正確地捕獲總線數據。握手信號,雙方電路在聲明或中止各自的握手信號前都要等待對方的響應。使用握手協議方式處理跨時鐘域數據傳輸,只需要對雙方的握手信號(req、ack)分別使用脈沖檢測方法進行同步。在具體實現中,首先,電路A聲明它的請求信號,即先把數據放入總線,隨后發送有效的請求req信號給電路B。然后,電路B檢測到有效的req信號后鎖存數據總線,聲明它的響應信號,即回送一個有效的ack信號表示讀取完成應答。當電路A檢測到電路B回應的響應信號有效后,中止自己的請求信號,即撤銷當前的req信號。最后,當電路B檢測到電路A的信號req撤銷后也相應撤銷ack信號,此時完成一次正常握手通信。此后,可以繼續開始下一次握手通信,如此循環。該方式能夠使接收到的數據穩定可靠,有效的避免了亞穩態的出現,以上所述的通信流程如圖3所示。

信號跨越一個時鐘域要花兩個時鐘周期的時間,信號在跨越多個時鐘域前被電路寄存。全部的時間序列是:A時鐘域中最多五個周期加上B時鐘域最多六個周期。握手有效的避免了亞穩態的出現,因為通過檢測請求與響應信號,每個電路都清楚地知道對方的狀態。但控制信號握手檢測會消耗通信雙方較多的時間,完成所有交互的整個過程要花費很多時鐘周期。

3.3 異步FIFO

異步FIFO[7-8]是一種先進先出的電路,使用在需要產時數據接口的部分,用來存儲、緩沖在兩個跨時鐘異步時鐘之間的數據傳輸。使用一個異步FIFO在兩個時鐘域的交界處通信,通過它來實現數據流的傳輸。由發送時鐘域將數據寫入,接收時鐘域將數據取出,在數據傳輸的同時實現了數據的緩存,因此是一種較理想的方法。

由圖4可以看出:整個系統分為兩個完全獨立的時鐘域——讀時鐘域和寫時間域;FIFO的存儲介質為一塊雙端口RAM,可以同時進行讀寫操作。在寫時鐘域部分,由寫地址產生邏輯產生寫控制信號和寫地址;讀時鐘部分由讀地址產生邏輯產生讀控制信號和讀地址。在空/滿標志產生部分,由讀寫地址相互比較產生空/滿標志。

不同時鐘域間數據傳遞的問題及其解決方法不同時鐘域間數據傳遞的最重要問題就是亞穩態問題。當數據信號通過兩個時鐘域的交界處時,將會分別由這兩個時鐘來控制信號的值。此時如果兩時鐘信號的敏感沿非常接近并超過了允許的額度,則將出現數據信號的不穩定,即電路陷入亞穩態,也稱為同步失敗,同樣會產生亞穩態。但是通過設計改進可以將其發生的概率降低到一個可以接受的程度。

在FIFO設計中,FIFO指針邏輯使用了格雷碼,代替指針使用的二進制碼。格雷碼在每一次計數增減時只改變其中的一位。你可以在格雷碼總線上使用同步器,因為每一次總線改變時只有一根信號線有變化,于是就消除了格雷碼總線各位通過不同同步器時的競爭情況,降低了亞穩態的產生,在異步FIFO設計中,通過提高空/滿標志產生邏輯的可靠性,能夠很好地抑制亞穩態,進一步的降低了亞穩態的產生。

4.結語

在FPGA跨時鐘域設計中,亞穩態與設計可靠性有著密切的聯系。本文探討分析了跨時鐘域亞穩態的產生機制及FPGA設計中亞穩態問題的解決方法,提出的這些方法行之有效。傳輸在不相關時鐘域的信號,都有可能在相對于捕獲寄存器時鐘沿的任何時間點變化。因此,設計者無法預測信號變化的順序或者說信號兩次變化間經過了幾個鎖存時鐘周期。設計者必須考慮到電路的這些情況,在實際應用中,設計者可根據具體的實際情況而使用異步FIFO傳輸信號或者使用握手信號進行控制。

一般情況下兩級寄存器同步適合步時鐘域之間單信號傳輸;當幾個電路不能預知相互的響應時間時,握手方法能讓數字電路間實現有效的通信;總線數據同步、高速數據傳輸、數據在跨越時鐘域時需要存儲容量大的緩沖時則可以采用異步FIFO。這些措施能夠有效解決FPGA設計中跨時鐘域的亞穩態問題,能實現數據跨越時鐘域的安全傳遞。

[1]夏字聞.Verilog數字系統設計教程(2版)[M].北京:北京航空航天大學出版社,2008.

[2]魏堃.跨時鐘域信號同步技術研究[D].西安:西安電子科技大學,2009.

[3]Michelle Lange.Automated CDC verification protects complex electronic hardware from metastability failures.Mentor Graphics Corporation.Aug.2008.

[4]孟憲元,譯.高級FPGA設計結構、實現和優化[M].北京:機械工業出版社,2009.

[5]徐翼,鄭建宏.異步時鐘域的亞穩態問題和同步器[J].微計算機信息,2008,24(2):171-172.

[6]吳小蕻.跨時鐘域若干問題的研究-同步與亞穩態[D].合肥:中國科學技術大學,2008.

[7]楊青山,蔡敏.基于多時鐘域的異步FIFO設設計[J].中國集成電路,2007(9):36-39.

[8]于海,樊曉椏.基于FPGA異步FIFO的研究與實現[J].微電子學與計算,2007.