基于運動補償的長時相干積累方法研究*

王啟智,岳玫君,杜春鵬**

(1.中國電子科技集團公司第三十八研究所,合肥 230088;2.解放軍電子工程學院,合肥 230037)

0 引言

稀布陣綜合脈沖孔徑雷達(SIAR)采用多發多收體制,使得發射信號在空間全向輻射,疊加后不形成方向圖,輻射能量在所有方向均勻分布。它不存在波束掃描時間問題,可以采用長時相參積累技術,以對付現代戰爭中諸如巡航導彈、隱身飛機等極小RCS 目標的挑戰。然而,隨著積累時間的增長,會帶來一系列新問題,如需要解決低信噪比下目標回波的運動補償等。本文通過對稀布陣體制雷達目標回波的建模,分析了長時相參積累的特點,提出一種簡易的運動補償方法,并給出具體的工程實現方案。

1 信號模型

1.1 目標回波信號模型

由于稀布陣雷達各發射陣元采用正交編碼信號對空間進行全向輻射,信號在空間沒有形成相干相加,不形成發射方向圖,各方向上輻射功率近似相等,其發射方向圖在接收端通過信號處理方式等效形成。

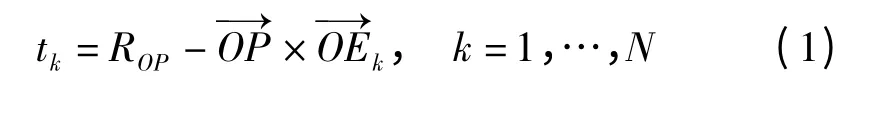

如圖1所示,設空間遠場區有一點目標P,其仰角為θ,方位角為φ,內圓為N個發射陣,外圓為M個接收陣,以陣中心點O為基準點。各發射站點相應于目標P的距離為

圖1 圓形陣幾何關系

各接收站點相對于目標P的距離為

第k個發射陣元到目標再到第l個接收陣元之間的總延遲為

令

則

其中τ0為目標回波相對于陣中心的時延,△τk為目標與第k個發射陣元相對于陣中心波程差的時延,△τl為目標與第l個接收陣元相對于陣中心的波程差時延。

假定各陣元發射線性調頻信號,調頻指數μ 相同,第k個陣元發射信號為

其中,rect(t)=1,(0≤t≤Te),否則為零;Te為發射脈沖寬度;fk表示第k個陣元發射信號頻率,fk=f0+Ck△f,f0為中心載頻,Ck為各陣元發射頻率編碼,△f為各陣元發射信號頻率間隔;Φk為各發射信號初相。假設P為靜止目標,忽略包絡時延差,信號經過目標P反射回波被第l個陣元接收的信號形式:

其中Ap為回波信號幅度。對各接收陣元信號下變頻,相位補償后即可進行波束形成、濾波等處理。

1.2 SIAR 長時相干積累特點

積累技術是雷達提高檢測能力的常用手段,但因波束掃描,可供積累的脈沖數主要受波束寬度、天線掃描等因素的限制。波束駐留目標時間內脈沖數有限,同時為了抑制雜波,有時還不能全部用來積累,都會影響積累改善因子。

SIAR雷達不存在波束掃描,它是全向輻射,在接收端通過信號處理形成發射和接收波束。因此,SIAR雷達可以向常規雷達的“燒穿”模式那樣,在某個方位甚至整個空間形成多個波束或波束堆積,積累時間只受目標運動和雷達參數影響,與波束對目標的掃描時間無關。但是,由于目標的運動,長時相參積累也會存在很多問題。

(1)發射信號帶寬限制了相干積累脈沖數

SIAR 同時發射的多個頻率信號中,最大頻率和最小頻率引起的多普勒頻率誤差為

其中,B為發射信號帶寬,v為目標速度,c為光速。若徑向速度v為630 m/s,帶寬=0.4 MHz,則εfd=1.68 Hz。εfd應小于FFT 濾波器的頻寬△F,△F=PRF/N,因此在重復周期PRF 一定的前提下就決定了積累脈沖數N。

(2)目標長時間運動存在多普勒頻率的變化

由于目標運動方向與雷達視線的夾角,隨著觀察時間增長,即使對勻速直線運動的目標,也會因夾角的改變而產生多普勒頻率的變化,長時間運動中還會受到加速度的影響。通常積累時間越長,多普勒頻率變化越大。

(3)目標穿過一個分辨單元的時間限制

目標在一個分辨單元內的回波數受到目標縱向和橫向穿過這個分辨單元的時間限制。若積累時間過長,則會產生跨距離單元走動,因此必須采取相關的運動補償措施,才能提供更多的脈沖數供積累。

2 基于運動補償的長時積累

從上節分析可知,目標經長時積累存在距離和多普勒走動,為了有效地對回波能量相參積累,就需要進行二維補償。對LFM信號的檢測,通常采用Radon-Wigner 變換,因為它有基于解線性調頻的快速算法,即將信號乘以exp(-jμt2/2)(μ 以各種不同值作搜索),并作傅里葉變換(FFT)。對于距離走動需對每一個距離單元進行包絡移動搜索,若搜索次數為N,同時還要對μ進行搜索,因此運算量相當巨大,幾乎不可能實時實現。為此,本文提出一種便于工程實現的簡易方法。

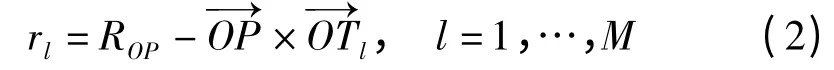

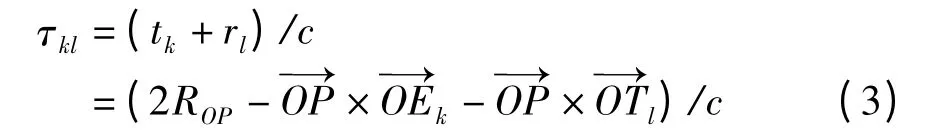

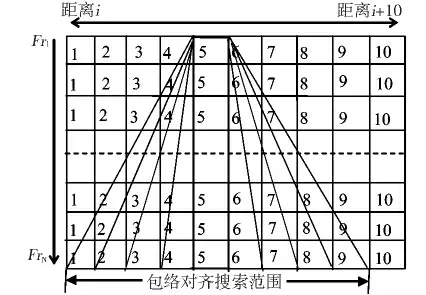

先對所有回波分組進行多普勒濾波。假定有(M×N)次回波,按順序分成M組,每組N個回波。在組內由于多普勒積累時間較短,可以不考慮組內多普勒頻率的變化。再對各組中相同多普勒通道信號進行非相參積累。考慮到長時間相干積累目標可能運動了幾個距離單元,需進行包絡對齊。在對N個回波進行多普勒濾波時,根據目標的最大可能速度進行被檢測距離單元的左右搜索,如圖2所示,這里假設目標在積累時間內是勻速直線運動。圖3、圖4 給出了計算機仿真結果。可見,若直接進行FFT 相參積累,目標的能量分散在多個距離單元和多普勒頻道里,經補償后能量匯聚一點,利于信號檢測。

圖2 包絡補償搜索示意圖

圖3 直接FFT 相參積累

圖4 包絡補償相參積累

3 基于DDR2和FPGA 硬件平臺的實現

由于SIAR 要在空間進行多波束堆積來覆蓋整個空域,系統會形成上千甚至幾千個波束,這就需要有很強的存儲和處理能力的硬件平臺作為支撐。硬件設計平臺采用基于大規模FPGA和DDR2的綜合處理插件。該板卡為SIAR信號處理系統的核心處理部分,采用FPGA+DSP的實現方案,由3 片FPGA 芯片、1 片DSP 芯片、若干大容量存儲器及相應的外圍電路構成,具有較強的運算能力和存儲容量,如圖5所示。硬件指標如下:

圖5 綜合處理板卡

(1)CPCI 接口:32 位33MHz,總線最大傳輸速度為132MB/s;

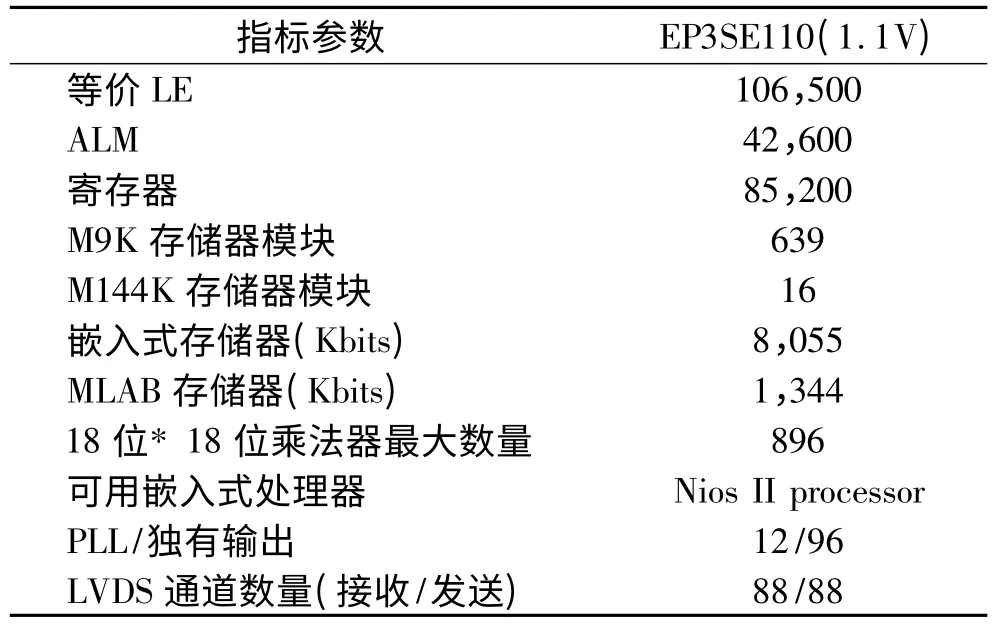

(2)FPGA:采用ALTERA 公司的EP2SGX90和EP3SE110,片內乘法器分別為384(9×9bit)和896(18×18bit)個,工作主頻最高可達500MHz;

(3)DSP:采用AD 公司的ADSP-TS201,工作主頻500MHz;

(4)DDR2:采用12 片MICRON 公司MT47H128-M16HG,存儲容量達24Gbit;

(5)可編程時鐘管理芯片:可編程、零延時,最多提供20個單端或10 對差分時鐘輸出;

(6)高帶寬光纖收發器:單通道傳輸速率可以達到2.5Gbps;

基于上述硬件平臺,用MATLAB 軟件產生一點頻測試信號。圖6為用Quartus II 軟件的SignaltapII 模塊采集綜合處理插件上FPGA 完成相參積累的測試結果。可以看出,當包絡補償匹配時信噪比最強,其他都處于失配狀態。

圖6 包絡補償仿真波形

表1 主要處理芯片參數

4 結束語

本文研究了稀布陣體制雷達長時相參積累問題,給出目標回波模型,分析長時積累所帶來的問題,提出了基于先分組多普勒濾波再非相參積累的新方法。該方法簡單易行,利于工程實現,能有效解決距離走動和跨多普勒問題,工程驗證表明了該方法的有效性。

[1]Abatzoglou T J,Gheen G O.Range,Radial Velocity,and Acceleration MLE Using Radar LFM Pulse Train[J].IEEE Trans.on AES,1998,34(4):1070-1083.

[2]Liu Yimin,Meng Huadong,Zhang Hao,et al.Motion Compensation of Moving Targets for High Range Resolution Stepped-Frequency Radar [J].Sensor,2008(5):3429-3437.

[3]劉崢,張守宏.步進頻率雷達目標的運動參數估計[J].電子學報,2000,28(3):43-45.

[4]Altera Corporation.Stratix II GX Device Handbook[EB/OL].http://www.altera.com.cn/literature/hb/stx2gx/stxiigx_handbook.pdf,2007,10.

[5]Altera Corporation.Stratix III Device Handbook[EB/OL].http://www.altera.com.cn/literature/hb/stx3/stx3_siii5v1.pdf,2009,5.

[6]Analog Devices,Inc.ADSP-TS201S[EB/OL].http://www.analog.com/static/imported-files/data_sheets/ADSP_TS201S.pdf,2006.12.

[7]Zhang S S,Zeng T,Long T,Yuan H P.Dim target detection based on keystone transform[C].Proceedings of the IEEE International Radar Conference,May 2005,889-894.

[8]Wang J,Zhang S H,Bao Z.On motion compensation for weak radar reflected signal detection[C].The 6th International Conference on Signal Processing,2002,1445-1448.