基于VPX架構和第四代Sharc DSP的SAR信號處理系統?

宋玉霞,甘峰,陳娟

(中國西南電子技術研究所,成都610036)

基于VPX架構和第四代Sharc DSP的SAR信號處理系統?

宋玉霞,甘峰,陳娟

(中國西南電子技術研究所,成都610036)

給出了一種基于VPX架構和ADSP-21469的合成孔徑雷達(SAR)實時信號處理機的設計與實現。處理機分別采用基于FPGA的交換機和各Lane接收緩沖再同步技術解決板內外數據交換和多Lane Serial RapidI/O同步難點,實現了實時寬帶雷達回波中頻采樣變換和SAR成像處理。測試表明,該信號處理機比相同處理能力的傳統處理機至少減少40 W功耗,并具有高達1 Gbyte/s的I/O吞吐力。

合成孔徑雷達;信號處理;中頻采樣;數字正交變換;功耗

1 引言

合成孔徑雷達(Synthetic Aperture Radar,SAR)是一種通過載體平臺的運動來模擬大孔徑天線獲得方位高分辨力的雷達。由于需采用孔徑時間內多個脈沖的回波進行二維壓縮獲得距離和方位向高分辨力,SAR雷達對信號處理的處理能力和I/O吞吐力提出了很高的要求。

傳統雷達信號處理系統常采用并行總線進行構建,這些總線包括PCI、CPCI、VME。由于并行線間的相位偏差難以控制在很小范圍,傳統共享并行總線逐漸成為高分辨SAR信號處理系統性能提高的瓶頸。而高速串行總線技術由于采用了時鐘打包、時鐘恢復以及信號的預加重和均衡處理技術,成功解決了數據線和時鐘線間的Skew和Jitter問題[1],將單對串行線的傳輸率提高到10 Gbit/s。

過去近10年,高性能雷達信號處理系統的處理器常采用Analog公司(ADI)的TigerSharc或Freescale(飛思卡爾)的PowerPC。但TigerSharc和PowerPC在擁有高處理能力的同時也具有很高的工作功耗,采用TigerSharc或PowerPC的處理系統往往面臨能源和散熱問題的困擾。

針對基于傳統并行總線和TigerSharc或PowerPC的信號處理系統的不足,本文設計了一種全新的SAR信號處理系統。該系統基于VPX架構,模塊間數據傳輸采用全雙工4 Lane Serial RapidI/O實現;主處理器采用ADI新一代Sharc DSP ADSP-2146X,系統處理性能高、功耗低。

2 VPX與ADSP-2146X

VPX(即VITA 46)是包括VPX基本標準和PCI Express on VPX、Serial RapidIO on VPX等多種標準的集合,其主要優勢為:IO數量巨增,可提供192個速度達5 Gbit/s的高速差分對;增強的供電能力,支持768 W/48 V;含3U和6U結構等。由于其同時具有更加堅固的機械結構和更強的冷卻能力[2],在一些苛刻的高傳輸需求領域有著誘人的前景。

ADI公司第四代Sharc處理器ADSP-21469的主要特點如下:支持高性能32 bit/40 bit浮點運算,內核工作頻率高達450 MHz,處理能力達2.7 GFLOPS;片內FIR、IIR、FFT硬件加速器潛在提升了計算能力。

3 SAR信號處理系統設計

SAR信號處理系統結構如圖1所示。該系統采用VPX架構,由3套完全相同的硬件電路板組成,每套板由1塊中頻采樣變換XMC背板和1塊3U成像處理載板組成。每塊XMC背板和載板間物理接口遵循VITA42.0規范并按VITA42.2設置高速Serial RapidI/O數據通信接口,3套板間物理電氣結構遵循VITA46.0并按VITA46.3 Serial RapidI/O設置高速Serial RapidI/O數據通信接口。

圖1 SAR信號處理系統結構圖Fig.1 Structure of SAR signal processor

中頻采樣變換板主要由2片ADS5474、1片XC5VSX95和2片SDRAM(每片容量256 Mbyte)組成。ADC轉換后的數字回波信號由XC5VSX95完成數字正交解調后送入SDRAM進行緩存。XC5VSX95提供8對高速串行差分數據鏈路Rocket I/O實現與載板通信,每對差分鏈路數據傳輸速率為2.5 Gbit/s。

成像處理板結構圖見圖2,板內共5個DSP節點,每節點包含1片ADSP-21469和128 Mbyte DDR2 SDRAM,單板峰值運算能力13.5 GFLOPS,ADSP-21469與DDR2間數據傳輸率900 Mbyte/s;每片DSP的2個Linkport口均接到板內FPGA(XC5VSX95)中,共提供1.66 Gbyte/s帶寬。節點間通過連接到FPGA的Linkport口實現分布式互連。每片XC5VSX95采用其32對高速串行差分數據鏈路實現4組4 Lane高速串行鏈路,其中1組與本板XMC進行通信,另3組用于板間通信。

圖2 成像處理板結構圖Fig.2 Structure of carrier board

系統采用無交換槽Full-Mesh互連方式,如圖1所示。圖1中各連接對均為4 Lane Serial Rapid I/O,各Lane峰值帶寬可達3.125 Gbit/s;各連接對間RD接TD,TD接RD,LaneX接LaneX。Full-Mesh拓撲結構使系統中模塊間能同時進行點對點信息交換,提高了數據傳輸效率;槽位間距20.32 mm。

4 算法和軟件流程

系統在研制中完成了掃描SAR成像處理和單脈沖SAR處理。本文以掃描SAR成像處理為例進行說明。

(1)中頻采樣變換

本系統輸入信號帶寬為150 MHz,中心頻率為560 MHz,根據帶通采樣定理,A/D采樣頻率選為320 MHz。直接由采樣序列交替得到的是在時間上相差1個采樣周期的信號正交分量和同相分量,需進行時域上插值或頻域濾波并進行符號修正。本系統選擇多相濾波進行正交變換,其處理流程如圖3(a)所示。

圖3 數字正交變換和SPECAN算法流程圖Fig.3 Flowchar of digital quadrature transformation and SPECAN algorithm

(2)SPECAN成像算法

SAR成像處理選用SPECAN算法,其流程如圖3(b)所示,其中多普勒中心估計采用時域相關法,即:

式中,v為平臺速度,θ為目標視線和平臺速度的夾角,fr為脈沖重復頻率,λ為雷達信號波長,r表示方位脈沖采樣序號。

距離徙動校正在頻域進行,徙動因子為RMC(n,m)=

式中,m∈[0,M-1]為方位向采樣點序號,n∈[0,N-1]為距離向采樣點序號,a為平臺加速度,fs為距離向采樣率。

方位向相位初補償采用慣導送來的徑向加速度直接運算,采用最大對比度法估計出調頻斜率^fdr后,得到方位向dechirp信號:

5 關鍵技術

(1)任務分配和數據交換

系統平臺采用多板多節點實現SAR成像處理,合理的任務分配和數據交換成為處理系統的關鍵環節。

系統采用多板多DSP并行處理方式實現實時處理。3塊板分別完成第3×(k-1)+n(n=1,2,3;k=1,2,3,…)個孔徑的成像處理,由和支路處理板完成板間數據分配。每板接收到各自子孔徑數據時,將第5×(k-1)+n(n=1,2,3,4,5;k=1,2,…,204)幀數據(每幀對應1個相參處理間隔的8 192點復數)送到第n個DSP節點進行距離向處理;距離向處理完成后DSP間需進行5次數據交換完成數據矩陣轉秩。

所有數據交換采用FPGA中設計的交換機實現。交換機設計如下:首先給每個需進行數據交換的節點分配ID號和兩個用于接收和發送數據緩沖的雙口RAM,每節點有若干離散線用于控制交換機。當節點間需發送數據時,發送端首先發出目的節點ID號,然后發出發數申請,交換機檢測到發數申請后,根據ID號檢測目的節點狀態,如接收口空閑,即可通過目的節點離散線向目的節點發起接收申請,目的節點響應申請,即可進行本次數據交換。

(2)多Lane Serial RapidI/O同步

中頻采樣變換后的數字基帶信號通過XMC槽位上的Rocket I/O接口實現。由于峰值數據率約800 Mbyte/s,需采用4 Lane Rocket I/O同時傳輸才能滿足要求。串行差分對間的同步問題成為必須解決的關鍵問題。

系統采用發送端數據對齊打包、并串轉換后通過串行鏈路發送;接收端分別采用從各Lane數據中恢復出來的時鐘接收數據并存入FIFO,然后再同時送入下級處理,從而成功解決了單元間數據傳輸同步問題,獲得10 Gbit/s比特率,有效數據率達1 Gbyte/s的單元間數據傳輸帶寬。

6 系統性能

經測試:本信號處理系統A/D有效位數均不低于10 bit(輸入信號頻率580 MHz,采樣率320 MHz);每路DDC變換后I、Q兩路基帶信號相位不平衡度小于0.01°、幅度不平衡度小于0.01 dB。

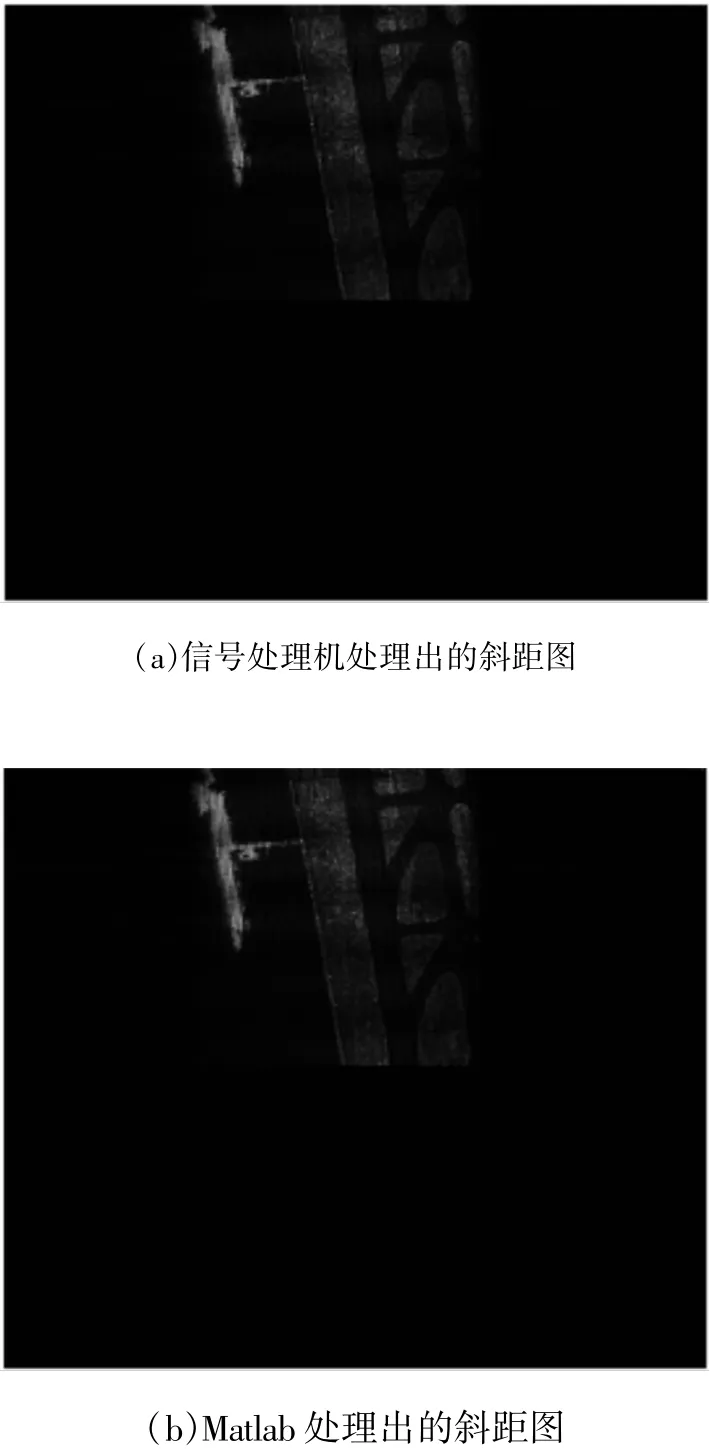

本信號處理系統采用SAR目標模擬器產生的SAR模擬回波數據進行了SAR成像處理,單板對1個子孔徑成像結果如圖4(a)所示,相同的模擬回波數據采用Matlab成像結果如圖4(b)所示。單板完成1個子孔徑掃描SAR成像處理耗時僅226.3 ms。

系統總工作功耗56 W,而同等處理能力的TS201信號處理系統功耗至少大于100 W。

圖4 從信號處理機獲得的SAR圖像和采用Matlab處理獲得的SAR圖像Fig.4 SAR imaging from processor and Matlab processing

7 結束語

本文設計的信號處理系統實現了寬帶雷達中頻信號采樣變換和SPECAN算法成像處理,已應用到某雷達系統中。本系統功耗低且采用高速串行總線實現模塊間數據傳輸,解決了傳統基于CPCI和TS201(或PowerPC)的信號處理系統I/O吞吐力瓶頸和高功耗問題。其中頻采樣板和信號處理板不僅性能強大,且分別采用XMC和VPX標準設計,硬件具有兼容性,整機具有擴展性。

[1]鄭東衛,陳矛,羅丁力.VPX總線的技術規范及應用[J].火控雷達技術,2009,38(4):73-77.

ZHENG Dong-wei,CHEN Mao,LUO Ding-li.Technical Specifications of the VPX Bus and Its Application[J].Fire Control Radar Technology,2009,38(4):73-77.(in Chinese)

[2]張天林,張思敏.CPCI-E與VPX總線標準的比較分析[J].工業控制計算機,2009,22(7):1-5.

ZHANG Tian-lin,ZHANG Si-min.Analysis of CPCI-E Comparing with VPX Bus Technology[J].Industrial Control Computer,2009,22(7):1-5.(in Chinese)

SONG Yu-xia was born in Jiajiang,Sichuan Province,in 1973.She received the M.S.degree in 2004.She is now a senior engineer.Her research direction is radar signal processing.

Email:syxhappy@yahoo.com.cn

甘峰(1984—),男,江西奉新人,2009年獲碩士學位,現為工程師,主要研究方向為雷達信號處理;

GAN Feng was born in Fengxin,Jiangxi Province,in 1984.He received the M.S.degree in 2009.He is now an engineer.His research direction is radar signal processing.

陳娟(1984—),女,湖北石首人,2008年獲碩士學位,現為工程師,主要研究方向為雷達信號處理。

CHEN Juan was born in Shishou,Hubei Province,in 1984.She received the M.S.degree in 2008.She is now an engineer.Her research direction is radar signal processing.

SAR Signal Processing System Based on VPX and Generation-IV Sharc DSP

SONG Yu-xia,GAN Feng,CHEN Juan

(Southwest China Institute of Electronic Technology,Chengdu 610036,China)

The design and realization of a real-time SAR(Synthetic Aperture Radar)signal processing system based on VPX and ADSP-21469 is given.Data transfer inside the system is resolved by switch built in FPGA and the synchronization of multi-lane Serial RapidI/O is resolved by synchronization after each lane receives and caches data.The real time orthogonal transformation and SAR processing for wide-band IF signal returned to radar is realized.Tests show that the power consumption of the system is decreased by 40W compared with traditional signal processing system,further more,the system attains 1Gbyte/s I/O throughput rate.

SAR;signal processing;IF sampling;digital orthogonal transformation;power consumption

TN957;TN911.7

:A

10.3969/j.issn.1001-893x.2012.06.013

宋玉霞(1973—),女,四川夾江人,2004年獲碩士學位,現為高級工程師,主要研究方向為雷達信號處理;

1001-893X(2012)06-0898-04

2011-11-14;

2012-04-06