SOI抗總劑量輻射加固工藝柵氧可靠性研究

高向東,吳建偉,劉國(guó)柱,周 淼

(中國(guó)電子科技集團(tuán)公司第58研究所,江蘇 無(wú)錫 214035)

1 介紹

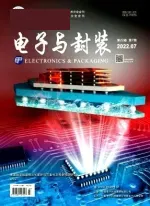

絕緣體上硅(SOI)由于其采用全介質(zhì)隔離技術(shù),相對(duì)于體硅工藝具有集成度高、速度快、抗干擾能力強(qiáng)的特點(diǎn)[1],同時(shí)徹底消除了體硅CMOS工藝的閂鎖(latch-up)效應(yīng),具有非常好的抗軟失效、瞬時(shí)輻照和單粒子翻轉(zhuǎn)能力[2~3],在抗輻射應(yīng)用領(lǐng)域有著廣闊前景。由于埋層二氧化硅(BOX)的存在,使得SOI器件在總劑量輻照效應(yīng)上比體硅差。為了改善SOI CMOS器件抗總劑量輻射能力,采用加固工藝的部分耗盡SOI CMOS技術(shù)能夠達(dá)到非常高的水平[4~10]。我們采用了埋層二氧化硅抗總劑量輻射加固工藝技術(shù),能夠使SOI CMOS器件抗總劑量輻射能力達(dá)到1Mrad(Si)。如圖1所示:(a)表示未采用抗總劑量加固工藝的SOI NMOS器件在輻射條件下的前柵轉(zhuǎn)移特性曲線;(b)表示采用抗總劑量加固工藝的SOI NMOS器件在輻射條件下的前柵轉(zhuǎn)移特性曲線。

圖1 是否采用抗總劑量輻射工藝的SOI器件輻射前柵轉(zhuǎn)移曲線

為了研究并提高抗輻射SOI CMOS器件的壽命,改善電路的可靠性,我們采用QBD(擊穿電荷量)對(duì)比了干氧化工藝和濕氧工藝的氧化層質(zhì)量,確定采用氧化層質(zhì)量相對(duì)更好的濕氧工藝。用斜階法對(duì)柵氧擊穿電壓進(jìn)行了分析,最后采用恒壓應(yīng)力對(duì)未采用抗總劑量加固和采用抗總劑量加固工藝的柵氧層質(zhì)量進(jìn)行評(píng)估,抗總劑量輻射加固工藝的柵氧在正常工作電壓下的壽命。

2 柵氧可靠性結(jié)構(gòu)

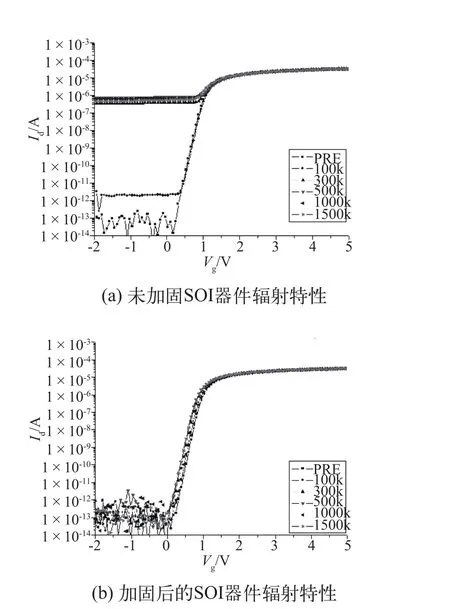

在我們的研究中,采用了PCM(process control measurement)測(cè)試版圖中,由n-well(n阱)、柵氧、多晶硅所組成的柵氧電容結(jié)構(gòu)如圖2所示,電容面積為90μm×300μm。

圖2 柵氧電容測(cè)試結(jié)構(gòu)圖

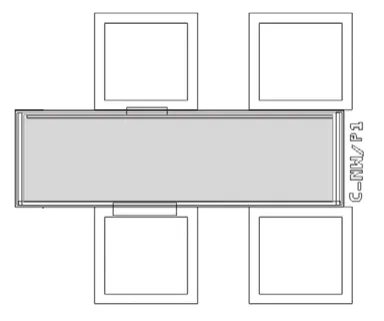

柵氧電容結(jié)構(gòu)主要形成的工藝步驟如圖3所示:(a)在SOI襯底材料片:Top-Si(頂層硅)=220nm,BOX(埋層二氧化硅)=400nm,RH抗總劑量輻射加固的埋層二氧化硅;(b)通過(guò)一次氧化(pad oxide)和一次氮化硅工藝(SiN),接著光刻有源區(qū),腐蝕氮化硅后,定義形成場(chǎng)區(qū)部分,如圖中(c)所示;進(jìn)行場(chǎng)氧化形成FOX場(chǎng)氧區(qū)域,去掉氮化硅材料,然后進(jìn)行離子注入形成n阱,形成電容測(cè)試結(jié)構(gòu)下電極,如圖中(d)所示;12.5nm柵氧化層生長(zhǎng),多晶硅淀積、多晶硅摻雜形成n+多晶硅,通過(guò)多晶硅光刻、腐蝕形成多晶硅柵,作為電容測(cè)試結(jié)構(gòu)的上電極,淀積LP SiO2350nm,通過(guò)各向異性腐蝕形成側(cè)墻(spacer),如圖中(e)所示;通過(guò)離子注入工藝形成n+重?fù)诫s區(qū),用于電學(xué)連接,如圖中(f)所示;完成PMD(金屬前介質(zhì)淀積)和接觸孔光刻、腐蝕,形成用于連接n+重?fù)诫s區(qū)和金屬布線的接觸孔,如圖中(g)所示;最后淀積金屬,并進(jìn)行金屬光刻、腐蝕后,形成金屬布線層,合金后完成多晶硅柵和n-well區(qū)域的連接,如圖中(h)所示。形成完整的柵氧電容測(cè)試結(jié)構(gòu),以下的測(cè)試結(jié)果將基于此結(jié)構(gòu)進(jìn)行測(cè)試分析。

圖3 柵氧電容結(jié)構(gòu)工藝流程簡(jiǎn)圖

3 實(shí)驗(yàn)與結(jié)果

3.1 干氧與濕氧工藝柵氧質(zhì)量比較

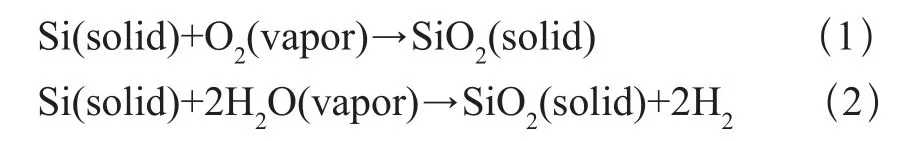

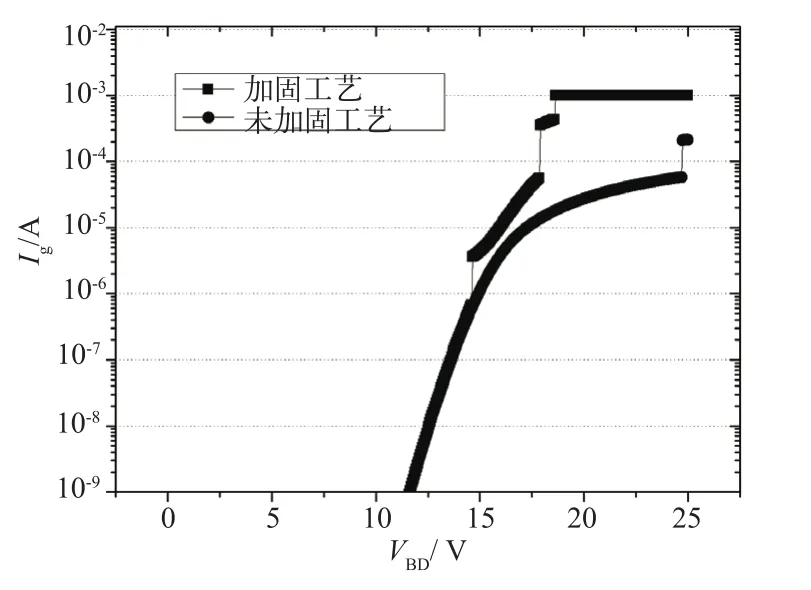

CMOS工藝對(duì)柵氧化層的厚度及氧化層質(zhì)量有很高的要求,通常采用干氧和濕氧氧化方式,氧化溫度通常選擇850℃~950℃,同時(shí)在氧化過(guò)程中加入摻氯氧化工藝以減少柵氧層中的可動(dòng)離子、提高氧化層質(zhì)量。干氧氧化采用氧氣與硅反應(yīng),如反應(yīng)式(1)所示;濕氧氧化采用氫氣與氧氣反應(yīng)形成水蒸氣,利用水蒸氣與硅反應(yīng),如反應(yīng)式(2)所示。

通過(guò)上述兩種工藝方法,我們制作了兩種12.5nm柵氧電容樣品,通過(guò)擊穿電荷量QBD測(cè)試,如圖4所示,圖中干氧氧化累計(jì)失效>80%,QBD>22C·cm-2,相對(duì)的濕氧氧化累計(jì)失效>80%時(shí),QBD>28C·cm-2。從表1可知干濕氧工藝的平均擊穿電場(chǎng)均達(dá)到了氧化層的本征擊穿,圖5所示為干濕氧工藝的VBD-η。

圖4 常規(guī)柵氧(干、濕氧)工藝的QBD-η

圖5 常規(guī)柵氧(干、濕氧)工藝的VBD-η

表1 常規(guī)柵氧工藝?yán)塾?jì)失效率及平均擊穿電場(chǎng)

3.2 抗輻射加固工藝的柵氧質(zhì)量

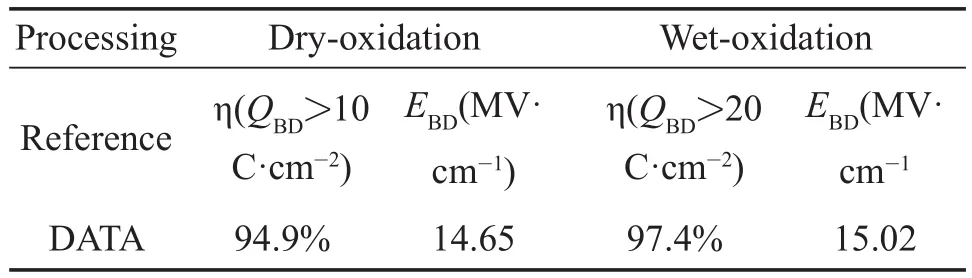

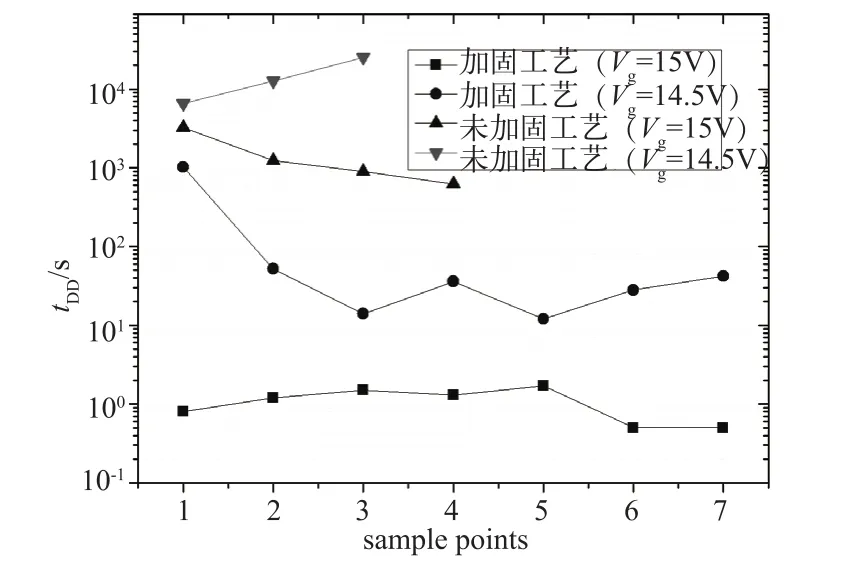

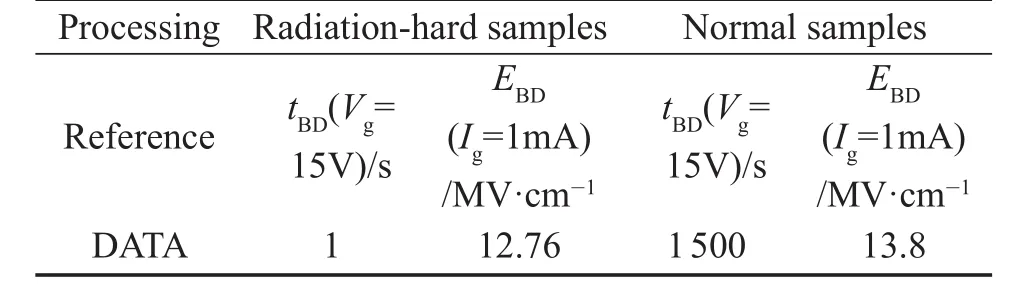

從上述柵氧工藝可靠性表征結(jié)果可見(jiàn),濕氧工藝的柵氧可靠性明顯優(yōu)于干氧工藝。因此,采用干氧化工藝來(lái)考察加固工藝對(duì)柵氧TDDB可靠性的影響更顯著。由圖6、7可知,因加固工藝誘導(dǎo)柵氧層結(jié)構(gòu)中的缺陷產(chǎn)生,在同等的應(yīng)力作用下(恒定電壓14.5V~15V和常溫度),加固工藝柵氧的經(jīng)時(shí)擊穿時(shí)間tBD較常規(guī)工藝柵氧偏低約103s。如表2所示,加固工藝柵氧的平均擊穿電場(chǎng)EBD較未加固工藝柵氧略低。

圖6 加固工藝對(duì)柵氧tBD的影響

圖7 加固工藝與未加固工藝的柵氧擊穿電壓

表2 加固?hào)叛豕に噒BD和擊穿電場(chǎng)

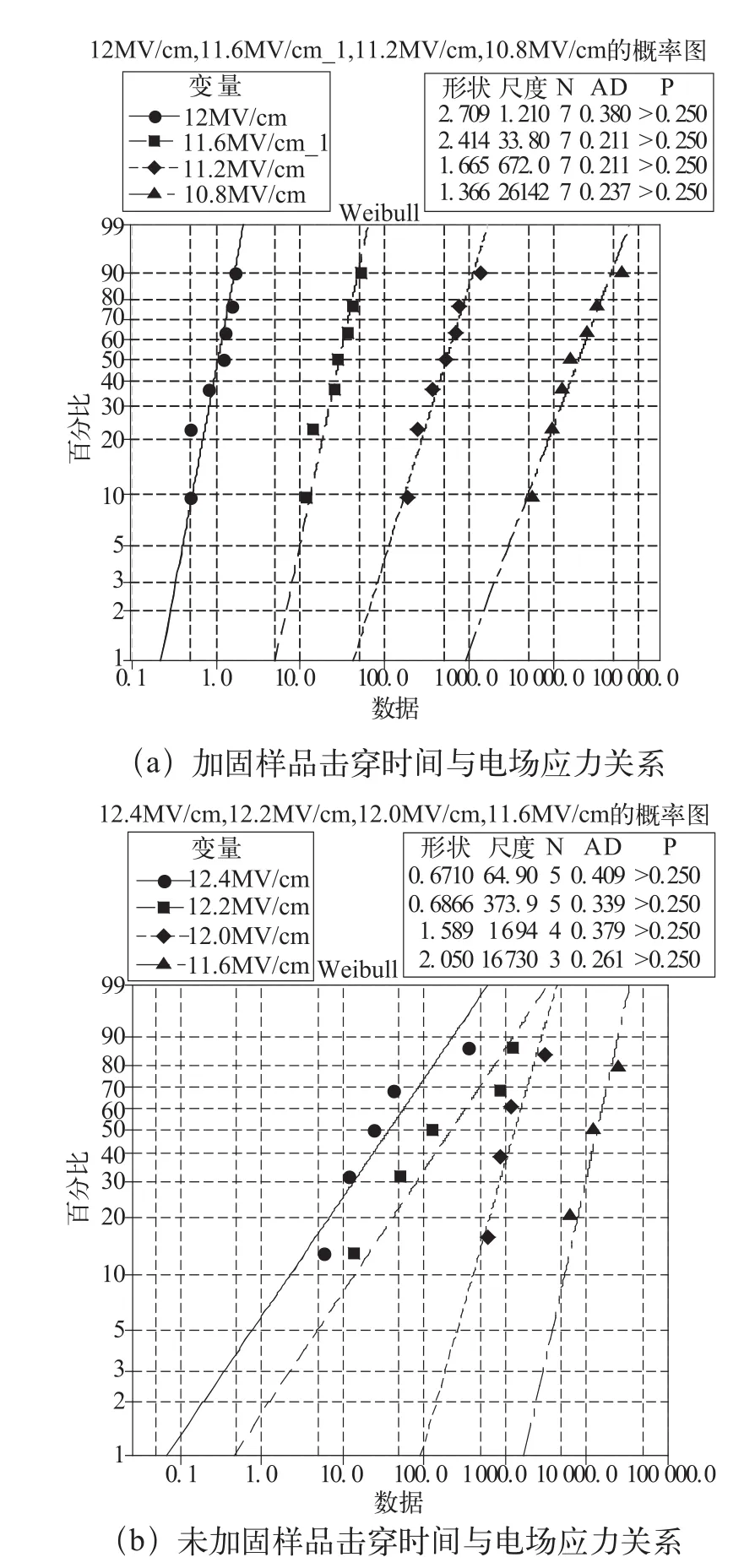

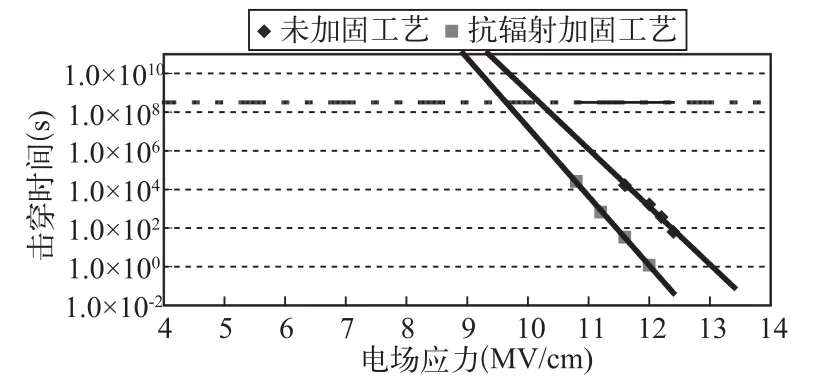

如圖8(a)中所示,采用加固工藝樣品的柵氧擊穿時(shí)間與電場(chǎng)應(yīng)力強(qiáng)度之間的關(guān)系采用weibull分布進(jìn)行統(tǒng)計(jì),取62.3%作為分布中心值;圖8(b)中表示加固工藝樣品的柵氧擊穿時(shí)間與電場(chǎng)應(yīng)力強(qiáng)度之間的關(guān)系。圖9將這兩個(gè)分布圖中的中心值和電場(chǎng)應(yīng)力強(qiáng)度做散點(diǎn)圖,采用指數(shù)模型進(jìn)行擬合,這兩種工藝的柵氧擊穿時(shí)間與電場(chǎng)應(yīng)力強(qiáng)度之間呈指數(shù)線性關(guān)系。通過(guò)模型倒推12.5nm柵氧在5.5V工作,即電場(chǎng)應(yīng)力在4.4MV·cm-1情況下的工作時(shí)間,我們能夠得到未加固工藝樣品柵氧壽命和加固工藝樣品柵氧壽命時(shí)間均遠(yuǎn)大于10年。

圖8 柵氧擊穿時(shí)間與電場(chǎng)應(yīng)力的分布關(guān)系圖

圖9 柵氧擊穿時(shí)間隨電場(chǎng)應(yīng)力的變化關(guān)系

4 討論

由于SOI材料與單晶硅材料存在一個(gè)特殊的埋層二氧化硅,抗總劑量輻射加固工藝針對(duì)埋層二氧化硅進(jìn)行材料改性,在頂層硅中引入缺陷。我們利用柵氧層擊穿電壓、擊穿電荷和恒壓法測(cè)試相關(guān)介質(zhì)擊穿等介質(zhì)可靠性的研究,發(fā)現(xiàn)抗總劑量輻射加固工藝對(duì)柵氧質(zhì)量存在影響。后續(xù)將針對(duì)不同SOI材料、柵氧電容結(jié)構(gòu)、柵氧厚度和不同溫度展開(kāi)研究,減少抗總劑量加固工藝在頂層硅中引入缺陷,提高柵氧介質(zhì)可靠性。

5 結(jié)論

本文對(duì)干氧和濕氧兩種工藝方法制作的柵氧質(zhì)量進(jìn)行評(píng)估,12.5nm干氧氧化的柵氧質(zhì)量要劣于濕氧氧化。采用干氧氧化工藝對(duì)抗總劑量輻射加固工藝的SOI柵氧層可靠性進(jìn)行對(duì)比評(píng)估,由于加固工藝誘導(dǎo)柵氧層結(jié)構(gòu)中的缺陷產(chǎn)生,在同等的應(yīng)力作用下(恒定電壓14.5V~15V和常溫情況),加固工藝柵氧的經(jīng)時(shí)擊穿時(shí)間tBD低于常規(guī)工藝柵氧。加固工藝柵氧的平均擊穿電場(chǎng)EBD較常規(guī)工藝柵氧略低,達(dá)到氧化層本征擊穿。并通過(guò)模型外推的方法得到抗輻射加固工藝柵氧的TDDB壽命能夠充分滿(mǎn)足SOI CMOS器件10年工作壽命的要求。

[1] Auberton-Herve A J.SOI: materials to systems[J].IEEE International Electron Device Meeting Technical Digest,1996:3.

[2] Brady F T, S cott T, Brown R, et al. Fully-depleted submicron SOI for radiation hardened application[J]. IEEE Trans Nucl Sci, 1994, 41:2304.

[3] Hatano H. Radiation hardened high performance CMOS VlSI circuit design[J].IEEE Proceedings-G, 1992, 139:287.

[4] Zhang Guoqiang, Liu Zhongli, Li Ning, et al. Influence of fluorine on radiation-induced charge trapping in the SIMOX buried oxides[J]. Proceeding of 7th International Conference on Solid-State and Integrated Circuits Technology, 2004, 2:847.

[5] Hughes H, McMarr P. Radiation-hardening of SOI by ion implantation into the buried oxide[P].US Patent.No.5795813.

[6] White M H, Adams D A, Murray J R, et al. Characterization of scaled SONOS EEPROM memory devices for space and military systems[P]. Non-Volatile Memory Technology Symposium, 2004:51

[7] Wu Jun-feng, Zhong Xing-hua, Li Duo-li. Improved breakdown voltage of partially depleted SOI nMOSFETs with half-backchannel implantation[J]. Chinese Journal of Semiconductors, 2005, 26(10):1875.

[8] Ohno T, Izumi K, Shimaya M, et al. CMOS/SIMOX devices having a radiation hardness of 2Mrad(Si)[J]. Electron Lett,1987, 23:141.

[9] Liu S T, Jenkins W C, Hughes H L. Total dose radiation hard 0.35μm SOI CMOS technology[J]. IEEE Trans Nucl Sci, 1990, 37:2013.