基于FPGA的電容數據采集系統的設計

張印強,孫冬梅,程明霄

(南京工業大學 自動化與電氣工程學院,南京 210009)

0 引言

電容式傳感器廣泛地應用于航空航天、軍事、工業、醫療等領域, 在很多場合下電容量只有幾pF到幾百pF,傳感器的輸出信號微弱,如何提高測量靈敏度和信噪比成為微弱電容檢測的關鍵[1]。

本文介紹了一種以FPGA為核心的電容數據采集系統,它利用基于載波調制的電荷放大電路完成電容/電壓轉換,抗干擾性較好。與傳統的模擬檢測系統相比,系統的載波生成和信號解調都在FPGA內部實現,載波穩定度更高, 解調誤差更小,高分辨率A/D轉換芯片的選用進一步保證了精度。

1 系統組成

系統以FPGA為核心集成了差動電容傳感器、電源電路、信號調理電路、A/D 轉換電路、D/A 轉換電路等功能模塊。系統整體結構如圖1 所示。

圖1 系統結構簡圖

信號調理電路主要用于對差動電容的變化進行載波調制、交流放大、濾波等預處理, 保證系統有較寬的測量范圍, 為AD轉換提供高質量的信號;AD轉換電路負責把信號調理電路的輸出信號轉化為數字量,送FPGA進行處理;FPGA模塊用于外設控制、載波生成、數字解調以及數據傳輸。

2 系統硬件設計

2.1 信號調理電路

2.1.1 電容/電壓轉換電路

為抑制共模噪聲,增強抗干擾性能,系統采用連續積分型電容檢測電路將差分電容的變化調制到正弦載波的幅度上[2,3],再利用相干解調的方法得到電容變化量,電路如圖2所示。

C6和C8構成差分電容;R2與R3為反饋電阻,阻值相等,C4和C9為反饋電容,電容值相同;R1為標準電阻,用于設置放大器U1的增益;它們與U1、U2構成電荷放大器,將差分電容的變化量調制到載波幅度上。Vs為正弦載波信號,可表示為Vsinωct。一般反饋電阻R2很大,R2>>1/ωcC4,設U1的放大倍數為A,當差分電容變化時,可得到輸出電壓Vo的表達式如式(1)所示:

圖2 電容/電壓轉換電路

電容/電壓轉換電路的輸出正比于差分電容的變化量,電容的變化被調制到輸出信號Vo的振幅之中。為保證測量精度以及小型化需求,U1選擇AD8221,U2選擇雙通道精密運算放大器OP2177。AD8221是美國模擬公司推出的儀表放大器,其增益誤差典型值小于20ppm且10KHz條件下的共模抑制比高達80dB。

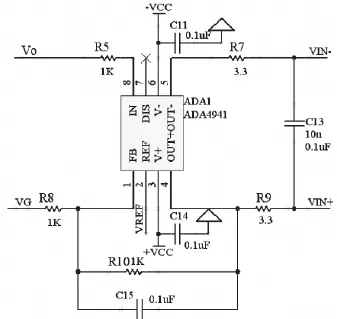

2.1.2 差分信號調理電路

由于A/D轉換器必須采用全差分驅動輸入,且差分輸入的共模電壓以及對差分輸入的限制與基準電壓有關,系統采用差分運算放大器ADA4941將電荷放大電路的輸出轉換為全差分信號后再與AD轉換器的差分輸入接口連接,差分信號調理電路如圖3所示。

ADA4941采用正負10伏的電源進行供電,選用0.1μF的旁路電容降低干擾,通過調整R8和R10這兩個電阻的阻值可調整運算放大器的增益。8腳為輸入電壓引腳,與電容/電壓轉換電路的輸出引腳相連;2腳VRef設定差分信號的共模電壓,這里為2.5V,5腳和4腳為差分輸出信號,其輸出電壓如式(2)所示,差模輸出電壓如式(3)所示。

圖3 差分放大電路

2.2 電源電路

系統所用到的電源主要有5V、3.3V、2.5V、1.8V、1.2V,選用SPX1117提供5V、2.5V、1.8V電壓信號,選用AMS1117提供1.2V電壓信號,利用開關型穩壓電源芯片LM2576提供3.3V信號。3.3V電源電路如圖4所示。

圖4 3.3V電源電路

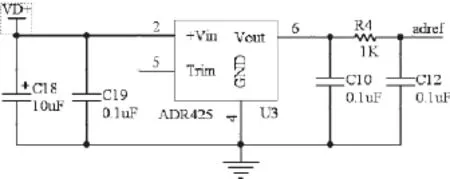

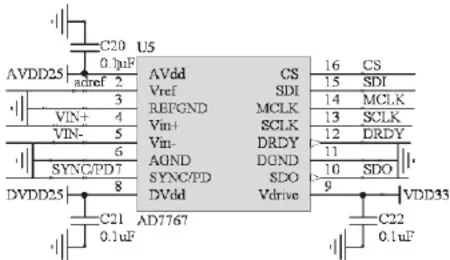

2.3 A/D轉換電路

為保證數字解調的精度,選用高精度24位A/D 轉換芯片AD7767對信號調理電路輸出的差分驅動信號進行采樣。AD7767為高性能24位過采樣SAR型模數轉換器,片內集成數字濾波器(包括線性相位響應),通過過采樣輸入來消除帶外噪聲,具有較寬的動態范圍和輸入帶寬,適用于超低功耗數據采集應用。

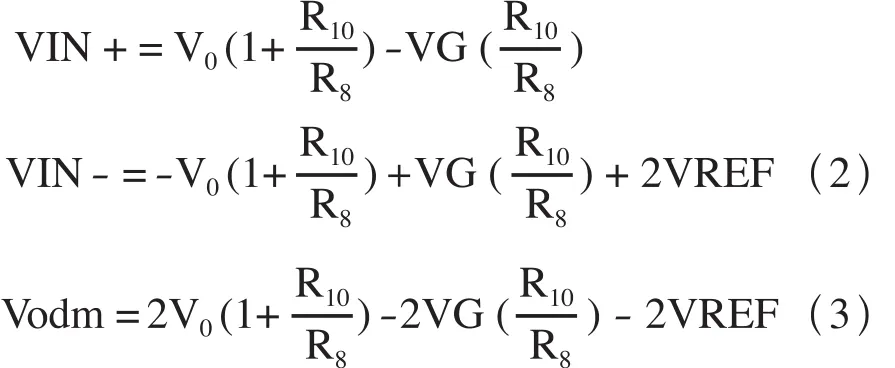

AD7767的工作電壓為2.5V,標準基準電壓為5V,為了保證A/D轉換的精度,選用ADI公司的高精度電壓參考源芯片ADR425提供基準電壓,它具有低噪聲、高精度和出色的長期穩定特性,輸出電壓5V。基準電壓產生電路如圖5所示,輸入電壓引腳和輸出電源引腳均由去耦電容與地連接。

圖5 基準電壓電路

AD7767的外圍電路如圖6所示,參考電壓由adref提供;其模擬工作電壓和數字供電電壓均為2.5V,I/O口電壓為3.3V,均通過去耦電容與地連接。CS引腳為片選輸入引腳,并充當SDO引腳的使能信號。數據輸出采用串行接口方式,輸出數據的協議為SPI協議。串行接口用到SCLK、MCLK、DRDY、SDI、SDO等信號,其中SCLK為串行時鐘輸入,MCLK為主時鐘輸入;DRDY為數據就緒信號,低電平有效;轉換后的數據通過引腳SDO移位輸出。SDI為串行輸入引腳,主要用于多個器件的菊花鏈連接。時鐘信號、片選信號、串行輸出控制信號都由FPGA進行控制。

圖6 AD7767的外圍電路

2.4 D/A轉換電路

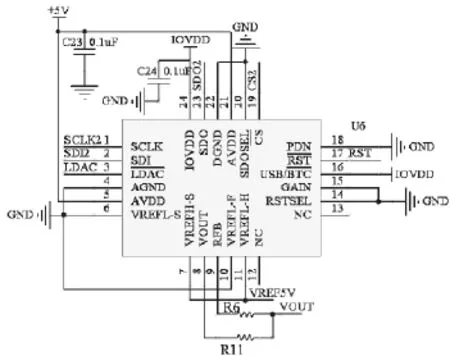

選用TI公司的DAC9881將FPGA內產生的數字載波信號轉換成模擬信號,其電路如圖7所示。

圖7 D/A轉換電路

TI 公司的DAC9881是高精確度的D/A轉換芯片,分辨率為18 位,典型功耗為4mW[4]。

2.5 FPGA模塊

FPGA芯片選用Altera公司生產的Cyclone系列的EP3C25E144C8, 其芯片模擬工作電壓為1.2V和2.5V,分別為模擬鎖相環PLL和模擬電壓端供電;數字工作電壓為3.3V和1.2V。控制程序存儲在配置芯片EPCS16中。

3 系統軟件設計

3.1 DDS算法

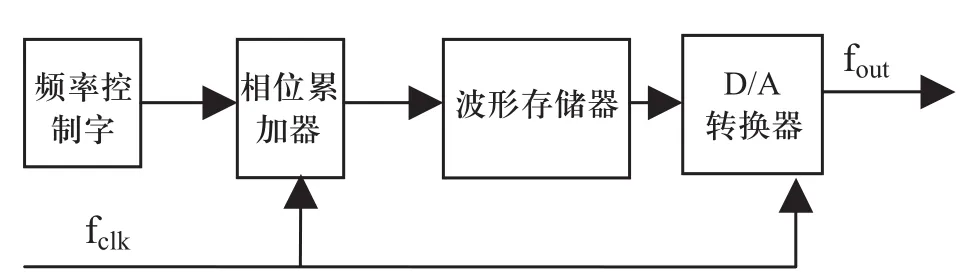

直接數字頻率合成(DDS)技術[5]是一種從相位概念出發直接合成所需波形的一種新的全數字頻率合成技術,其結構如圖8所示。

圖8 DDS的結構框圖

DDS系統主要由相位累加器、波形存儲器和數模轉換電路等部分組成。相位累加器由加法器和累加寄存器級聯構成,在時鐘脈沖的控制下將頻率控制字與累加相位相加,得到信號的新相位。相位累加器的輸出作為波形存儲器的相位地址,通過查找表得到對應的正弦值或余弦值,經數模轉換器將數字量形式的波形幅值轉換為模擬量。

DDS算法實現的部分代碼如下:

always @ (posedge clk or posedge rst)

begin

if (rst)

ADD_1<=0;

Else if(we) //ADD_1為頻率控制字

ADD_1<= data;

end

always @ (posedge clk or posedge rst)

begin

if (rst)

ADD_2<=0;

Else if(en)

ADD_2<=ADD_2+ADD_1; //相位累加器

end

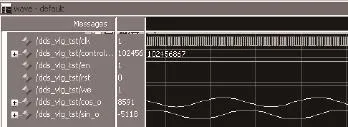

DDS載波生成信號的modelsim仿真結果如圖9所示,sin_o和cos_o代表正弦值和余弦值。

圖9 DDS模塊的modelsim仿真圖

3.2 AD7767的采樣控制

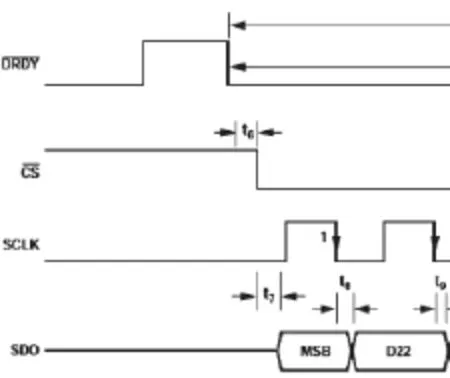

AD7767通過串行數據輸出引腳(SDO)輸出其數據轉換結果。SCLK是該器件的串行時鐘輸入;DRDY線用作狀態信號;CS信號是SDO引腳的選通信號。數據讀出的工作時序如圖10所示。

有效的數據準備好時,DRDY被置為低電平。CS引腳變為低電平后開始啟動串行數據傳輸,數據在時鐘信號控制下串行輸出,FPGA 提供AD7767工作所需的時鐘信號和控制信號。在QUARTUS中設計的A/D控制模塊如圖11所示。

圖10 ADS1278的串行時序圖

圖11 AD控制模塊圖

4 結束語

基于FPGA的電容數據采集系統運用數字技術生產載波和實現解調,結構簡單,精度高,具有一定的實用價值。

[1] 劉俊, 徐佩, 石云波. 微弱電容信號的離散頻率測試方法及其硬件電路的實現[J]. 兵工學報, 2005, 26(4): 500-503.

[2] 周曉奇, 鄭陽明, 金仲和, 等. 基于FPGA的數字式電容檢測系統[J]. 傳感技術學報, 2008, 21( 4): 698-699.

[3] 龐士信, 王超, 匡石. 基于FPGA的硅電容傳感器調理模塊設計[J]. 儀表技術與傳感器, 2010, (10): 1-2.

[4] 魏永旺, 羅海波, 鄒彥. 18位數/模轉換芯DAC9881的原理與應用[J]. 現代電子技術, 2009, (14): 167-169.

[5] 湯文亮. 基于CORDIC算法的高速高精度DDS研究與實現[J]. 制造業自動化, 2011, 33(3): 104-106.