基于可重構計算技術的ASIP設計與實現

宋奐寰,王樹宗,邵利兵

(海軍工程大學兵器工程系,湖北 武漢 430033)

基于可重構計算技術的ASIP設計與實現

宋奐寰,王樹宗,邵利兵

(海軍工程大學兵器工程系,湖北 武漢 430033)

為了加速計算密集或數據密集類算法,設計了Kahn線程定義的虛擬指令,以及嵌入式粗粒度可重構陣列流水線處理器的體系結構。通過指令流水線設計,實現虛擬指令的并行執行,將指令級并行擴展為線程級并行。系統運行時,采用訂閱/發布機制作為可重構陣列的通信機制,利用可重構系統可重復配置的特點,提高了系統的計算效率。通過仿真實驗驗證了基于可重構計算技術的流水線處理器結構的有效性。

可重構計算;粗粒度可重構陣列;循環指令流水線;訂閱/發布機制

0 引言

可重構計算兼顧定制計算的高效性與通用計算的靈活性,是一種新型的時空域計算模式。在可重構計算系統中,通過硬件的時域復用完成復雜的功能定制和系統任務。通過設計合理的重構粒度,可以提高硬件的計算能力[1]。

文獻[2]介紹一種粗粒度可重構多核協處理器體系結構,用于加速計算密集或數據密集類算法。在該結構中采用具有猜測執行機制的循環自動流水線技術,將流水線并行執行和數據驅動執行緊密結合。采用以循環程序為單位的固定指令多數據流執行模式,在循環執行期間,每個單元固定執行一種指令,配置信息量減少,支持快速動態重構。設計了多種特殊數據傳遞指令,如非平衡數據復制指令、數據選擇指令等,充分利用循環迭代內部、循環迭代間的數據相關,開發數據重用性,減少對存儲器帶寬的需求。文獻[3]提出了一種數據驅動處理器陣列結構,該結構能有效平衡存儲和計算,適合用于在FPGA上實現高性能的算法加速。

本文設計了循環指令流水線和循環算數流水線,以數據驅動的方式填充和排空循環流水線。通過Kahn進程定義的虛擬指令使流水線在嵌入式可重構陣列上自動運行。利用可重構系統的通信網絡具有可配置的特點,采用訂閱/發布通訊機制,靈活地改變網絡的拓撲結構。

1 預備知識

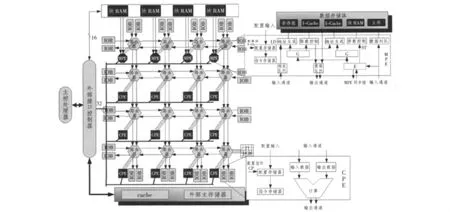

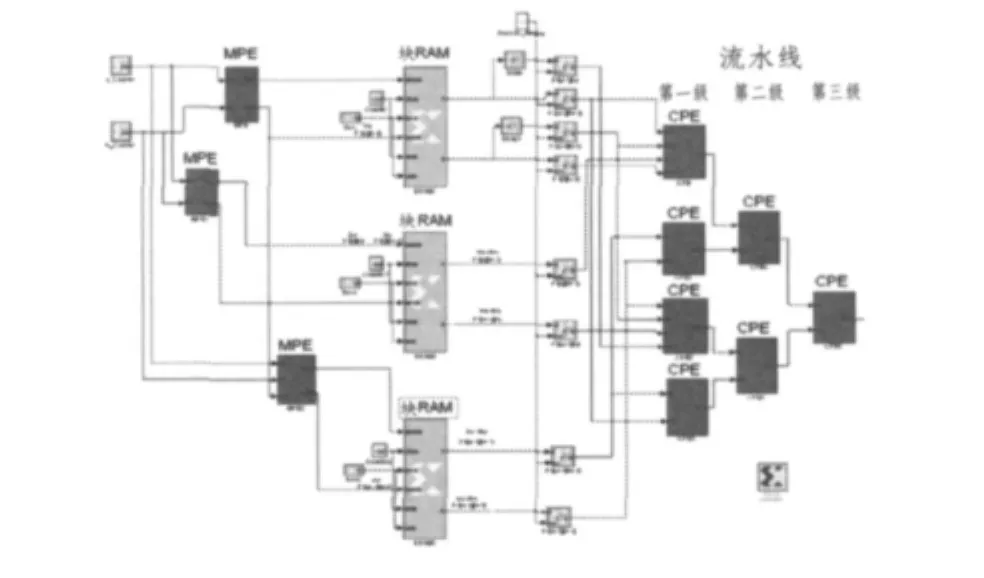

專用指令集處理器(ASIP)綜合了軟件占優和硬件占優2類系統的特點,能在微處理器和專用集成電路間進行權衡,提供了嵌入式設計的一種良好解決思路;ASIP可通過定制獲得需要的功能,成為通用處理器和ASIC的替代者[4-5]。粗粒度可重構陣列采用 FPGAs或其他可編程硬件,可配置邏輯塊(CLB)是FPGA內的基本邏輯單元。若干個功能部件CLB有規則地組成FPGA邏輯單元陣列結構,形成一個可配置處理單元(RU),以完成用戶指定的邏輯功能。粗粒度可重構陣列以RU為一個可配置單位,RU是硬件向用戶提供的最小編程接口。所有建立在粗粒度可重構陣列之上的設計單元都要被翻譯為這些RU器件,否則是不可實現的。粗粒度可重構陣列作為協處理器,嵌入專用指令集處理器,實現基于粗粒度可重構陣列的流水線處理器(見圖1)。

粗粒度可重構陣列作為主控處理器的協處理器,主控處理器用于執行控制可重構邏輯或執行不能被加速執行的編程代碼,粗粒度可重構陣列作為主控處理器數據通道中定制的功能單元使用。當主控處理器遇到密集型計算時,向粗粒度可重構陣列定制可配置處理單元。可配置處理單元分為用于循環控制和存儲訪問控制的MPE和用于計算任務的CPE。處理單元與互聯網絡上的路由器相連。接口控制器是連接主控處理器、外部主存儲器和粗粒度可重構陣列處理器的橋梁,用于粗粒度可重構陣列加載配置信息、以DMA方式在外部主存儲器和內部數據存儲器之間加載數據或讀取結果,或是主控制處理器向粗粒度可重構陣列發送啟動命令及查詢運行狀態。

為了最大限度地利用可重構硬件,粗粒度可重構陣列上的密集型計算必須具備重復計算的特點,即對于多組輸入數據執行的操作是相同的,因此本文引進流水線作為粗粒度可重構陣列上的任務單元。

2 粗粒度可重構陣列上的流水線

流水線處理器是當前指令集處理器設計中廣泛應用的技術[6]。流水線就是將一個操作分解為一些小規模的基本操作,并且在基本操作之間增加適當的寄存器,把基本操作產生的中間值存放在這些寄存器中,并在下一個時鐘周期內繼續運算。在流水線處理器設計中,要流水化的運算就是每個指令周期所要進行的工作。流水線設計的主要任務可以看做是將邏輯指令周期映射到物理機器周期。換句話說,就是將指令周期所對應的運算分成一個子運算的序列,由流水線的各段運行。流水線的類型主要分為指令流水線和算術流水線2種。

2.1 指令流水線設計

圖1 基于粗粒度可重構陣列的流水線處理器Fig.1 Pipeline processor based on coarse-grained reconfigurable array

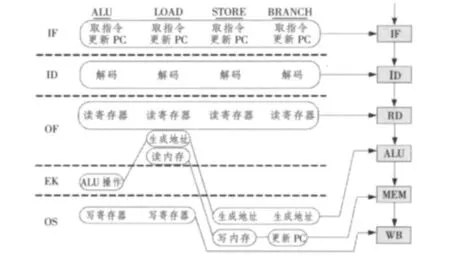

一個典型的指令周期按功能可以劃分為取址(IF)、譯碼(ID)、取操作數(OF)、執行(EX)和存儲(OS)等5個基本運算分量。指令流水線的設計任務是將以上運算分量進行劃分或組合,使模塊執行時間均衡,以平衡指令流執行時間。指令流水線重復處理的指令具有不同的指令類型:算數操作(ALU)、數據移動(LOAD、STORE)和指令定序(BRANCH)。統一不同的指令類型,將不同資源需求有效地整合到1條指令流水線中去,使得這條流水線適合于所有的指令類型。整合的目標是盡量減少流水線所需要的資源數,同時盡量提高流水線中所有資源的利用率,整合后的TYP指令流水線[6]如圖2所示。

圖2 TYP指令流水線Fig.2 TYP instruction pipeline

專用指令集處理器根據指令的相關性,在可重構陣列上定制指令流水線,只要程序計數器PC所指向的指令地址不為空,就會有指令不斷填充TYP指令流水線。用虛擬指令描述TYP指令流水線的行為,如表1所示。指令流水線所訪問的存儲體采用分層結構,即ALU寄存器、I-cache(專用于存放指令)、D-cache(專用于存放數據)、外部主存儲器。ALU寄存器、I-cache和D-cache只有1個端口,因此在1個時鐘周期內,只能對其執行讀(LD)或寫(ST)指令之一。多端口的主存儲器在1個時鐘周期內即可進行讀操作又可進行寫操作,因此除了執行LD和ST指令之外,還可執行MM指令。

2.2 算術流水線設計

當指令流水線ID段解析到循環體程序時,可以通過流水線向量化算法[7],將串行執行的循環體展開成可并行執行的程序段,然后根據數據流圖,為粗粒度可重構陣列定制循環算術流水線功能單元。只要循環未結束,就會有數據不斷填充算術流水線。用虛擬指令描述算術指令流水線的行為,如表2所示。

?

表1和表2的虛擬指令有很多是相同的,采用Kahn進程[8]實現這些虛擬指令。將這些虛擬指令映射到基于嵌入式粗粒度可重構陣列的流水線處理器中:①LD指令和ST指令根據接口地址Address_in和Address_out的地址格式在MPE中訪問不同的存儲體;②流水線啟動(G)/關閉(E)指令、F指令和G與數據存儲體緊密相關,因此它們集中在MPE中實現;③用于算術和邏輯運算的Compute指令集中在CPE中實現;④Jump指令根據給出的地址,更新I-cache的內容和程序計數器PC的值,因為Jump指令與存儲體密切相關,所以在MPE中實現;⑤F,Join與J指令分別采用CPE提供的邏輯運算O=I?L:R和O=L op R來實現。

2.3 流水線時鐘周期的計算

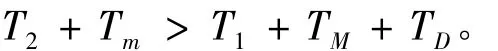

時鐘是流水線執行的控制器,也是流水線深度的決定因素之一。流水線的時鐘周期也叫機器周期。流水線的每一級是由1組組合邏輯電路F和1個寄存器組成。在實現過程中,為減少信號的傳輸延遲和節約邏輯資源,這個寄存器通常由CLB單元中的觸發器D實現。定義TM為通過F的最大傳輸延遲,即通過最長信號路徑的延遲;Tm為通過F的最小傳輸延遲,即通過最短信號路徑的延遲;TD為正確建立時鐘信號所需要的額外時間,包括必要的建立和保持時間,以保證正確的鎖存,同時還包括可能的時鐘扭曲,即到達不同觸發器的時鐘沿的最大時差。假設1組信號X1自T1時刻作用在流水線某一級的輸入端,那么F的輸出最遲將在T1+TM時刻有效,要保證D的正確鎖存,F的輸出信號在T1+TM+TD時刻必須仍然有效。當第2組信號X2自T2時刻作用在F的輸入端時,最快只要到T2+Tm時刻就能傳到鎖存器L。要保證第2組信號不覆蓋第1組信號,必須滿足公式[9]:

上式可改寫為

其中:T2-T1為最短時鐘周期。因此流水線的時鐘周期T必須比TM-Tm+TD大,最大時鐘頻率不能超過1/T。

2.4 通信機制

訂閱/發布通信機制由生產者、消費者和事件通知服務組成[9]。生產者和消費者分別是對產生事件對象和消費事件對象的統稱,事件通知服務即通常意義上的訂閱/發布中間件。消費者以訂閱的方式向事件通知服務注冊,表達對特定事件的興趣,生產者發布事件到事件通知服務,并將生產的數據送到數據池中。事件通知服務充當生產者和消費者的中介,負責訂閱的管理,根據訂閱過濾事件,并以通知的形式發送事件到感興趣的消費者,消費者收到通知后,從數據池中取出所需的數據,如圖3所示。

圖3 訂閱/發布通信模型示例Fig.3 Examples of communication model

核即是訂閱/發布機制的生產者/消費者。由于訂閱/發布系統具有松耦合、匿名、多對多通信和可擴展的特點,符合粗粒度可重構陣列的通信網絡是可配置的要求,因此是基于嵌入式粗粒度可重構陣列的流水線處理器體系結構理想的通信模式。數據存儲體(塊RAM,觸發器,用于數據存儲的查找表)充當數據池的角色。粗粒度可重構陣列內嵌有數字時鐘管理模塊。將時鐘頻率不同的設計劃分到不同的時鐘區域,通過異步FIFO以及雙口RAM為不同的時鐘區域建立不同的數據池,設計轉發器實現不同數據池間數據的傳輸,這樣可避免信號直接跨越不同的時鐘域并在一定程度上化解流水線相關。Xilinx提供了片上RAM,特別是大量的塊RAM,可以配置成雙口RAM或ROM,它們存儲量大、速度快且不占邏輯資源[10]。將這些塊RAM資源以數據池的形式分配給時鐘頻率相同的可配置的處理單元,當某個核所需的初始數據在數據池中被初始化后,該核自動被啟動執行。若干個核同時配置到粗粒度可重構陣列空間,就形成了循環流水的自動執行,提高了數據的吞吐率和并發程序的執行效率。

3 實驗與性能分析

基于可重構計算技術的ASIP的軟件實驗環境包括 Modelsim SE 6.5, Simulink, Xilinx System Generator(系統生成環境)和Xilinx ISE 9.1i(系統綜合環境),硬件實驗環境包括Xilinx公司的大容量FPGA芯片 Virtex4xc4vsx35-10ff668,32MB SDRAM和PCI橋。

首先,通過PCI橋將FPGA芯片與主控處理器相連,SDRAM與FPGA間有64位數據通路。該實驗平臺能運行應用程序并提供時鐘準確的運行結果。其次,用Verilog硬件描述語言實現粗粒度可重構陣列的體系結構。用模塊實現自定義的IP核(MPE核、CPE核),用雙口RAM實現1個系統周期同時讀出2個數據。

用本文提出的思想,在嵌入式粗粒度可重構陣列的流水線處理器實驗平臺上實現邊界檢測算法,過程如下:

步驟1 在流水線處理器上執行高級語言程序。高級語言程序的每一條語句依次通過圖2所示的TYP流水線。當解碼得到的指令為循環指令時,進入步驟2。

步驟2 將循環程序轉換成用虛擬指令表示的偽代碼。將循環程序利用表1和表2所示的虛擬指令轉換成偽代碼。

步驟3 畫出虛擬指令表示的偽代碼數據流圖。

步驟4 使用Simulink,Xilinx System Generator以及IP核實現步驟3的數據流圖。由于該段程序不存在流水線相關,所以這個3級流水線使系統的吞吐率提高了3倍;利用粗粒度可重構陣列上的塊RAM,有效地緩解了讀取存儲器的瓶頸問題。

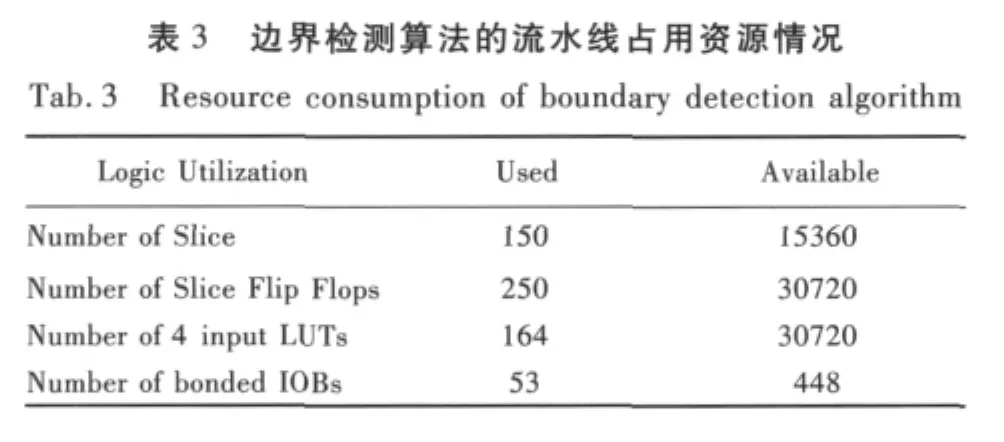

步驟5 利用Xilinx ISE進行設計綜合。由主控處理器通過PCI總線寫入FPGA芯片,最終邊界檢測算法在基于可重構計算技術的ASIP上運行,循環流水線占用FPGA資源情況如表3所示,可見基于可重構計算技術的ASIP設計方法在計算速度和占用資源方面的有效性。

?

4 結語

本文的創新點有:將可重構計算技術應用于ASIP實現集成電路的定制;在可重構陣列上引入流水線技術,實現指令的并行執行;采用訂閱/發布通信機制實現并行任務間的通信。具體方法有:采用Kahn進程定義虛擬指令,在專用指令集處理器上執行。通過虛擬指令在循環流水線上的并行執行實現了Kahn進程的并行執行。粗粒度可重構陣列既可以執行循環算術流水線,執行數據密集或計算密集類算法,又可以執行循環指令流水線,執行指令的取指、譯碼、取操作數、執行和存儲等操作。體系結構采用模塊化設計,為循環流水線設計的可配置處理單元是最小的資源分配單位,采用多種可配置指令,實現了虛擬指令的功能。訂閱/發布通訊機制使得分布在粗粒度可重構陣列之上的各個處理單元擁有靈活的拓撲網絡結構和共享的數據池,當某處理單元所需的數據準備完畢后,由數據驅動流水線自動執行。實驗結果驗證了基于可重構技術的ASIP方法的可行性與有效性。

圖4 使用Simulink,Xilinx System Generator實現數據流圖的仿真程序Fig.4 Simulation program of data flow diagram in Simulink,Xilinx System Generator environment

[1]孫康.可重構計算相關技術研究[D].杭州:浙江大學,2007.

[2]竇勇,鄔貴明,等.支持循環自動流水線的粗粒度可重構陣列體系結構[J].中國科學,2008,38(4):579 -591.

[3]鄔貴明,竇勇,等.面向數據驅動處理器陣列的自動綜合[J].計算機工程與科學,2009,31(S1):42-45.

[4]楊君,專用指令集處理器(ASIP)體系結構設計研究[D].合肥:中國科技大學,2006.

[5]KEUTZER K,MALIK,S,NEWTON A R.From ASIC to ASIP:the next design discontinuity[C].Proceedings of the 2002 IEEE International Conference on Computer Design:VLSI in Computers and Processors,2002.84 -90.

[6]SHEN J P,LIPASTI M H.現代處理器設計技術[M].北京:電子工業出版社,2004.24-61.

[7]WEINHARDT M,LUK W.Pipeline vectorization[J].IEEE Transactions on computer-aided design of integrated circuits and systems,2001,20(2):234 -248.

[8]KAHN G.The semantics of a simple language for parallel programming[C].Proceedings of the IFIP Congress,North-Holland,1974.471-475.

[9]施東材.基于對等網絡的語義發布/訂閱系統的關鍵技術研究[D].杭州:浙江大學,2007.

[10]田耘,徐文波.Xilinx FPGA開發實用教程[M].北京:清華大學出版社,2008.3-105.

Design and realize for ASIP based on reconfigurable computing

SONG Huan-huan,WANG Shu-zong,SHAO Li-bing

(Department of Weapon Engineering,Naval University of Engineering,Wuhan,430033,China)

In order to accelerate algorithm of computation-intensive and data-intensive,virtual instructions designed by Kahn thread and pipeline processor for embedded coarse-grained reconfigurable array are introduced.Instruction-level parallelism is extended to contain thread-level parallelism by design of instruction pipeline.Communication of reconfigurable array adopts subscribe/published mechanism.Finally,the simulation result validates the architecture of pipeline processor.

reconfigurable computing;ASIP;cycle pipline;subscribe/published mechanism

TP314

A

1672-7649(2012)05-0078-05

10.3404/j.issn.1672-7649.2012.05.018

2011-08-08;

2011-09-06

國防973項目資助(613660202);中國博士后科學基金資助項目(200902668)

宋奐寰(1983-),女,博士研究生,從事可重構技術與故障處理研究。