基于PCIE的數字信號處理板設計與實現

聶彬彬,解 放

(中國電子科技集團公司第四十七研究所,沈陽110032)

1 引言

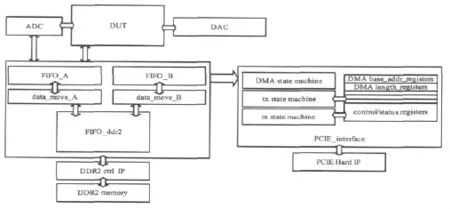

為滿足科研項目需求,本文設計了一種可應用于數字上/下變頻、FFT等數字信號處理算法評估驗證的通用數字信號處理卡,該板卡可將處理后的數據在計算機上顯示和分析處理。該板卡主要由模擬數據輸入/輸出模塊,數據存取模塊、數字信號處理模塊和數據通訊模塊構成。模擬數據輸入/輸出模塊主要由模數轉換芯片和數模轉換芯片構成。該板卡的數字邏輯部分全部在ALTERA公司生產的Arria GX2系列的EP2AG125EF29芯片內部實現,其中數據存取模塊由FPGA內部的RAM資源和外接DDR2存儲器共同組成,數據通訊模塊利用FPGA器件內部提供的hard IP實現本設計所需的PICE接口,并利用WinDriver軟件完成PCIE驅動的設計和API封裝。本文介紹的板卡內部功能框圖如圖1所示。

圖1 通用數字信號處理板卡功能框圖

2 模擬數據輸入/輸出模塊

(1)模數轉換芯片使用精度為14位、采樣率65MSPS的AD9244,可滿足較高的模數轉換精度和速度需求。AD9244無需配置,輸出數據格式為14位并行數據,便于與FPGA的接口連接,本設計配置2塊 AD9244。

(2)數模轉換芯片采用精度為16位、采樣率為1Gsps的AD9779A。AD9779A為雙通道DAC,采用SPI串行總線接口進行配置。由于本文側重點為通用數字信號處理卡的設計,故對AD9779A的內部寄存器具體內容不作介紹。使用AD9779A需要注意2組16位并行數據輸入由FPGA驅動,兩組16位數據在布線時要按數據總線處理,盡量確保等長。而AD9779A輸出的DATACLK可以作為數據參考時鐘接入FPGA的時鐘輸入管腳。FPGA輸出并行數據添加TCO約束后,可以保證并行數據的每一位均幾乎同時到達DAC的輸入。設置AD9779A內部寄存器以使DATACLK是否反相,未反相或反相的DATACLK中必有一種配置可以使并行數據滿足于DATACLK的建立與保持時序關系。這樣可以簡化當FPGA輸出的數據率為100MSPS或更高時的時序設計。

AD9779A的數據經過濾波等環節后可以作為AD9244的輸入,為本數字信號處理卡提供信號源。

3 數字信號處理模塊

本板卡的設計目的是用于評估數字信號處理算法,故本文不介紹具體數字信號處理模塊的實現。Altera公司的Arria GX2 125芯片內部的邏輯資源可用于實現不同的算法。

4 數據存取模塊

在評估數字信號處理算法時需要分析數字信號處理前/后以及處理過程中各節點輸出的數據,由于FPGA內部RAM空間有限,故本設計采用內部RAM與外擴DDR2內存相結合的方式來完成大容量數據的緩存。為了便于用戶使用DDR2內存,本設計將DDR2實現的大容量FIFO_ddr2與由內部RAM實現的FIFO_A和FIFO_B進一步封裝為一個模塊pseudo_fifo。用戶進行FIFO寫操作時,數據寫入FIFO_A中,用戶進行FIFO讀操作時,數據從FIFO_B中讀出,pseudo_fifo內實現由FIFO_A向FIFO_ddr2的數據搬移邏輯A和由FIFO_ddr2向FIFO_B的數據搬移邏輯B。在DDR2實現大容量FIFO時使用了DDR2內存控制器IP,在FIFO_ddr2內部利用格雷碼計數器來生成讀/寫地址,根據讀/寫地址的關系來生成FIFO_ddr2的空/滿以及近空/近滿等標志。數據搬移邏輯A完成寫地址遞增操作,數據搬移邏輯B完成讀地址遞增操作。數據搬移邏輯A對FIFO_A的讀操作和FIFO_ddr2的寫操作、數據搬移邏輯B對FIFO_ddr2的讀操作和FIFO_B的寫操作,工作在高速時鐘200MHz。這樣的設計使用戶僅需按照FIFO的寫時序,就可將待觀測的各個信號加入數據存取模塊進行緩存,而數據通訊模塊也僅需按照FIFO的讀時序將緩存中的數據讀入,簡化了數據通訊模塊的設計。

本設計采用容量為2GB的內存,該內存數據位寬為64位,配置內存控制器時使用half rate模式,則FIFO_ddr2的內部數據寬度為256位(64位X4)。則FIFO_A和FIFO_B的數據寬度也設為256位。這樣可同時對256路數字量進行采集,采集深度約為64M,由此可知,該板卡具有普通邏輯分析儀無法比擬的數據處理能力。

5 數據通訊模塊

PCIE插槽正逐漸取代計算機主板上的PCI插槽,故本設計采用了PCIE協議作為與計算機間的通訊協議。文中數據通訊模塊的設計包括固件和軟件兩個方面。

5.1 固件設計

Arria GX2器件支持PCIE的hard ip實現,對比soft IP實現節省了FPGA的內部資源。為了使PCIE的ip core能與數據存取模塊進行通訊,本設計在數據通訊模塊內部實現PCIE_interface邏輯。軟件可發出讀/寫寄存器的命令到本板卡上,PCIE_interface邏輯負責對命令進行解釋和執行。本板卡上實現了如下寄存器用于控制和觀測板卡的工作:

(1)兩個寄存器用于控制板卡數據采集的開始和結束;

(2)兩片AD9244采集的數字信號在數字信號處理模塊進行正交變換時會產生兩組同相(I)/正交(Q)分量共四組數據,每組256個共4組FIR系數寄存器用于加載板卡上數字濾波器的系數;

(3)抽取率寄存器可用于設置抽取率;

(4)組DMA基址寄存器、傳輸字節數寄存器用于設置4組DMA通道,以完成4組數據的上傳;

(5)一組狀態寄存器用于表示板卡各子模塊的工作狀態,如FIFO的空/滿、近空/近滿、FIFO寫入/讀出數據個數。

(6)一組寄存器組用于設計數控振蕩器(NCO)的頻率控制字等。

對于寄存器讀寫操作實現較為簡單,即將來自計算機的MWr數據包中的地址進行譯碼并取出數據包中的數據完成寄存器寫操作,將MRd數據包中的地址進行譯碼并以CPld數據包返回查詢的寄存器內容。

為了將數據存取模塊中的海量數據上傳至計算機,不能采用軟件查詢操作方式,而需使用中斷方式。即通過由本板卡發起的DMA操作,將數據存取模塊中的數據以MWr數據包的方式寫入計算機內存空間。定義如下狀態完成DMA操作:

DMA_IDLE:總線空閑

DMA_REQUEST:板卡請求DMA傳輸

DMA_ACK:允許本次DMA傳輸

TX_LENGTH:確定本次傳輸的數據長度

MWR_REQ:MWr數據包desc準備

MWR_DV:MWr數據包數據傳輸

MWR_DONE:本次DMA傳輸結束

DMA_INTERRUPT:所有DMA操作完成產生中斷

DMA_WAIT_INTERRUPT_ACK等待計算機軟件處理中斷

5.2 軟件設計

利用WinDriver軟件可以簡化驅動程序的開發,該公司網站有試用版可供使用。該軟件可自動生成驅動程序框架,提供可以訪問板卡硬件資源的API,用戶只需調用API對板卡固件中實現的寄存器進行讀/寫,即可完成板卡配置和查看板卡狀態。基本的寄存器讀寫較為簡單不做介紹,下面簡單介紹如何由軟件來初始化和完成一次DMA傳輸。

(1)通過讀取板卡狀態寄存器組中的FIFO寫入數據個數寄存器,來獲得本次DMA一共需要傳輸的數據字節數。

(2)在計算機內存中分配存儲空間供本次DMA使用。

(3)將分配的內存起始地址和待傳輸字節數寫入板卡相應的寄存器。

(4)板卡根據DMA基址寄存器和DMA傳輸的字節數寄存器的內容來使固件中的DMA狀態機開始工作。

(5)當所有數據上傳完畢后,板卡發起中斷。

(6)軟件在中斷處理函數中清除板卡中斷,準備開始下一次DMA數據傳輸。

6 結束語

此板卡可進行數字濾波器、上/下變頻、FFT等算法的硬件仿真測試,通過外接存儲器的方法增加了板卡的數據存儲能力,并通過PCIE協議將采集到的數據轉儲到計算機內存,在計算機上可通過對比MatLab等軟件仿真的結果與板卡的數據處理結果來分析數字信號處理算法的有效性。還可以靈活的修改軟件和固件使其能夠滿足科研項目對通用數字信號處理實驗平臺的需求。

[1] Altera International Limited.Arria II Device Handbook[J/OL].http://www.altera.com.

[2] Altera International Limited.IP Compiler for PCI Express User Guide[J/OL].http://www.altera.com.

[3] Jungo Ltd.WinDriver.PCI/PCMCIA/ISA Low-Level API Reference[J/OL].http://www.Jungo.com.