專用集成電路靜態(tài)時序分析

唐 拓,張 偉

(中國電子科技集團(tuán)公司第四十七研究所,沈陽110032)

1 引言

為了使電路性能達(dá)到設(shè)計預(yù)期目標(biāo),并滿足電路工作環(huán)境要求,必須對一個電路設(shè)計進(jìn)行諸如時序、面積、負(fù)載等方面的約束,并自始至終使用這些約束條件使電路設(shè)計軟件按照設(shè)計意圖來運(yùn)行。設(shè)計約束一般包括專用集成電路(ASIC)生產(chǎn)廠家的設(shè)計規(guī)則約束和設(shè)計者自定義的設(shè)計優(yōu)化約束。設(shè)計規(guī)則約束優(yōu)先權(quán)高于設(shè)計優(yōu)化約束,是隱含的,無須設(shè)計者指定,因此,這里重點討論設(shè)計優(yōu)化約束。設(shè)計優(yōu)化約束包括設(shè)計者對電路性能上的一系列在時序、面積和版圖布通性等方面的指標(biāo),其中最重要、最復(fù)雜的是時序約束。

2 設(shè)計的時序約束

2.1 單時鐘同步電路的時序約束

要對一個電路的時序行為進(jìn)行充分約束,至少應(yīng)考慮時鐘網(wǎng)絡(luò)、端口輸入輸出延遲以及端口的驅(qū)動和負(fù)載特性。

2.1.1 時鐘網(wǎng)絡(luò)

對于一個實際的時鐘網(wǎng)絡(luò),最重要的兩個屬性就是時鐘的傳播延時和時鐘的不確定性。時鐘的傳播延時包括時鐘源延時和時鐘網(wǎng)絡(luò)延時。在版圖設(shè)計完成之后,時鐘樹上電路單元和網(wǎng)絡(luò)延時等參數(shù)可以反標(biāo)回來,通過適當(dāng)設(shè)置,讓這些延時信息在時鐘網(wǎng)絡(luò)上傳播,這樣可以自動獲得時鐘的這些重要屬性。

當(dāng)時鐘網(wǎng)絡(luò)上包含除緩沖器和反相器之外的邏輯時,就會產(chǎn)生門控時鐘信號。通過約束使門控信號在相對時鐘沿的建立時間和保持時間區(qū)域內(nèi)保證不發(fā)生變化。

最小時鐘脈寬的檢查對時序電路非常重要,由于時鐘網(wǎng)絡(luò)上的門控單元和延時等的影響,脈寬在時鐘的傳播過程中會減小,可能在時鐘網(wǎng)絡(luò)的某些點上,時鐘不再往后傳遞。因此必須設(shè)定脈寬的最小限制。

2.1.2 端口延時

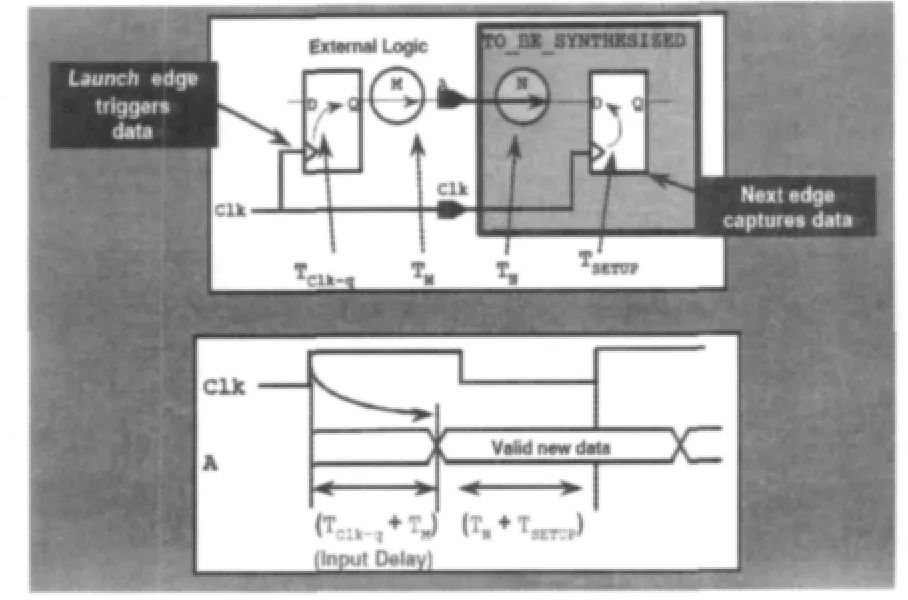

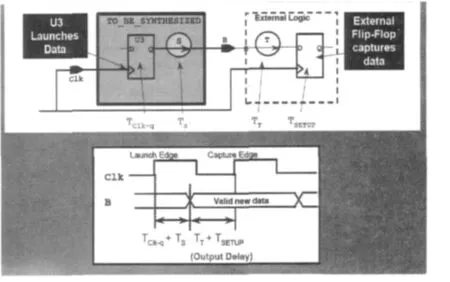

端口輸入延時是指外部路徑到電路輸入(或雙向端口)的相對于時鐘沿的時間。端口輸入延時應(yīng)該等于從源寄存器時鐘腳到驅(qū)動單元(輸入腳的直接驅(qū)動單元)輸出腳的延時減去驅(qū)動單元與負(fù)載相關(guān)的那部分延時。端口輸出延時是指輸出腳(或雙向端口)到外部寄存器的路徑延時,端口輸出延時的最大值等于從輸出腳到外部寄存器數(shù)據(jù)端的路徑延時的最大值加上寄存器的建立時間。端口輸出延時的最小值等于從輸出腳到外部寄存器數(shù)據(jù)端的路徑延時的最小值減去寄存器的保持時間。輸入(input delay)和輸出(output delay)延遲的圖解如下。

圖1 輸入延遲

圖2 輸出延遲

2.1.3 端口的驅(qū)動和負(fù)載特性

端口的驅(qū)動和負(fù)載特性描述了電路與外部環(huán)境的接口,將影響電路的時序行為。應(yīng)用環(huán)境轉(zhuǎn)變到約束如圖3所示。可以為不同的輸入端口從庫單元中選擇不同的驅(qū)動單元,為輸入、輸出端口指定負(fù)載值,同時還可以為輸出端口設(shè)定扇出負(fù)載的大小。在端口進(jìn)行時序約束時,應(yīng)考慮端口驅(qū)動和負(fù)載特性對時序的影響。

圖3 電路的驅(qū)動和負(fù)載信息

2.2 多時鐘同步電路的時序約束

多時鐘同步電路是指電路中的多個時鐘都由同一時鐘源派生而來,它們之間有相對固定的相位關(guān)系,其中有的時鐘不一定有實際對應(yīng)的電路端口。從總體上說,多時鐘同步電路可以采用與單時鐘同步電路同樣的約束策略,也包括定義時鐘(必要時需要建立虛擬時鐘作為端口輸入、輸入延時的參考)、指定I/O腳相對時鐘的延時等步驟。由于可能出現(xiàn)一個端口或網(wǎng)絡(luò)上存在多個約束的情況,時序分析工具總是選擇最苛刻的約束條件作為計算建立時間和保持時間的約束條件。對于特殊的電路結(jié)構(gòu),還可以通過設(shè)置多周期路徑和最大、最小延時等辦法,來滿足建立時間和保持時間的要求。

3 靜態(tài)時序分析

靜態(tài)時序分析技術(shù)是一種窮盡分析方法,用以衡量電路性能。它提取整個電路的所有時序路徑,通過計算信號沿在路徑上的延遲傳播,找出違背時序約束的錯誤,主要是檢查建立時間和保持時間是否滿足要求,而它們又分別通過對最大路徑延遲和最小路徑延遲的分析得到。靜態(tài)時序分析的方法不依賴于激勵,而且可以窮盡所有路徑,運(yùn)行速度很快,它完全克服了動態(tài)時序驗證的缺陷,適合進(jìn)行大規(guī)模及超大規(guī)模ASIC電路的驗證,可以節(jié)省多達(dá)20%的設(shè)計時間。靜態(tài)時序分析的問題在于:它不了解電路的動態(tài)行為,因而受到電路中眾多偽路徑的困擾;同時,目前靜態(tài)時序分析還只局限于同步電路的分析。因此設(shè)計結(jié)束之前要對全芯片進(jìn)行一次動態(tài)仿真。

4 設(shè)計實例及結(jié)果

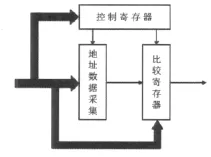

在一款硬件調(diào)試芯片設(shè)計中,采用靜態(tài)時序分析技術(shù)很好地分析了芯片的時序狀況。該芯片主要由地址/數(shù)據(jù)采集寄存器,控制寄存器以及比較器模塊構(gòu)成。分別完成對地址/數(shù)據(jù)的采集工作,在控制寄存器的控制作用下,與編程到比較器的數(shù)據(jù)進(jìn)行比較,從而完成對程序執(zhí)行的實時監(jiān)控。其結(jié)構(gòu)框圖如圖4所示。

該芯片的時鐘頻率有12M,分別完成芯片內(nèi)部同步邏輯的控制工作。從整體上說,該款芯片屬于同步電路,因此,應(yīng)用靜態(tài)時序分析工具來對其進(jìn)行時序分析是一種很好的選擇。在分析的時候,存在的問題是復(fù)位信號經(jīng)過兩級同步電路同步后,由于同步寄存器之間幾乎沒有電路,因此出現(xiàn)了HOLD TIME的違背情況。這可以在后端布局布線的時候予以解決。

圖4 硬調(diào)試芯片總體框圖

在芯片版圖(layout)設(shè)計前,所有時鐘網(wǎng)絡(luò)必須設(shè)置 set-don’t-touch-network 和 set-ideal-net,以確保不影響后端版圖設(shè)計中時鐘樹的設(shè)計及版圖設(shè)計。待版圖設(shè)計完畢后,抽取出SDF文件和SPEF文件,然后在靜態(tài)時序分析工具中進(jìn)行反標(biāo)門級網(wǎng)表,進(jìn)行靜態(tài)時序分析。在版圖設(shè)計中,絕大多數(shù)(hold)錯誤,必須通過手工插入緩沖區(qū)解決。對于時鐘路徑的處理,對最小時鐘脈寬分析,通過set-min-pulsewidth分析;對setup timing和hold timing的分析,通過report_timing命令來分析,還可以用report_constraint–all_violators命令來檢查所有時序上的違背情況。

5 結(jié)束語

采用UMC公司0.35微米CMOS標(biāo)準(zhǔn)單元庫(Faraday FS8000A 0.35微米library),邏輯綜合工具為Synopsys Design Compiler,ATPG產(chǎn)生工具為Tetra-MAX靜態(tài)時序分析工具采用Prime Time。通過對全芯片進(jìn)行靜態(tài)時序分析,芯片的時序狀況良好并為設(shè)計人員所把握,為后續(xù)環(huán)節(jié)的處理提供良好的依據(jù),為整個芯片的成功設(shè)計提供了堅實的基礎(chǔ)。

[1] Benkoski J,Vanden Meersch E,Claesen L J M,et al.Timing Verification Using Statically Sensitizable Paths[J].IEEE Trans on Computer2Aided Design of Integrated Circuits and Systems,1990,9(10):1073-1083.

[2] Prime time Workshop.Synopsys Customer Education Services[EB/OL].http://www.synopsys.com.

[3] 呂宗偉,林爭輝,張鐳.數(shù)字集成電路的時序分析[J].微電子學(xué),2001,31(2):126-129.