基于DSP的雷達干擾控制與處理系統(tǒng)

謝曉霞,傅其祥

(國防科技大學電子科學與工程學院,長沙410073)

1 引言

雷達電子戰(zhàn)是現(xiàn)代信息作戰(zhàn)中的重要部分,隨著數(shù)字信號處理(DSP)芯片技術(shù)的飛速發(fā)展,各種高速處理芯片已廣泛應用于各類電子對抗裝備中。美國TI公司推出的TMS320C6701是具有修正的哈佛總線結(jié)構(gòu)的32位浮點型通用DSP,基于此款DSP設(shè)計的雷達干擾系統(tǒng)控制與處理器是某干擾機的核心部分。它的功能是負責整個系統(tǒng)(包括射頻分系統(tǒng)、干擾信號模擬分系統(tǒng)、控制與信號處理分系統(tǒng)以及PC機)的控制、數(shù)據(jù)處理與監(jiān)控。

2 TMS320C6701簡介

在該DSP分系統(tǒng)設(shè)計中,采用美國TI公司的TMS320C6000系列32位浮點數(shù)字信號處理器TMS320C6701,其浮點運算速度可達1GFLOPS,已在眾多領(lǐng)域中得到了充分應用。它的主要特點有:

采用了修正的哈佛總線結(jié)構(gòu),內(nèi)部有一套256位的程序總線、兩套32位的數(shù)據(jù)總線和一套32位的DMA專用總線。這種靈活的總線結(jié)構(gòu)使得數(shù)據(jù)傳輸瓶頸對系統(tǒng)性能的限制大大緩解。

DSP核采用改進的甚長指令字(VLIW)體系結(jié)構(gòu)和多流水線技術(shù),具有8個可并行執(zhí)行的功能單元,。當芯片內(nèi)部8個處理單元同時運行時,其最大處理能力可以達到1336MIPs或1GFLOPS,大大提高了系統(tǒng)實時處理分析能力。

片上集成了大容量的高速程序存儲器和數(shù)據(jù)存儲器,最高可以200Mbit/s的速度訪問。程序存儲器為64K字節(jié)、256位寬,還可靈活設(shè)置為高速CACHE使用;數(shù)據(jù)存儲器采用雙存儲塊,每個存儲塊又采用多個存儲體,可靈活支持8/16/32位數(shù)據(jù)讀寫。片上集成了32位外部存儲器接口EMIF,可直接支持各種規(guī)格的 SDRAM、SBSRAM、SRAM、ROM、FLASH、FIFO 存儲器。

從以上特點可知,TMS320C6701具有高速的數(shù)據(jù)吞吐能力和極高的數(shù)據(jù)處理速度,還可以實現(xiàn)與外部存儲器的直接接口,這些特點都很好的保證了雷達干擾控制與處理分系統(tǒng)的實現(xiàn)。

3 控制與處理器設(shè)計

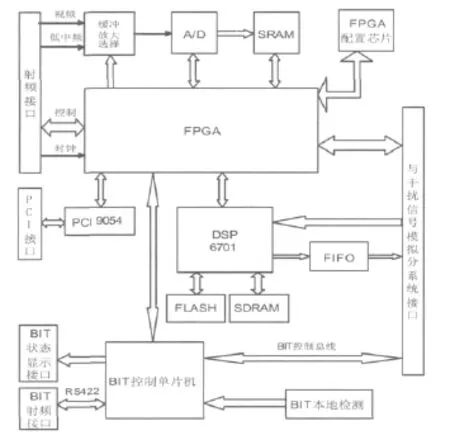

控制與處理器的功能是負責整個系統(tǒng)的控制、數(shù)據(jù)處理與監(jiān)控。它負責的控制功能包括射頻系統(tǒng)的控制(包括射頻系統(tǒng)的開關(guān)控制、增益控制、頻綜控制、射頻通道選擇)、干擾控制(包括干擾樣式、干擾時機等的控制);數(shù)據(jù)處理主要完成射頻系統(tǒng)中瞬時測頻接收機的測頻結(jié)果的實時處理和干擾信號模擬分系統(tǒng)采集到的高中頻信號(100MHz~500MHz)的1024點FFT(快速傅立葉變換)結(jié)果的譜分析(用來實現(xiàn)數(shù)字測頻)。為了解決單一測頻方式所帶來的測頻速度和測頻精度之間的矛盾,本干擾機系統(tǒng)采用了瞬時測頻與數(shù)字測頻相結(jié)合的雷達信號測頻技術(shù)。測頻結(jié)果的分析以及利用測得的頻率引導干擾則由控制與處理器的數(shù)據(jù)處理部分實現(xiàn)。監(jiān)控功能則包括整個系統(tǒng)的自檢以及視頻信號和低中頻信號(0~40MHz)的采集上傳。系統(tǒng)可分為五個模塊與三個接口:DSP模塊、FPGA模塊、BIT(自檢 )模塊、A/D模塊、PCI接口模塊;射頻接口、干擾信號模擬分系統(tǒng)接口以及PCI接口,其結(jié)構(gòu)框圖見圖1。

圖1 控制與處理分系統(tǒng)結(jié)構(gòu)框圖

下面分別就各模塊的設(shè)計思路進行介紹。

3.1 DSP模塊

DSP模塊是整個控制與處理器的核心模塊,要完成整個系統(tǒng)的控制以及大部分的數(shù)據(jù)處理和部分監(jiān)控功能。DSP模塊由DSP處理器、數(shù)據(jù)存儲空間以及程序存儲空間幾部分組成。

C6701片內(nèi)有64kBytes的數(shù)據(jù)存儲器和64kBytes的程序存儲器,但由于系統(tǒng)運行過程中要存放大量數(shù)據(jù),系統(tǒng)采用1片大容量的SDRAM映射到DSP的外部存儲空間以存放數(shù)據(jù)。程序存放在外部非易失存儲器(FLASH)中,在系統(tǒng)啟動后被調(diào)入片內(nèi)高速運行。

DSP模塊通過外部中斷來實現(xiàn)與其它模塊之間的功能交互。TMS320C6701共有4個外部中斷,除了一個用于DSP的復位,其它三個中斷分別用來響應來自主機的控制指令,來自干擾信號模擬分系統(tǒng)的取數(shù)據(jù)指令和響應外部視頻包絡(luò),用于干擾控制。

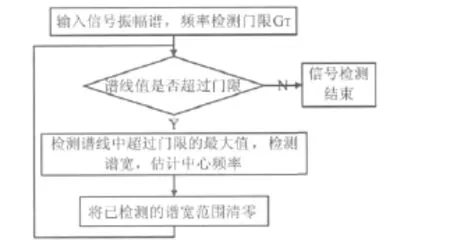

DSP模塊接收來自主機的控制指令,解讀后發(fā)指令給FPGA,經(jīng)過FPGA譯碼完成對其它各模塊的控制。DSP模塊將接收到的射頻部分的瞬時測頻結(jié)果進行統(tǒng)計分析,在上傳給主機的同時引導干擾系統(tǒng)對準目標頻段;來自干擾信號模擬分系統(tǒng)的高中頻信號的1024點FFT結(jié)果的譜分析也由DSP模塊完成,具體的處理流程見圖2所示。

圖2 FFT處理流程

DSP模塊完成的監(jiān)控功能主要是根據(jù)主機指令設(shè)置本地自檢芯片的門限電平。

3.2 A/D模塊

為了實現(xiàn)有效干擾必須對干擾機所面臨的輻射環(huán)境進行偵察。為此本系統(tǒng)設(shè)計了A/D模塊,用來采樣低中頻信號和視頻信號,將采樣數(shù)據(jù)送給主機進行雷達信號的分選與識別。低中頻信號的中心頻率為30MHz,帶寬為20MHz。利用100MHz A/D電路采集低中頻信號,通過采集這樣的中頻信號經(jīng)過分析處理得到信號帶寬、脈內(nèi)特征調(diào)制、信號時寬、重復頻率等一系列參數(shù);視頻信號則通過一個40MHz的A/D電路采集得到,通過分析處理可以得到脈沖寬度和脈沖到達時間等參數(shù)。通過獲得這些參數(shù)以及DSP模塊分析得到的測頻結(jié)果來實現(xiàn)對輻射源的有效識別,為干擾決策提供有利支持。

視頻信號與低中頻信號并不同時輸入,因此通過一個二選一的高速模擬選擇器選擇一路信號進來,信號通過緩沖器再送給A/D,A/D采集的數(shù)據(jù)存到SRAM里面,由DSP發(fā)出指令,在FPGA的控制下將采集得到的數(shù)據(jù)通過PCI接口上傳至主機。

3.3 FPGA模塊

FPGA模塊在控制與處理器中起到了橋梁的作用,它的主要功能是實現(xiàn)大量的邏輯控制電路,DSP的協(xié)處理和大量的接口電路。

FPGA模塊接收DSP傳送來的控制指令,對其譯碼后輸出A/D電路的控制信號(包括高速模擬選擇器的控制、A/D芯片控制與SRAM控制)、PCI接口芯片的工作模式選擇信號以及總線仲裁邏輯控制;DSP的總線連接以及BIT總線連接等也由FPGA完成。利用FPGA模塊C6701實現(xiàn)了對分系統(tǒng)中各電路模塊的控制,使各部分可以協(xié)調(diào)工作。

3.4 BIT模塊

BIT模塊即系統(tǒng)的自檢模塊,它的功能是以單片機為核心,采集系統(tǒng)的關(guān)鍵測試信號,包括各種電源電壓、溫度、關(guān)鍵信號電平、主要脈沖信號的頻率計數(shù)測量等,在先驗知識的前提下,自動判斷系統(tǒng)狀態(tài)信息,形成告警信號,為整個干擾系統(tǒng)的故障定位提供信息支撐。

射頻前端的BIT檢測結(jié)果通過422總線實時傳送給本系統(tǒng),干擾信號模擬分系統(tǒng)的BIT檢測結(jié)果通過數(shù)據(jù)與控制總線實時傳送,本地檢測則由片上芯片DS1780完成(它可同時監(jiān)測6個模擬量,包括4個電源電壓和2個溫度結(jié)果)。利用單片機(51單片機)實時將系統(tǒng)所采集到的各種工作狀態(tài)通過BIT總線送給主機用以顯示與決策,同時該信號也輸出到系統(tǒng)面板上,通過面板上的指示燈直觀的看到系統(tǒng)工作狀態(tài)正常與否。

3.5 PCI接口模塊

隨著ISA總線逐步被淘汰,基于PCI總線的接口設(shè)計越來越被廣泛地應用于各種高速、大數(shù)據(jù)量的處理系統(tǒng)中。本系統(tǒng)采用專用 PCI接口芯片PIC9054來完成PCI接口設(shè)計。它是PLX公司推出的一種32位33MHz的PCI總線主控I/O加速器。它采用多種先進技術(shù),使復雜的PCI接口應用設(shè)計變得相對簡單。在具體的電路設(shè)計中將PCI1054的所有地址線、數(shù)據(jù)線和控制線與 PFGA連接,由FPGA完成其工作模式選擇以及總線仲裁邏輯。數(shù)據(jù)傳輸采用的是突發(fā)方式下的DMA傳輸。PCI總線采用的是中斷共享機制,所有PCI擴展板在PCM插槽上共用一根信號線INTA#,通過電平觸發(fā)方式響應PCI中斷。

3.6 接口電路

系統(tǒng)包括三個接口電路:射頻接口、干擾信號模擬分系統(tǒng)接口以及PCI接口。

射頻接口主要是數(shù)字信號,考慮到傳輸電纜相對來說較長,容易受到干擾,因此采用422差分傳輸方式。干擾信號模擬分系統(tǒng)接口為了保證數(shù)據(jù)準確傳輸,在數(shù)據(jù)傳輸口增加一個雙向同步FIFO,F(xiàn)IFO起到緩沖的功能,提高效率與通信準確度。其內(nèi)部有兩個獨立的FIFO存儲器,兩個FIFO存儲器共用總線,這樣的設(shè)計使得兩個分系統(tǒng)之間的讀寫不發(fā)生沖突,不用總線仲裁機制,兩個分系統(tǒng)可以同時讀也可以同時寫,保證數(shù)據(jù)高效準確傳輸。另外與干擾信號模擬分系統(tǒng)的接口還需要一些控制信號,這些控制信號通過FPGA與DSP連接,受到DSP的控制。PCI接口用于實現(xiàn)控制與處理分系統(tǒng)與主機的連接。PCI總線采用的是中斷共享機制,主機的驅(qū)動程序利用中斷使能寄存器和中斷狀態(tài)寄存器對中斷類型進行識別,然后響應相應的中斷服務(wù)子程序。

4 系統(tǒng)應用

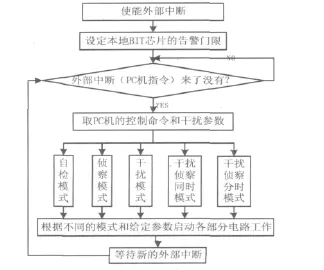

在整個系統(tǒng)工作時,控制與處理分系統(tǒng)接收來自主機的指令,完成對整個干擾系統(tǒng)的控制。DSP的工作流程如圖3所示。

由圖3,DSP工作后將所有外部中斷開啟,設(shè)定本地自檢芯片的門限,然后開始等待外部中斷(PC機指令)。操作員輸入指令后,給DSP發(fā)中斷,DSP響應外部中斷后,首先將控制指令和干擾參數(shù)讀出,然后根據(jù)讀出的指令和給定的參數(shù)啟動各部分電路工作。

圖3 DSP工作流程圖

5 結(jié)束語

基于DSP的控制與處理分系統(tǒng)是整個干擾系統(tǒng)的核心部分,可以實現(xiàn)整個系統(tǒng)干擾的控制與自檢監(jiān)控以及數(shù)據(jù)處理,是DSP處理技術(shù)的又一種有效應用。

[1] Texas Instrument Incorporated[Z].TMS320C6701 數(shù)據(jù)手冊.

[2] 曹瑞.一種基于DSP的雷達信號實時處理系統(tǒng)[J].微處理機,2001(4):38-40.

[3] 于鳳芹.TMS320 C6000 DSP結(jié)構(gòu)原理與硬件設(shè)計[M].北京:北京航空航天大學出版社,2008.