虛擬數字音頻掃頻儀的設計

周 濤 楊景常 郝明剛

(西華大學電氣信息學院,四川 成都 610039)

0 引言

在電子測量中,經常涉及到對網絡的阻抗特性和傳輸特性進行測量的問題,其中,傳輸特性包括增益特性、衰減特性、幅頻特性和相頻特性等。用于測量上述特性的儀器被稱為頻率特性測試儀,簡稱掃頻儀,它為被測網絡的調整、校準和故障的排除提供了極大的方便[1]。

傳統的、使用較多的儀器如BT-4型掃頻儀,大多是采用不同的電子元器件構成的振蕩器,這種儀器存在價格高、體積大、精度低等缺陷,不便于用戶實際使用。隨著電子技術的飛速發展,越來越多的電子電路要求集中在音頻范圍內工作,所以電路的音頻特性就顯得非常重要。

在此,本文提出了一種簡易的數字化掃頻儀的設計方法,能夠實現對待測網絡的音頻特性進行測試的功能。

1 掃頻信號產生原理

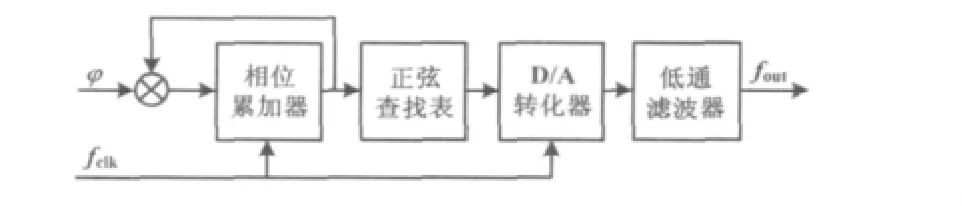

直接數字頻率合成(direct digital frequency synthesis,DDS)原理框圖如圖1所示。

圖1 DDS原理框圖Fig.1 Block diagram of DDS

DDS技術的工作原理介紹如下[2]。

相位累加器是由1個N位加法器和1個N位寄存器組成,其作用是對頻率控制字φ進行線性累加,正弦查找表中對應的是一張函數波形查尋表。對不同的相位碼址輸出不同的幅度編碼,相位累加器根據累加輸出的序列對查找表進行尋址,得到一系列離散的幅度編碼。該幅度編碼經D/A轉化器轉化后得到對應的階梯波,最后經低通濾波器平滑濾波后得到所需的模擬波形。相位累加器在基準時鐘fclk作用下進行線性相位累加,當相位累加器加滿時就會產生一次溢出。這就完成了DDS信號的一個頻率周期。

輸出信號的頻率為:

式中:fclk為參考時鐘頻率,Hz;φ為頻率控制字,rad;N為相位累加器的位數,bit。由式(1)可知,直接數字頻率合成(DDS)的頻率分辨率即最低頻率為:

所以,只要N足夠大,DDS就可得到很小的頻率間隔。要改變DDS的輸出信號的頻率,只要改變頻率控制字φ即可。

本設計根據上述DDS原理,利用DSP芯片通過軟件編程的方式來產生掃頻信號。軟件實現DDS的基本思路為:相位累加器由幾條語句來實現,正弦查找表采用DSP芯片內部ROM中固化的正弦表,數模轉換器的功能用脈寬可變的脈沖寬度調制波與低通濾波器來實現。其中掃頻信號產生的關鍵在于將所查到的正弦值映射成脈寬可變的脈沖寬度調制波。

2 幅頻特性測試原理

系統利用DSP內部的ADC模塊對EV模塊產生的單頻信號進行高速采樣,并通過比較求最大值的方法計算出待測網絡輸出端的單頻信號峰值。

本設計的幅頻特性測試編程思路為:用ePWM中斷子程序產生單頻掃頻信號,并通過置位標志位的方式通知主程序,主程序記錄當前待測網絡輸出端的頻率;然后啟動模數轉換器,并對當前待測網絡輸出端的信號進行高速采樣,獲得該頻率的幅值;最后將該頻率與幅值一起發送到PC機。

3 系統硬件設計

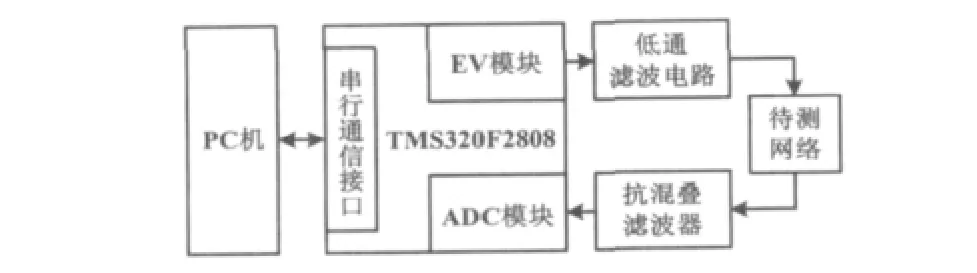

系統硬件主要包括PC機、串門通信接口模塊、EV模塊、ADC模塊、濾波電路、待測網絡等模塊,其整體框圖如圖2所示。

圖2 系統硬件框圖Fig.2 Block diagram of system hardware

3.1 DSP 最小系統

系統選擇DSP芯片TMS320F2808作為本設計的核心處理芯片。TMS320F2808含有豐富的片上外設資源,如 PIE、EV、ADC、串行通信接口(serial communication interface,SCI)、SPI等。本設計只涉及了其片上的EV、ADC和SCI等模塊。

最小系統由DSP芯片、復位電路、JTAG調試接口和時鐘電路組成[5]。復位電路采用容阻式的復位電路,其中RC回路充電時間常數為30 ms,能夠確保復位成功。JTAG調試接口可以方便程序的調試和燒寫。本設計的時鐘采用20 MHz無源晶振,經TMS320F2808內部的鎖相環倍頻后獲得100 MHz的CPU時鐘。

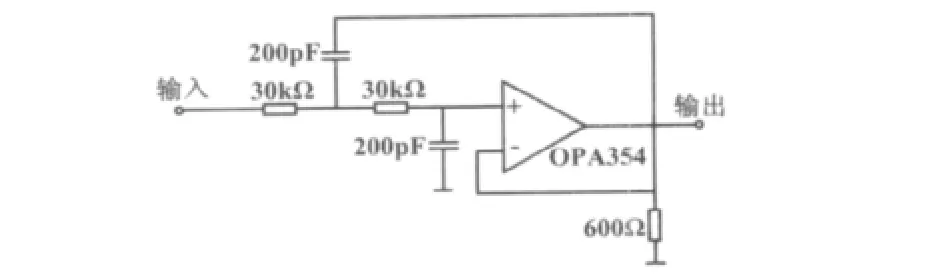

3.2 低通濾波電路

以OPA354運放芯片為核心芯片,設計了二階有源低通濾波器[6]。該濾波電路如圖3所示,其截止頻率為24 kHz,具有性能穩定、增益易調整、輸入阻抗高以及輸出阻抗低的特點。TMS320F2808輸出占空比可變的PWM信號,經該濾波電路處理后,輸出幅度為0~3 V的正弦信號,即掃頻信號。

圖3 低通濾波電路Fig.3 Circuitry of low-pass filter

3.3 抗混疊濾波電路

抗混疊濾波電路的結構亦采用上述低通濾波電路的設計方法。該電路的截止頻率是ADC采樣頻率的一半,可實現抗混疊的作用。待測網絡的輸出信號通過該電路進行抗混疊處理之后,輸入到TMS320F2808的ADCINA0引腳,由ADC進行高速采樣。

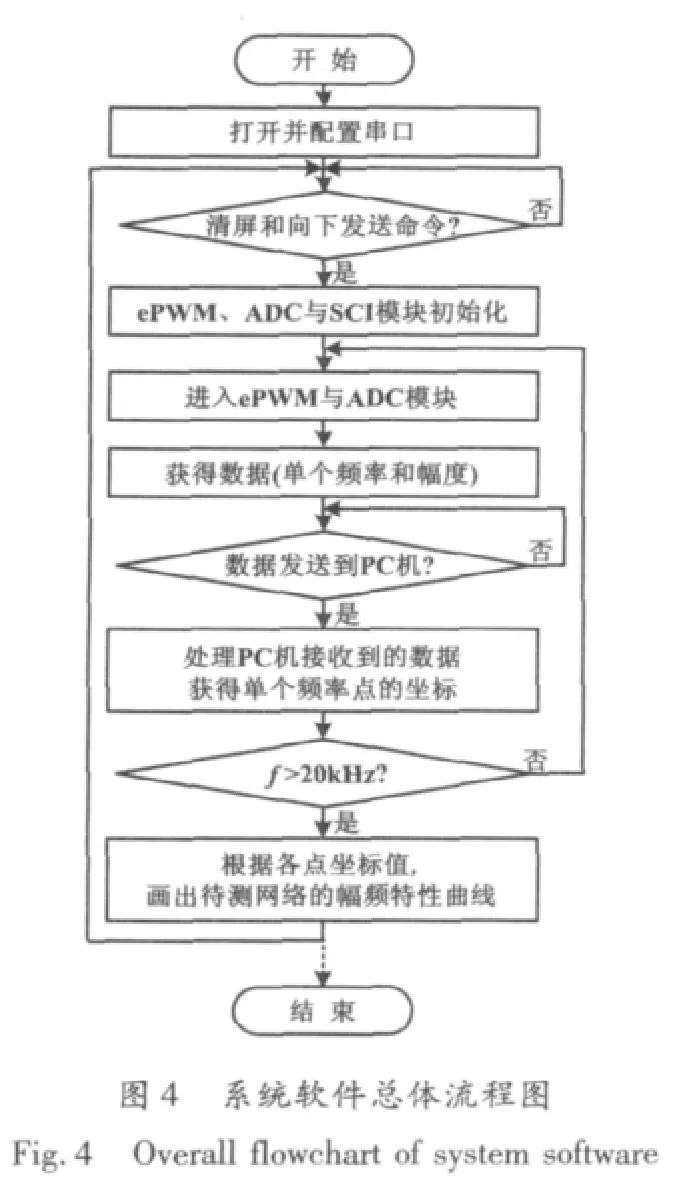

4 系統軟件設計

系統的軟件設計采用模塊化設計方案,即將實現特定功能的每個子程序組成一個功能模塊,最后由主程序統一調用。系統軟件包含的主要功能模塊包括初始化模塊、主程序控制模塊和中斷模塊。

4.1 初始化模塊

初始化模塊主要包括 PIE、PWM、ADC、SCI、GPIO模塊的初始化。

系統初始化將CPU時鐘通過TMS320F2808內部鎖相環倍頻后配置為100 MHz,禁止看門狗;并配置外設高速時鐘為系統時鐘的2分頻,外設低速時鐘為系統時鐘的4分頻,使能PWM、ADC、SCI時鐘。

PIE初始化首先將12組外設中斷寄存器和外設中斷標志寄存器清除,然后再初始化中斷向量表并使能PIE中斷。

GPIO初始化將所用的GPIO口根據系統的功能要求配置為相應的功能,其中GPIO28、GPIO29配置為SCI發送和接收,GPIO0配置為EPWM1A。

4.2 中斷模塊

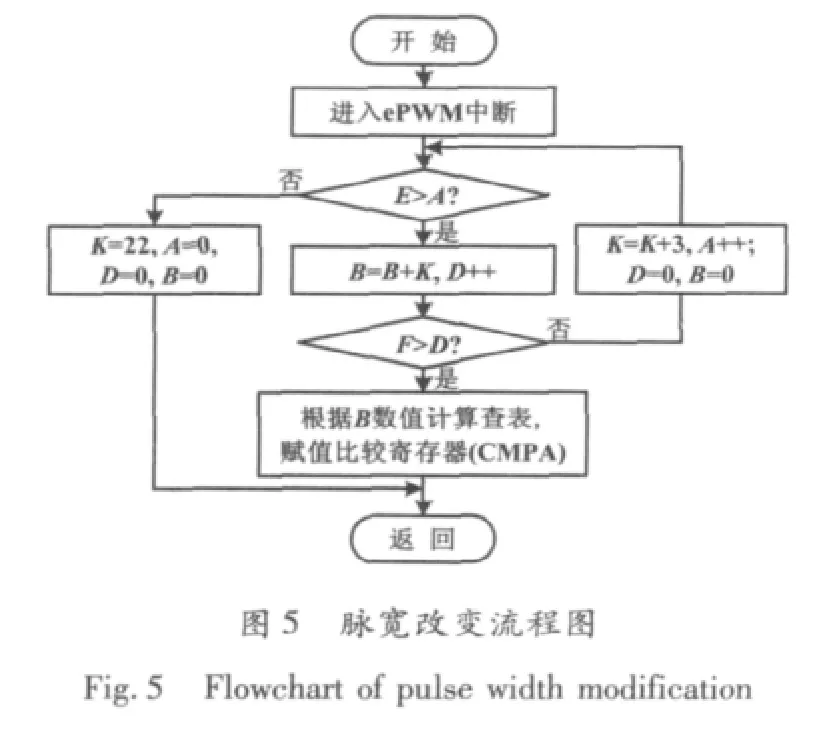

中斷模塊含有ePWM中斷、ADC中斷和 SCI中斷。ePWM中斷負責產生脈寬可變的PWM波,ADC中斷負責獲得單頻信號的幅值,SCI中斷負責發送單頻信號頻率與幅值到PC機和接收PC機下發來的命令。系統軟件總體流程圖如圖4所示。脈寬改變的具體程序流程如圖5所示。

圖5中:A為當前累計的頻率點數;B為相位累加器的值;K為頻率控制字;D為每種單頻信號的采樣點數;E為音頻范圍內總的頻率點數;F為各單頻信號的采樣點數,即為相位累加器的位數。

5 測試結果

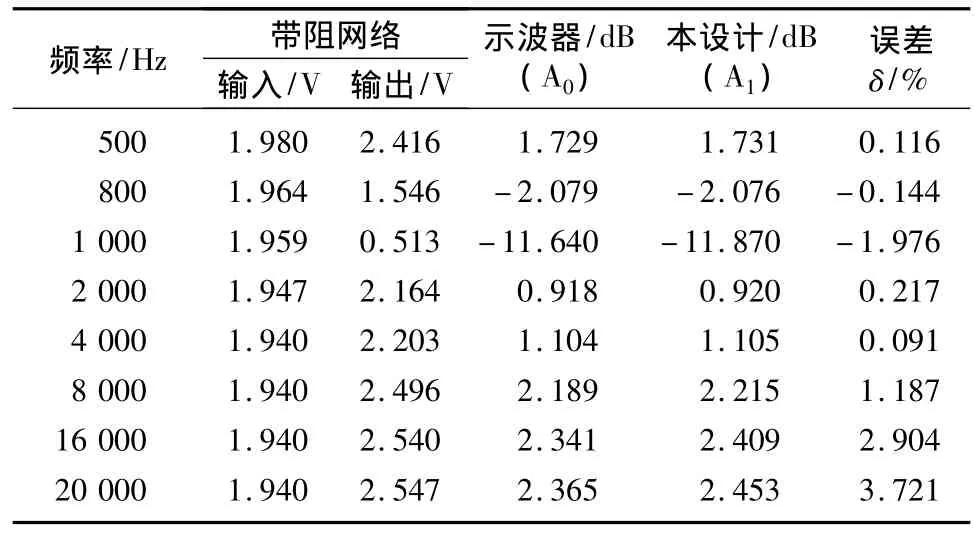

對系統的性能進行測試,本設計制作了1個雙T帶阻濾波器。本設計使用TDS1002示波器進行測試,示波器的頻率范圍為60 MHz,滿足本設計的測試要求。在選取的各頻率點處,首先用示波器測量該帶阻濾波器的輸入、輸出信號的幅度值;然后計算出掃頻信號通過該帶阻濾波器后在各頻率點處的幅度增益;最后將計算結果與PC機界面顯示的結果進行比較。帶阻濾波器的頻率特性測試結果如表1所示。由表1所示數據可知,本設計的測量誤差控制在4%以內,說明系統具有較高的測量精度,滿足系統要求。

表1 帶阻濾波器的頻率特性測試數據Tab.1 Test data of frequency characteristics of band-stop filter

6 結束語

本文設計的掃頻儀具有外圍電路少、系統參數軟件可調、運算速度快、精度高和結果數據可存儲等特點,測試誤差控制在4%以內,能夠直觀地測試被測網絡的音頻頻率特性,并繪制出相應的幅頻特性曲線。同時,它可以作為通用測試儀器,在電子產品開發中對音頻范圍內的被測網絡進行幅頻特性的測試,便于開發人員調整設計方案和設計參數。該設計的不足之處在于其沒有實現對待測網絡進行相頻特性測試的功能,這將是下一步開發的重點完善之處。

[1]毛長根.低頻掃頻儀的設計與制作[J].微電子與基礎產品,2002,28(3):37-40.

[2]毛敏,王淑仙,劉錦高.新型直接數字化合成式掃頻儀的原理和研制[J].儀器儀表學報,2004,25(4):534-537.

[3]操長茂.基于DDS的頻率特征測試儀[J].半導體技術,2003,28(12):44-46.

[4]陳小靜.基于 DDS技術的掃頻儀的設計[D].保定:河北大學,2010.

[5]孫麗明.TMS320F2812原理及C語言程序開發[M].北京:清華大學出版社,2008.

[6]康華光.電子技術基礎[M].5版.北京:高等教育出版社,2006:418-422.

[7]郝俊壽,李春明.基于DSP正弦信號源的實現[J].現代電子技術,2007,249(10):158-160.

[8]程佩青.數字信號處理教程[M].3版.北京:清華大學出版社,2007.

[9]譚浩強.C語言程序設計[M].3版.北京:清華大學出版社,2005.

[10]錢能.C++程序設計教程[M].北京:清華大學出版社,1999.