基于FPGA的多通道HB6096航空總線接口設(shè)計(jì)

劉 江

(中國(guó)西南電子技術(shù)研究所,成都 610036)

1 引 言

HB6096航空總線是我國(guó)在國(guó)外ARINC429航空總線基礎(chǔ)上發(fā)布的國(guó)內(nèi)航空電子設(shè)備總線傳輸協(xié)議,其數(shù)據(jù)傳輸方式及傳輸電平與ARINC429基本相同,是一種單向點(diǎn)對(duì)多廣播模式高速差分信號(hào)[1]。

國(guó)內(nèi)傳統(tǒng)HB6096總線接口設(shè)計(jì)主要依靠國(guó)外ARINC429專(zhuān)用集成電路實(shí)現(xiàn)。這些專(zhuān)用集成電路不僅面臨國(guó)外技術(shù)封鎖,還存在接口單一、集成度低的問(wèn)題。隨著我國(guó)航空工業(yè)的發(fā)展,越來(lái)越多的機(jī)載設(shè)備掛接在系統(tǒng)總線上,這時(shí)候傳統(tǒng)的HB6096接口設(shè)計(jì)方案已不能滿足小型化、高集成度及國(guó)產(chǎn)化設(shè)計(jì)需求。

為提高硬件集成度,本文立足于國(guó)產(chǎn)化設(shè)計(jì)思路,依據(jù)HB6096總線傳輸標(biāo)準(zhǔn),根據(jù)設(shè)計(jì)需求,基于FPGA實(shí)現(xiàn)了多通道HB6096航空總線接口設(shè)計(jì),并給出了總體設(shè)計(jì)方案、硬件、軟件詳細(xì)設(shè)計(jì)方法及測(cè)試結(jié)果。

2 HB6096總線簡(jiǎn)介

HB6096總線協(xié)議標(biāo)準(zhǔn)是我國(guó)航空工業(yè)部在1986年發(fā)布的SZ-01數(shù)字信息傳輸系統(tǒng)。協(xié)議要求每傳輸完成一個(gè)32位的數(shù)字字之后,以傳輸周期間至少5位的時(shí)間間隔為基準(zhǔn),緊跟該字間隔后要發(fā)送的第一位的起點(diǎn)即為新字的起點(diǎn)[2],而ARINC429則要求4位的時(shí)間間隔[3]。總線數(shù)據(jù)傳輸依靠?jī)筛罘中盘?hào)線完成,速率分為高速工作狀態(tài)(位速度100×103bit/s)及低速工作狀態(tài)(位速度12~14.5×103bit/s),并且要求高速率和低速率信息不在同一傳輸總線上傳輸。

HB6096總線調(diào)制方式采用雙極性歸零制的三態(tài)碼調(diào)制方式,即調(diào)制信號(hào)由“高”、“零”和“低”狀態(tài)組成的三電平狀態(tài)調(diào)制。A、B端總線電平狀態(tài)及轉(zhuǎn)換為T(mén)TL電平后對(duì)應(yīng)的邏輯狀態(tài)關(guān)系如圖1所示。

圖1 HB6096總線傳輸電平及數(shù)據(jù)轉(zhuǎn)換關(guān)系Fig.1 The voltage of HB6096 bus and data conversion

3 設(shè)計(jì)需求

要求總線接口模塊能接收、發(fā)送多路HB6096總線數(shù)據(jù),接口模塊通過(guò)設(shè)備內(nèi)并行總線實(shí)現(xiàn)通信。

(1)HB6096總線要求

1)8路HB6096總線接收接口;

2)5路HB6096總線輸出接口;

3)傳輸速率:100 kbit/s或12.5 kbit/s;

4)緩存要求:每個(gè)HB6096總線通道(接收或發(fā)送)緩存不小于1 024 byte。

(2)設(shè)備內(nèi)自定義總線接口

1)16位數(shù)據(jù)總線;

2)16位地址總線;

3)讀 、寫(xiě) 、片選 、中斷 、復(fù)位信號(hào) 。

4 總體設(shè)計(jì)

因HB6096傳輸電平與ARINC429基本相同,國(guó)內(nèi)傳統(tǒng)的HB6096多通道總線接口設(shè)計(jì)大多借用ARINC429設(shè)計(jì)方案,即采用處理器加進(jìn)口協(xié)議芯片,如文獻(xiàn)[4]采用CPLD和DSP相結(jié)合的方式,提出了一種2片DEI1016芯片并行工作的方案并實(shí)現(xiàn)。兩芯片共構(gòu)成2收4發(fā)6路429通道,采用中斷方式并行高速運(yùn)行;或如文獻(xiàn)[5]基于SOPC技術(shù),以NiosII軟核處理器為系統(tǒng)核心,并配合ARINC429通信協(xié)議芯片HS3282和HS3182實(shí)現(xiàn)對(duì)429總線數(shù)據(jù)的收發(fā)。

本設(shè)計(jì)方案立足國(guó)產(chǎn)化設(shè)計(jì),由FPGA完成HB6096協(xié)議解析,每個(gè)總線通道(接收或發(fā)送)緩存均由FPGA內(nèi)部RAM生成,每個(gè)通道設(shè)計(jì)一個(gè)狀態(tài)機(jī)進(jìn)行獨(dú)立管理,由控制內(nèi)核完成與設(shè)備內(nèi)并行總線的數(shù)據(jù)訪問(wèn),即基于FPGA實(shí)現(xiàn)多通道HB6096航空總線數(shù)據(jù)收發(fā)。

5 硬件設(shè)計(jì)

硬件主要由電源、時(shí)鐘、調(diào)試接口、FPGA、電平轉(zhuǎn)換電路、隔離驅(qū)動(dòng)電路等組成,硬件原理框圖如圖2所示。

圖2 硬件原理框圖Fig.2 Schematic block diagram of hardware

硬件核心FPGA采用ACTEL公司的A3P1000。設(shè)計(jì)要求8個(gè)接收通道,5個(gè)發(fā)送通道,每個(gè)通道緩存要求1 024 byte,一共需用(8+5)×1 024=104 kbit。A3P1000內(nèi)部 RAM 資源是144 kbit,滿足設(shè)計(jì)需求。

外圍方案是:隔離驅(qū)動(dòng)采用164245系列芯片完成TTL到LVTTL電平的轉(zhuǎn)換與隔離;接收通道的電平轉(zhuǎn)換芯片采用HOLT公司的HI-8588,發(fā)送通道的電平轉(zhuǎn)換芯片采用HOLT公司的HI-8585;系統(tǒng)時(shí)鐘50MHz;電源使用+5 V、+12 V、-12 V電壓滿足HB6096電平轉(zhuǎn)換芯片的使用。

6 軟件設(shè)計(jì)

6.1 設(shè)計(jì)方案

HB6096數(shù)據(jù)是32位串行數(shù)據(jù),設(shè)備內(nèi)部數(shù)據(jù)總線為16位并行數(shù)據(jù),需要將HB6096串行數(shù)據(jù)拆分為兩包16位的并行數(shù)據(jù)。接收通道采用16位寬度、512位深度的DPRAM,發(fā)送通道采用32位寬度、256位深度FIFO。每個(gè)接收通道分配一個(gè)DPRAM,每個(gè)發(fā)送通道分配一個(gè)FIFO緩存,各個(gè)通道相互獨(dú)立,由狀態(tài)機(jī)負(fù)責(zé)運(yùn)行工作。當(dāng)外部CPU需要對(duì)模塊進(jìn)行數(shù)據(jù)讀出、寫(xiě)入時(shí)由控制內(nèi)核完成相關(guān)地址映射、寄存器讀寫(xiě)工作。

整個(gè)軟件的功能結(jié)構(gòu)框圖如圖3所示。

圖3 軟件功能結(jié)構(gòu)框圖Fig.3 Block diagram of software configuration

軟件語(yǔ)言采用VHDL,編譯環(huán)境采用ACTEL公司產(chǎn)品適用的Libero9.1版本。

6.2 接收通道設(shè)計(jì)

6.2.1 32位串并轉(zhuǎn)換器

根據(jù)圖1所示雙極性歸零碼的特性,32位串并轉(zhuǎn)換器采用A與B異或作為數(shù)據(jù)采集的觸發(fā)信號(hào)。外部CPU根據(jù)系統(tǒng)實(shí)際使用情況,通過(guò)模塊間自定義總線配置速率寄存器,設(shè)置分頻器參數(shù),生成相應(yīng)10 MHz或1.25 MHz的采樣時(shí)鐘,以100倍的采樣速率對(duì)A端和B端的信號(hào)同時(shí)進(jìn)行采集。數(shù)據(jù)采集分為兩次校驗(yàn):單bit采集數(shù)據(jù)必須滿足A和B的異或關(guān)系,即A為邏輯“1”時(shí)B必須為邏輯“0”,B為邏輯“1”時(shí)A必須為邏輯“0”;32 bit數(shù)據(jù)采集完成后再進(jìn)行奇偶數(shù)據(jù)校驗(yàn),校驗(yàn)不通過(guò)的數(shù)據(jù)直接拋棄。兩次校驗(yàn)通過(guò)后按照相應(yīng)協(xié)議格式對(duì)32 bit的并行數(shù)據(jù)進(jìn)行轉(zhuǎn)換,轉(zhuǎn)換完成后將32 bit數(shù)據(jù)送入鎖存器,置相關(guān)標(biāo)志位,并做好下一包總線數(shù)據(jù)采集準(zhǔn)備。

6.2.2 DPRAM寫(xiě)狀態(tài)機(jī)

DPRAM寫(xiě)狀態(tài)機(jī)的流程如圖4所示。

圖4 DPRAM寫(xiě)狀態(tài)機(jī)流程圖Fig.4 The flow chart of state machine for writing DPRAM

圖4說(shuō)明如下:

STEP0:等待;

STEP1:置 CS、WR 有效,將低 16位數(shù)據(jù)送DPRAM,將虛擬地址+地址指針值送DPRAM;

STEP2:置 CS、WR 無(wú)效;

STEP3:置 CS、WR 有效,將高 16位數(shù)據(jù)送DPRAM,將虛擬地址+地址指針+1值送DPRAM;

STEP4:置 CS、WR 無(wú)效;

STEP5:地址指針累加。

在串并轉(zhuǎn)換成功標(biāo)位RX_SIGN置有效后,啟動(dòng)數(shù)據(jù)拆分及DPRAM寫(xiě)狀態(tài)機(jī)。將32位并行數(shù)據(jù)從鎖存讀出并拆分為 2包16位的并行數(shù)據(jù)。根據(jù)DPRAM的寫(xiě)數(shù)據(jù)時(shí)序,將虛擬的片選、寫(xiě)等控制信號(hào)置有效,然后按照先寫(xiě)低位,再寫(xiě)高位的方式,通過(guò)分配的虛擬地址,分兩次將一包HB6096數(shù)據(jù)寫(xiě)入DPRAM雙口。每寫(xiě)入一組16 bit的數(shù)據(jù)后,地址指針自動(dòng)加1,確保數(shù)據(jù)能夠進(jìn)行累進(jìn)存儲(chǔ),每寫(xiě)完一包HB6096數(shù)據(jù)地址指針實(shí)際累積加2。當(dāng)存儲(chǔ)到第512個(gè)數(shù)據(jù)(實(shí)際上是第256個(gè)HB6096數(shù)據(jù))時(shí),將地址指針自動(dòng)清零。第513個(gè)數(shù)據(jù)來(lái)后,將原來(lái)存儲(chǔ)的第1包數(shù)據(jù)進(jìn)行覆蓋存儲(chǔ)。

6.2.3 DPRAM存儲(chǔ)

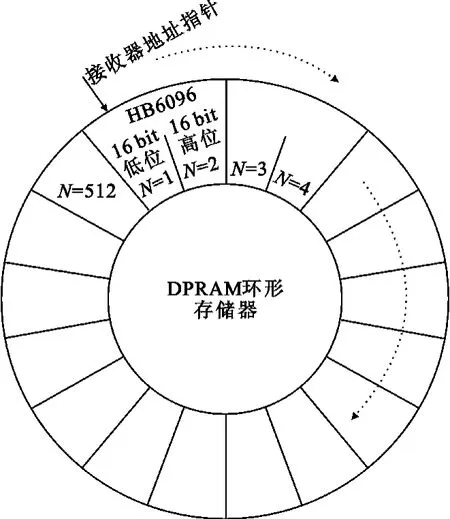

根據(jù)產(chǎn)品設(shè)計(jì)要求,結(jié)合FPGA的RAM資源,在數(shù)據(jù)量不大的情況下,我們采用DPRAM環(huán)形存儲(chǔ)的方式,即當(dāng)存儲(chǔ)BUFFER裝滿之后,重復(fù)寫(xiě)入該段存儲(chǔ)空間,覆蓋之前的數(shù)據(jù)。DPRAM環(huán)形存儲(chǔ)器結(jié)構(gòu)如圖5所示。

圖5 DPR AM環(huán)形存儲(chǔ)器結(jié)構(gòu)Fig.5 Architecture of circular DPRAM

圖5說(shuō)明如下:

(1)每個(gè)通道配置DPRAM環(huán)形存儲(chǔ)器1 kbyte,寬度為16位,深度512位;

(2)每一包HB6096數(shù)據(jù)先寫(xiě)16 bit低位,再寫(xiě)16 bit高位;

(3)每寫(xiě)入一包HB6096數(shù)據(jù),接收器地址指針自動(dòng)加2;

(4)當(dāng)存儲(chǔ)第256包HB6096數(shù)據(jù)后,地址指針清零;

(5)當(dāng)存儲(chǔ)第257包HB6096數(shù)據(jù)時(shí),該包數(shù)據(jù)將覆蓋之前接收到的第一包數(shù)據(jù)。

拋棄傳統(tǒng)外部掛接雙口芯片而在FPGA內(nèi)部開(kāi)辟DPRAM的優(yōu)點(diǎn)是:節(jié)約印制板空間,節(jié)約成本,抗干擾能力強(qiáng),存儲(chǔ)速度快,最重要的是可以實(shí)現(xiàn)多通道數(shù)據(jù)獨(dú)立并行處理。每個(gè)通道設(shè)計(jì)一個(gè)狀態(tài)機(jī)進(jìn)行獨(dú)立管理,將數(shù)據(jù)寫(xiě)入對(duì)應(yīng)通道的DPRAM,完全實(shí)現(xiàn)多通道的并行運(yùn)行。此種方案比外掛一個(gè)DPRAM芯片然后再依靠處理器或控制內(nèi)核去管理各個(gè)通道,依次逐個(gè)寫(xiě)入各個(gè)通道接收數(shù)據(jù)要合理有效得多,也避免了各通道滿負(fù)荷運(yùn)行時(shí)的數(shù)據(jù)堵塞。這也是本方案的創(chuàng)新之處。

6.3 控制內(nèi)核設(shè)計(jì)

控制內(nèi)核是整個(gè)總線接口模塊的數(shù)據(jù)傳輸、協(xié)調(diào)控制單元,整個(gè)控制內(nèi)核主要分為寄存器配置、總線接收地址指針讀取、總線數(shù)據(jù)接收讀取、總線數(shù)據(jù)發(fā)送寫(xiě)入。

控制內(nèi)核通過(guò)對(duì)各個(gè)接收通道、發(fā)送通道統(tǒng)一進(jìn)行地址編碼分配、接口映射,可實(shí)現(xiàn)與外部處理器進(jìn)行總線訪問(wèn)。上電后,外部處理器先配置各個(gè)接收、發(fā)送通道的HB6096總線傳輸速率。當(dāng)接收通道收到數(shù)據(jù)后,對(duì)應(yīng)接收通道地址指針轉(zhuǎn)動(dòng)。控制內(nèi)核可向CPU處理器發(fā)送中斷信號(hào),也可以由CPU處理器以主動(dòng)方式查詢各個(gè)接收通道的地址指針值。當(dāng)CPU發(fā)現(xiàn)接收地址指針偏移后,計(jì)算偏移量,得出接收到了多少包總線數(shù)據(jù),然后將該段數(shù)據(jù)讀出。當(dāng)需要發(fā)送數(shù)據(jù)時(shí),CPU通過(guò)控制內(nèi)核先查詢?cè)撏ǖ赖腇IFO存儲(chǔ)器是否已經(jīng)存滿。若可以繼續(xù)寫(xiě)入數(shù)據(jù),則通過(guò)控制內(nèi)核的發(fā)送通道地址映射,將發(fā)送數(shù)據(jù)寫(xiě)入對(duì)應(yīng)FIFO。

6.4 發(fā)送通道設(shè)計(jì)

由于發(fā)送數(shù)據(jù)是外部處理器為主動(dòng)模式,每一包HB6096數(shù)據(jù)均依照對(duì)應(yīng)發(fā)送通道進(jìn)行發(fā)送,因此只需要對(duì)每一個(gè)發(fā)送通道的地址進(jìn)行標(biāo)記。每次往該通道發(fā)送數(shù)據(jù),只需往該通道的地址寫(xiě)入數(shù)據(jù)就可以。因此,發(fā)送緩存采用基于PIPELINE管道結(jié)構(gòu)的FIFO緩存更合理。

6.4.1 寫(xiě)FIFO狀態(tài)機(jī)

根據(jù)設(shè)計(jì)要求,采用 32×256的 FIFO滿足1 kbyte要求。詳細(xì)設(shè)計(jì)如下:以發(fā)送1通道為例,設(shè)置TX1-ADDR地址為發(fā)送1通道的數(shù)據(jù)位低位,TX1-ADDR+1為數(shù)據(jù)位高位地址。CPU寫(xiě)入數(shù)據(jù)時(shí),先寫(xiě)入低16位數(shù)據(jù)到寄存器,再寫(xiě)入高16位數(shù)據(jù)送入寄存器,同時(shí)給出該通道數(shù)據(jù)已組合好的標(biāo)志位CPU-WR1。利用此標(biāo)志位,產(chǎn)生符合FIFO時(shí)序的寫(xiě)信號(hào),將32位HB6096數(shù)據(jù)一次寫(xiě)入FIFO。

其他發(fā)送通道類(lèi)似。

6.4.2 讀FIFO狀態(tài)機(jī)

讀FIFO狀態(tài)機(jī)采用FIFO緩存在存入數(shù)據(jù)后狀態(tài)標(biāo)志位的跳變信號(hào)作為啟動(dòng)信號(hào),再根據(jù)FIFO的讀時(shí)序,產(chǎn)生相應(yīng)的片選、讀信號(hào),將數(shù)據(jù)讀出。讀FIFO狀態(tài)機(jī)需要注意的是,狀態(tài)機(jī)在讀數(shù)前,需要先檢查32位并串轉(zhuǎn)換器的忙標(biāo)志位信號(hào)。如果并串轉(zhuǎn)換器處于忙狀態(tài),說(shuō)明上一包HB6096數(shù)據(jù)還沒(méi)有發(fā)送完成,需要等待;如果已經(jīng)轉(zhuǎn)換完成,證明上一包數(shù)據(jù)已發(fā)送,才可以讀取下一包數(shù)據(jù)。

6.4.3 32位并串轉(zhuǎn)換器

32位并行數(shù)據(jù)從FIFO中讀出來(lái)后,利用發(fā)送控制寄存器,將發(fā)送數(shù)據(jù)的傳輸速率以及發(fā)送數(shù)據(jù)的奇、偶校驗(yàn)方式信息傳遞給32位并串轉(zhuǎn)換器。轉(zhuǎn)換器根據(jù)寄存器配置信息選擇分頻時(shí)鐘及數(shù)據(jù)校驗(yàn)方式,然后對(duì)32位并口數(shù)據(jù)按照100 kHz或12.5 kHz時(shí)鐘,結(jié)合協(xié)議要求進(jìn)行格式轉(zhuǎn)換及編碼工作。編碼工作開(kāi)始后置忙標(biāo)志位,表明轉(zhuǎn)換器正處于發(fā)送工作狀態(tài),禁止再?gòu)腇IFO讀數(shù),防止數(shù)據(jù)丟失。直到32位數(shù)據(jù)已轉(zhuǎn)換完成,并按照HB6096總線要求設(shè)置5個(gè)比特位的時(shí)間間隔后,再將忙標(biāo)志位置為無(wú)效,啟動(dòng)讀FIFO狀態(tài)機(jī)讀出下一包數(shù)據(jù)。

7 測(cè)試驗(yàn)證

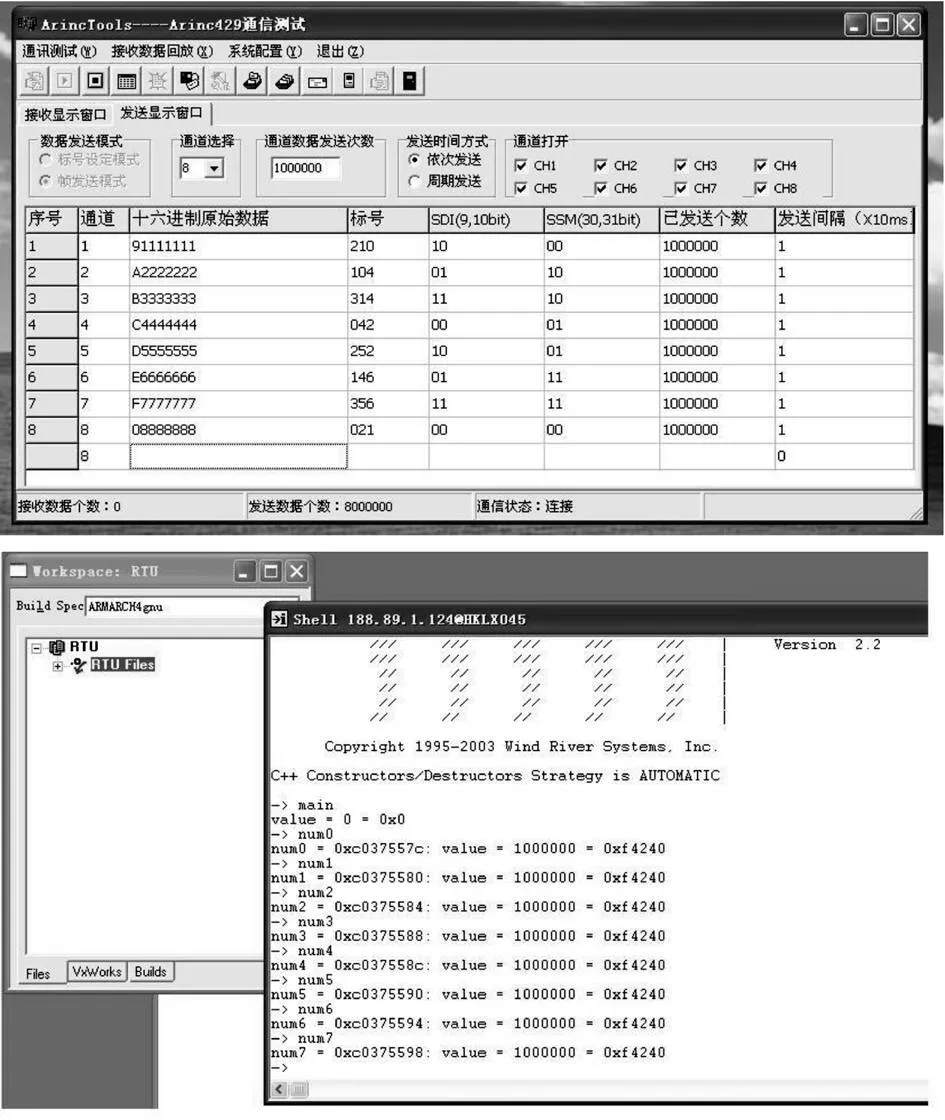

采用旋極公司Arinc429接口板及ArincTools通信測(cè)試軟件,結(jié)合CPU處理器TORNADO軟件,分別對(duì)本模塊的發(fā)送和接收通道進(jìn)行測(cè)試。

測(cè)試發(fā)送性能時(shí),ArincTools軟件處于接收狀態(tài),利用測(cè)試程序使5個(gè)發(fā)送通道全部打開(kāi),每個(gè)通道同時(shí)發(fā)送100萬(wàn)包HB6096數(shù)據(jù),通信速率100 kbit/s。檢測(cè)結(jié)果顯示本模塊所有發(fā)送通道均無(wú)數(shù)據(jù)錯(cuò)誤或丟失。發(fā)送通道測(cè)試結(jié)果如圖6所示。

圖6 發(fā)送通道測(cè)試結(jié)果Fig.6 The test result of sending channels

測(cè)試接收性能時(shí),ArincTools軟件處于發(fā)送狀態(tài),8個(gè)發(fā)送通道全部打開(kāi),每個(gè)通道同時(shí)發(fā)送100萬(wàn)包HB6096數(shù)據(jù),通信速率100 kbit/s。檢測(cè)結(jié)果顯示本模塊所有接收通道均無(wú)數(shù)據(jù)錯(cuò)誤或丟失。接收通道測(cè)試結(jié)果如圖7所示。

圖7 接收通道測(cè)試結(jié)果Fig.7 The test result of receiving channels

8 結(jié)束語(yǔ)

本文從工程應(yīng)用角度,基于FPGA設(shè)計(jì)了8路HB6096總線接收及5路HB6096總線輸出的總線接口,硬件資源開(kāi)銷(xiāo)小,系統(tǒng)滿足設(shè)計(jì)需求,軟件設(shè)計(jì)構(gòu)架合理。目前該設(shè)計(jì)已成功應(yīng)用于某機(jī)型HB6096航空總線接口模塊,經(jīng)模擬測(cè)試及高低溫等各項(xiàng)環(huán)境試驗(yàn)條件驗(yàn)證,模塊時(shí)序工作正常,穩(wěn)定可靠。

此設(shè)計(jì)方案摒棄了傳統(tǒng)HB6096總線數(shù)據(jù)處理依賴(lài)國(guó)外進(jìn)口ARINC429總線集成協(xié)議芯片辦法,實(shí)現(xiàn)了國(guó)產(chǎn)化設(shè)計(jì);摒棄了采用ARINC429集成芯片只能單、雙路收發(fā)的局限性,實(shí)現(xiàn)了多通道的數(shù)據(jù)收發(fā);每個(gè)通道配置獨(dú)立的緩存,實(shí)現(xiàn)了多通道的獨(dú)立并行運(yùn)轉(zhuǎn),節(jié)約資源,高效穩(wěn)定;采用CPU主動(dòng)查詢方式讀取接收數(shù)據(jù),保證了多路總線數(shù)據(jù)的穩(wěn)定接收,避免了可能出現(xiàn)的掉數(shù)問(wèn)題。該設(shè)計(jì)思路還可拓展應(yīng)用于國(guó)內(nèi)1553B等航空總線多通道接口國(guó)產(chǎn)化設(shè)計(jì)。

[1] 張楨,孫沛.基于FPGA的ARINC429總線通訊板設(shè)計(jì)[J].航空計(jì)算技術(shù),2010,40(4):112-115.ZHANG Zhen,SU N Pei.Design of Multi-channel ARINC 429 Communication Board Based on FPGA[J].Aeronautical Computing Technique,2010,40(4):112-115.(in Chinese)

[2] HB6096-86SZ-01,數(shù)字信息傳輸系統(tǒng)[S].HB6096-86SZ-01,Digital information transfer system for the standards of aeronautic industry department of the prc[S].(in Chinese)

[3] ARINC specification 429P3-19,mark 33 digital information transfer system(dits)-part 3-file data transfer techniques[S].

[4] 宋桂華,趙偉,劉建業(yè).多路ARINC429數(shù)據(jù)傳輸?shù)脑O(shè)計(jì)與實(shí)現(xiàn)[J].微處理機(jī),2009,30(3):116-118.SONG Gui-hua,ZHAO Wei,LIU Jian-ye.Design and Realization of Multi-channel ARINC 429 Data Transmission Technique[J].Microprocessors,2009,30(3):116-118.(in Chinese)

[5] 陳東,韓治中,梁勇.基于 SOPC的ARINC429總線接口設(shè)計(jì)[J].工業(yè)儀表與自動(dòng)化裝置,2010(1):30-33.CHEN Dong,HAN Zhi-zhong,LIANG Yong.The design of ARINC429 data bus interface based on SOPC[J].Industrial Instrumentation&Automation,2010(1):30-33.(in Chinese)