基于USB和FPGA的多功能等效器設(shè)計

蘇虎平,沈三民,劉文怡,葉 勇,張 昊

(中北大學(xué)電子測試技術(shù)國家重點實驗室,儀器科學(xué)與動態(tài)測試教育部重點實驗室,山西 太原 030051)

責任編輯:時 雯

等效器是一種自動測試系統(tǒng),是用以產(chǎn)生各種模擬、正弦、串行數(shù)字、時間指令脈沖等控制和測試信號,并進行事后數(shù)據(jù)分析和處理的自動測試平臺。等效器由計算機進行整體控制,由上位機下發(fā)命令到等效器的等效功能模塊產(chǎn)生所需要的各種測試信號,并將需要檢測的數(shù)據(jù)讀回來存儲、分析、處理,本文設(shè)計的等效器的多功能性體現(xiàn)在它不僅可以提供控制和測試信號給遙測設(shè)備的地面系統(tǒng)測試中,還可以對被測設(shè)備(遙測系統(tǒng))進行實時監(jiān)控、功能檢測和故障定位診斷等。

傳統(tǒng)的通信接口通常采用PCI總線或者是RS-232總線。PCI總線有較高的傳輸速率,可達132 Mbit/s,也可以即插即用,但是其擴展槽有限且插拔不方便;RS-232連接比較方便,但是傳輸速率太低。由于USB具有有傳輸速度快、占用資源少、真正的即插即用,且與PC產(chǎn)業(yè)的一致性和成本低廉等優(yōu)點,使其迅速在市場中流行。FT245RL是FTDI公司的快速USB通信接口解決方案之一,它無需編寫片內(nèi)固件程序,PC機使用FTDI公司提供的官方驅(qū)動程序D2XXDRIVER,F(xiàn)T245RL芯片的主要功能是在內(nèi)部硬件邏輯的作用下實現(xiàn)USB串行數(shù)據(jù)與并行數(shù)據(jù)的雙向轉(zhuǎn)換。因此,基于FT245RL的USB設(shè)備在測試系統(tǒng)中有很大的優(yōu)越性。本文上位機通過USB接口與FT245RL進行數(shù)據(jù)交換,F(xiàn)T245RL則通過并行方式與等效器主控 FPGA 通信[1-2]。

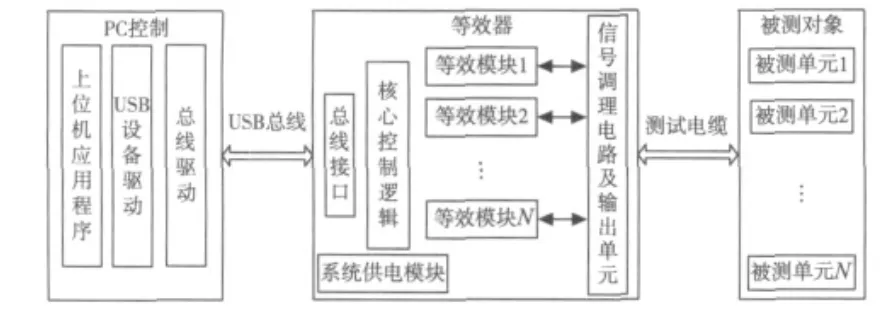

1 系統(tǒng)整體設(shè)計思路和結(jié)構(gòu)簡介

設(shè)計采用FT245RL和FPGA實現(xiàn)數(shù)據(jù)的通信,F(xiàn)PGA作為主控制器,F(xiàn)T245RL作為與PC機的USB通信接口。FPGA通過FT245RL接收上位機傳輸?shù)拿睢?shù)據(jù),然后根據(jù)上層通信協(xié)議判斷命令和數(shù)據(jù)類型,轉(zhuǎn)發(fā)上位機命令、數(shù)據(jù)到各功能模塊以實現(xiàn)不同的功能。為了匹配USB讀數(shù)速率和422異步串行通信發(fā)送數(shù)據(jù)速率的不同,采用FPGA內(nèi)部實現(xiàn)FIFO緩存通信數(shù)據(jù)。本設(shè)計盡量進行模塊化設(shè)計、彈性設(shè)計,可隨時對系統(tǒng)進行升級改進,擴大如圖1中所示的等效模塊,系統(tǒng)整體架構(gòu)見圖1。

2 硬件模塊設(shè)計

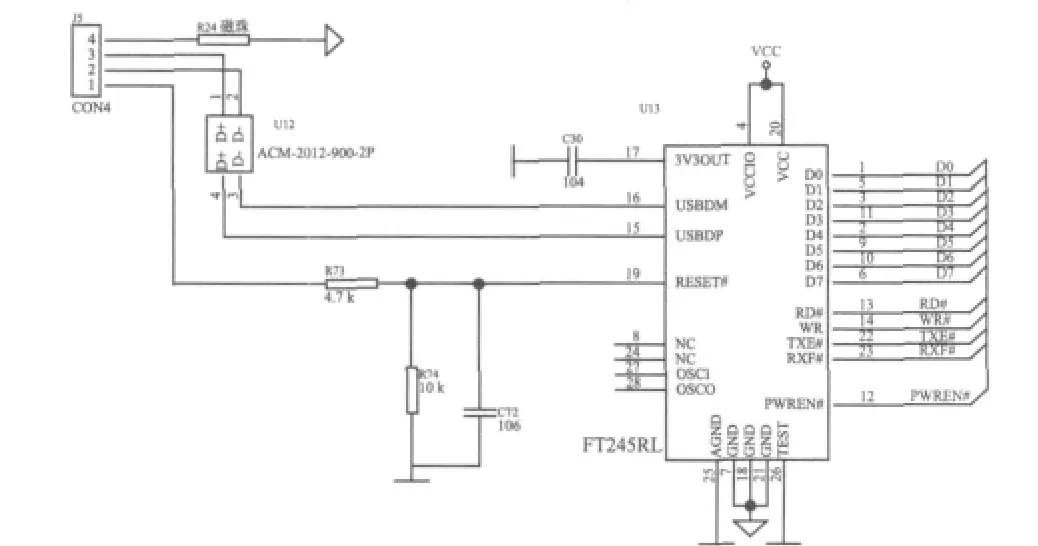

2.1 基于FT245的USB接口部分設(shè)計

圖2為FT245RL的USB接口電路。FT245RL 內(nèi)含兩個FIFO數(shù)據(jù)緩沖區(qū)。一個是128 byte的接收緩沖區(qū),另一個是384 byte的發(fā)送緩沖區(qū),它們用作USB數(shù)據(jù)與并行I/O口數(shù)據(jù)的交換緩沖區(qū)。FIFO主要是通過8根數(shù)據(jù)線DO~D7、讀寫控制線RD和WR、FIFO發(fā)送緩沖區(qū)空標志TXE和FIFO接收緩沖區(qū)非空標志RXF的配合來完成數(shù)據(jù)的交互。本設(shè)計采用自供電方式,上電復(fù)位,采用內(nèi)部晶振。圖中ACM-2012-900-2P共模電感和磁珠是為了減少主機和設(shè)備的干擾,PWREN管腳用于判斷USB總線是處于掛起狀態(tài)還是正常狀態(tài),D0~D7是8根數(shù)據(jù)線,、WR是FT245與FPGA相連的控制線。

圖1 等效器系統(tǒng)整體結(jié)構(gòu)圖

圖2 等效器系統(tǒng)USB接口電路

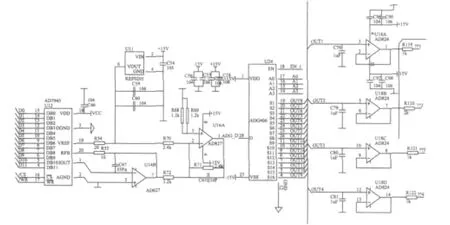

2.2 直流量部分設(shè)計

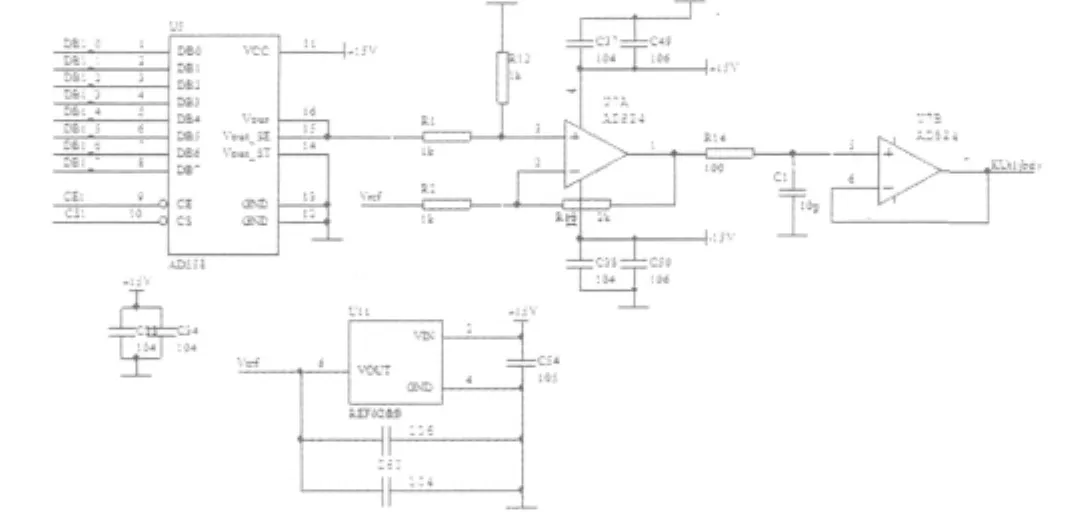

系統(tǒng)設(shè)計了16路模擬信號的輸出電路,對于不同電壓值可調(diào)的直流量信號,最好的選擇就是用D/A轉(zhuǎn)換電路產(chǎn)生小幅值電壓,然后運用信號調(diào)理電路產(chǎn)生所需要的電壓值。對于如此多路直流信號,如單獨實現(xiàn)每一路直流信號則會造成太大的浪費和成本的提高,因為各直流量信號的變化速度相對有限,因此本設(shè)計用模擬開關(guān)分時切換進行多路信號的輸出,這樣只需運用一片D/A轉(zhuǎn)換電路就可產(chǎn)生多路模擬直流信號。本設(shè)計由D/A轉(zhuǎn)換電路、運算調(diào)理電路、模擬電子開關(guān)、電壓保持電路組成。其具體電路如圖3所示。

DAC電路的設(shè)計需要考慮主要因素主要有轉(zhuǎn)換精度、轉(zhuǎn)換速度、電源要求等。此外溫度特性、數(shù)據(jù)耦合、焊接毛刺和非線性誤差的影響也不容忽視。本設(shè)計選用ADI公司的AD7945作為DAC芯片,它是12位乘法型并行輸入、單通道的電流輸出型低功耗數(shù)模轉(zhuǎn)換芯片,具有低溫漂、良好線性度的特性,采樣速率可達l.7 MSample/s,轉(zhuǎn)換時間最大值為760 ns,可直接與TTL或CMOS邏輯電平進行連接,本設(shè)計由REF0205輸出穩(wěn)定的5 V電壓來作為基準電壓,分辨力約為0.00122 V,精準度高。

圖3 D/A轉(zhuǎn)換電路

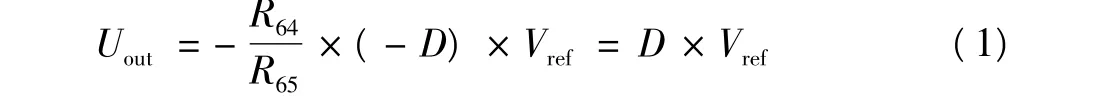

因為要輸出模擬電壓值,需將AD7945的輸出電流轉(zhuǎn)換為電壓。設(shè)計時輸出經(jīng)兩級反相運放轉(zhuǎn)換為需要的電流。前一級I/U轉(zhuǎn)換,后一級為利用反相比例放大電路設(shè)計的一階低通濾波器,輸入阻抗較小。由運算放大電路的運算公式可知

式中:Uout為AD7945轉(zhuǎn)換輸出并調(diào)理后的模擬量采樣幅值電準電壓;D為模擬電平的量化值。

如上文所述,任務(wù)要求產(chǎn)生多路模擬直流信號,因此本設(shè)計將D/A轉(zhuǎn)換電路調(diào)理輸出的電壓值經(jīng)過模擬開關(guān)分時輸出以“同時”產(chǎn)生多路直流信號。系統(tǒng)采用ADI公司的模擬開關(guān)ADG506,其具有16路模擬數(shù)據(jù)通道,電壓輸出范圍寬泛、功耗低,并且兼容CMOS/TTL電平標準,最大導(dǎo)通時間400 ns,開啟時間為50 ns,導(dǎo)通電阻一般為280~600Ω。因為要保證各通道獨立持續(xù)輸出模擬量,所以使用存儲芯片SRAM對各通道要轉(zhuǎn)換的數(shù)字量進行存儲。FPGA的進程觸發(fā)后,從SRAM中一次讀取數(shù)字量,并控制模擬開關(guān)切換到相應(yīng)的通道。模擬開關(guān)的A0~A3值與SRAM的地址線是同一數(shù)字線,這樣不同的SRAM存儲單元對應(yīng)不同的通道號。

2.3 正弦信號部分設(shè)計

AD558是電壓輸出型的D/A轉(zhuǎn)換器,輸出電壓范圍為0~10 V,再經(jīng)過由運算放大器構(gòu)成的差動減法電路,實現(xiàn)電壓范圍從0~10 V到-5~+5 V的轉(zhuǎn)換,這個差動減法電路還具有電壓放大的功能,將轉(zhuǎn)換的電壓放大兩倍,實現(xiàn)-5~+5 V到-10~+10 V范圍的電壓輸出;再經(jīng)過其后由RC和電壓跟隨器電路構(gòu)成的簡易有源低通濾波器,實現(xiàn)電壓平滑輸出,使用電壓跟隨器是因為其輸入阻抗很大,輸出阻抗很小,實現(xiàn)前后電路阻抗的匹配,電壓的完整輸出。首先上位機軟件將所需要產(chǎn)生的一定頻率、幅值的正弦波形量化,采樣256個點,計算出每個點的電壓;然后通過USB接口將量化數(shù)據(jù)傳送給主控FPGA,主控FPGA將這些數(shù)據(jù)寫入正弦波形存儲RAM;再由FPGA根據(jù)接收到的正弦波形的頻率等參數(shù)計算出正弦波形的周期以及每兩個點的時間間隔,將時鐘分頻到所需的周期,按照頻率參數(shù)讀取RAM中的數(shù)據(jù)送往D/A轉(zhuǎn)換電路輸出,從而產(chǎn)生所需正弦交流信號,圖4為正弦信號產(chǎn)生電路。

圖4 正弦信號產(chǎn)生電路

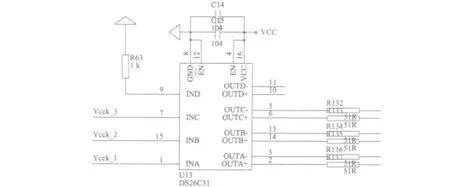

2.4 特定幀結(jié)構(gòu)的異步串行通信部分設(shè)計

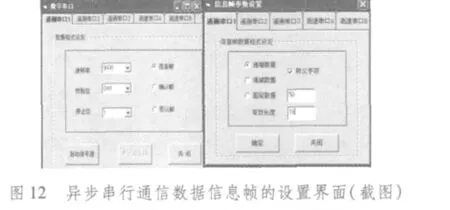

設(shè)計選用DS26C31作為RS-422發(fā)送控制器,用FPGA控制產(chǎn)生所要求幀結(jié)構(gòu)的異步串行數(shù)據(jù)。硬件電路如5圖所示,在發(fā)送端分別串聯(lián)50Ω的限流保護電阻,為了防止大電流對輸入端的影響。DS26C31的作用是將輸入端TTL/CMOS電平轉(zhuǎn)換為RS-422電平,具體的異步串行通信的數(shù)據(jù)發(fā)送波特率、時序和幀結(jié)構(gòu)等特性都由FPGA來實現(xiàn)。對于異步串行通信來說,數(shù)據(jù)的傳送涉及眾多的參數(shù):對于每一字節(jié)數(shù)據(jù)設(shè)計的參數(shù)有:波特率、數(shù)據(jù)位的數(shù)量、停止位的數(shù)量、奇偶校驗位等;對于數(shù)據(jù)幀來說涉及的參數(shù)有:幀類型、一幀數(shù)據(jù)的數(shù)量、幀數(shù)據(jù)的組織方式等。本設(shè)計按照任務(wù)要求的RS422異步串行通信數(shù)據(jù)幀格式為:波特率可變(可選擇為4800,9600,19200,38400,115200,1152000),數(shù)據(jù)字節(jié)校驗方式可變(可選擇為奇校驗、偶校驗),停止位數(shù)量可變(1位停止位或2位停止位);幀結(jié)構(gòu)類型可選擇(信息幀、確認幀、否認幀),信息幀組織形式可變(遞增數(shù)據(jù)、遞減數(shù)據(jù)、固定數(shù)據(jù)),信息幀數(shù)據(jù)數(shù)量可變,信息幀起始字節(jié)可設(shè)置等[3]。

圖5 RS-422電平轉(zhuǎn)換電路

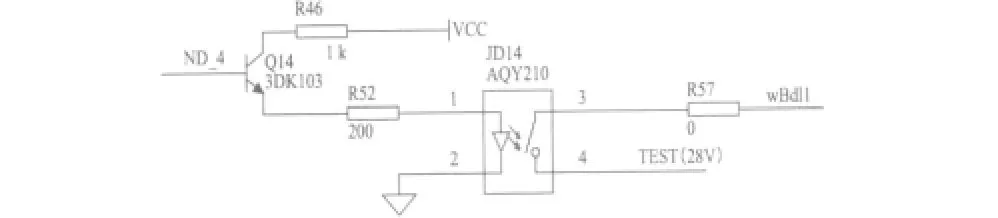

2.5 時間指令脈沖信號部分設(shè)計

本設(shè)計由FPGA控制光耦A(yù)QY210來實現(xiàn)所需的時間指令(包括帶點指令和不帶點指令)。帶電不帶電時間指令信號電路設(shè)計類似,只不過帶電指令信號的供電電壓由等效器提供;而不帶電指令信號的供電由測量系統(tǒng)來提供。AQY210具有噪聲低、速度快、體積小、壽命長、觸發(fā)電壓低等優(yōu)點,常用于信號的傳遞、電器隔離的場合。本設(shè)計采用此電路實現(xiàn)了時間指令信號。用FPGA管腳接到三極管3DK103的基極來控制三極管的通斷:當FPGA輸出“0”電平時,三極管工作在截止狀態(tài),發(fā)射極輸出低電壓低電流,這樣AQY210不導(dǎo)通,信號輸出端口工作在高阻態(tài);當FPGA輸出“1”電平時,三極管工作導(dǎo)通,發(fā)射極輸出高電壓高電流,驅(qū)動AQY210導(dǎo)通。時間指令信號的設(shè)計就是在上述開關(guān)電路的基礎(chǔ)上,F(xiàn)PGA收到上位機發(fā)來的命令后,判斷命令類型,確定通道號,之后啟動計數(shù)器來實現(xiàn)規(guī)定時間的開關(guān)電路的通斷來實現(xiàn)的,如圖6為時間指令脈沖硬件電路部分設(shè)計。

圖6 時間指令脈沖電路

3 等效器應(yīng)用層通信協(xié)議

等效器產(chǎn)生的信號類型和數(shù)量眾多,且這些信號模塊都必須受上位機的控制,為便于對這些信號控制模塊進行統(tǒng)一管理,本文設(shè)計了統(tǒng)一的等效器應(yīng)用層協(xié)議,此協(xié)議包括各類信號幀結(jié)構(gòu)的設(shè)計和協(xié)調(diào)一致的工作流程。

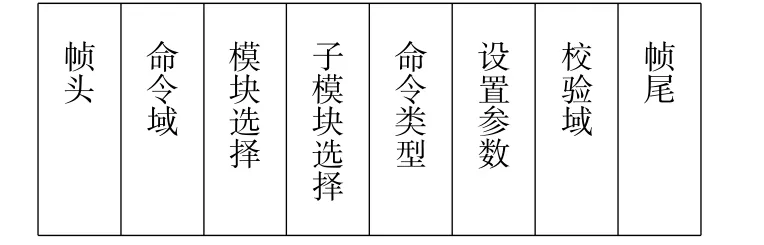

本設(shè)計中一幀有10 byte,其中幀頭2 byte,命令域、模塊選擇、子模塊選擇、命令類型、校驗域和幀尾各占1 byte,設(shè)置參數(shù)占2 byte。命令域包括包括自檢和握手命令、停止命令、各功能模塊接收信號命令;模塊選擇和子模塊選擇代表不同功能模塊的邏輯地址;設(shè)置參數(shù)包括直流信號、時間指令脈沖信號、422異步串行輸出信號、正弦信號、模擬信號清零復(fù)位信號;校驗域采用奇校驗,通過校驗域來保證命令和數(shù)據(jù)傳輸?shù)目煽啃裕?]。應(yīng)用層通信協(xié)議幀結(jié)構(gòu)的設(shè)計如圖7所示。

圖7 應(yīng)用層通信協(xié)議幀結(jié)構(gòu)

4 系統(tǒng)軟件設(shè)計

4.1 USB讀寫時序

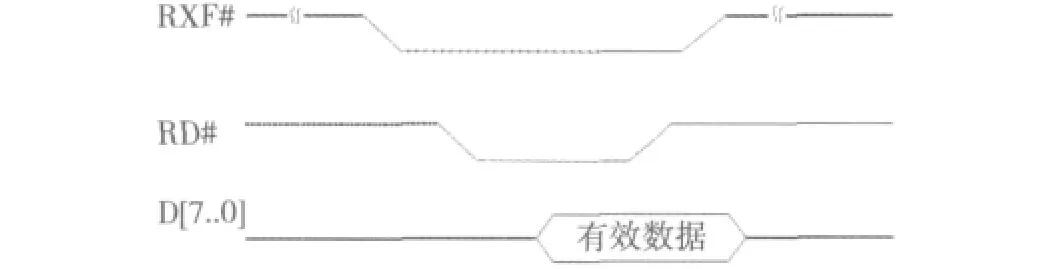

接收數(shù)據(jù)時序圖如圖8所示。接收數(shù)據(jù)的過程是外控制器(本設(shè)計為FPGA)不斷查詢FT245RL的RXF引腳狀態(tài),如果RXF引腳為高電平,說明芯片正處于接收數(shù)據(jù)狀態(tài);當RXF為低電平,則說明芯片已經(jīng)接收完成一字節(jié)數(shù)據(jù)并存儲到FT245RL的接收緩沖區(qū)(接收FIFO);外控制器隨即驅(qū)動RD引腳由高變低產(chǎn)生讀控制時序,即可讀取接收FIFO中數(shù)據(jù)到外控制器的數(shù)據(jù)緩沖區(qū)。重復(fù)上述接收數(shù)據(jù)步驟即可實現(xiàn)一幀數(shù)據(jù)的接收,然后即可進行幀處理,實現(xiàn)既定的功能。

圖8 接收數(shù)據(jù)時序圖

RT245RL發(fā)送數(shù)據(jù)時序圖見圖9。發(fā)送數(shù)據(jù)到上位機的過程主要是外控制器(FPGA)不斷查詢FT245RL的TXE引腳電平,當其為高電平說明上一次寫入數(shù)據(jù)的過程還未完成;當其變?yōu)榈碗娖奖砻鱂T245RL發(fā)送邏輯空閑,外控制器將所需發(fā)送數(shù)據(jù)準備好后,驅(qū)動WR引腳由高到低產(chǎn)生下降沿即可將緩沖區(qū)內(nèi)數(shù)據(jù)寫入FT245RL的發(fā)送FIFO,隨后FT245RL在適當?shù)臅r候自動將數(shù)據(jù)發(fā)送給上位機,重復(fù)上述發(fā)送數(shù)據(jù)步驟即可實現(xiàn)上傳數(shù)據(jù)給上位機。

圖9 發(fā)送數(shù)據(jù)時序圖

4.2 VB上位機軟件設(shè)計

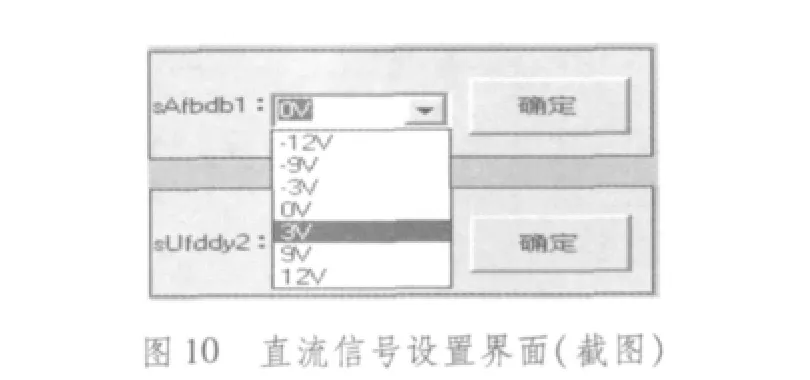

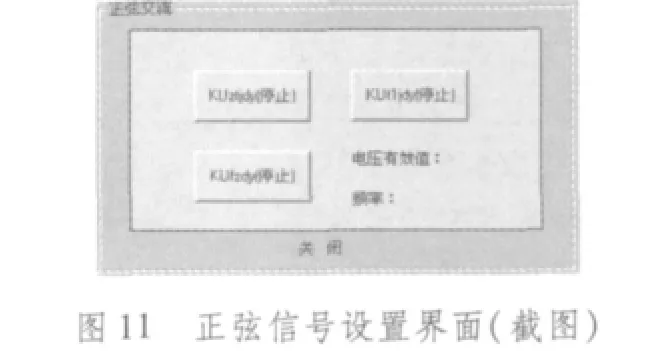

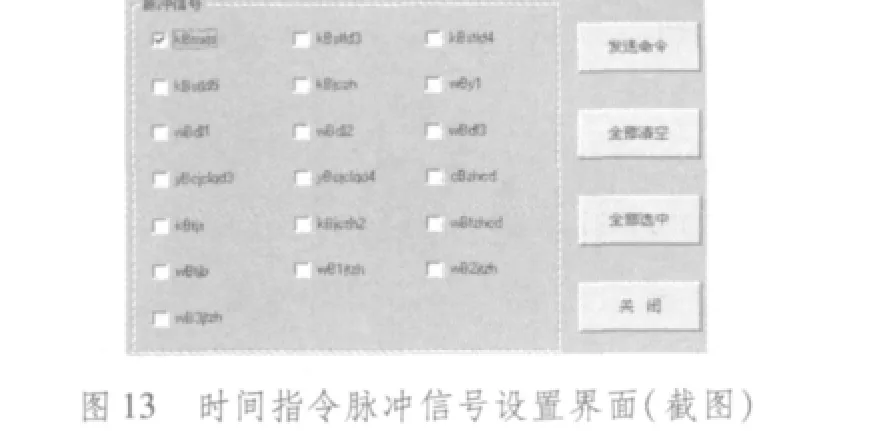

設(shè)計由各硬件電路模塊實現(xiàn)任務(wù)要求的具體功能,由上位機對整個等效器的工作進行整體控制,上位機通過發(fā)送啟動命令、設(shè)置參數(shù)與等效器進行數(shù)據(jù)交互。上位機與等效器通過USB總線接口進行通信,通信協(xié)議參見“等效器應(yīng)用層協(xié)議”。其中每一類信號的命令信息幀根據(jù)“等效器統(tǒng)一幀結(jié)構(gòu)”的格式而制定,上位機與等效器硬件電路的數(shù)據(jù)通信流程嚴格按照“上位機向主控模塊發(fā)送命令通信協(xié)議”的規(guī)定執(zhí)行,具體見圖10~圖13。

5 測試結(jié)果

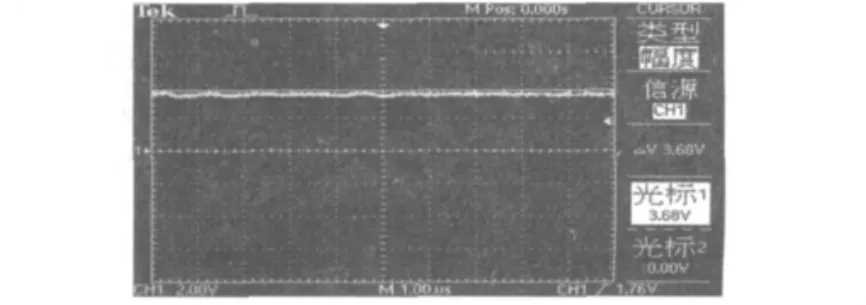

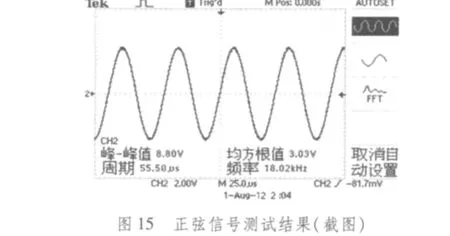

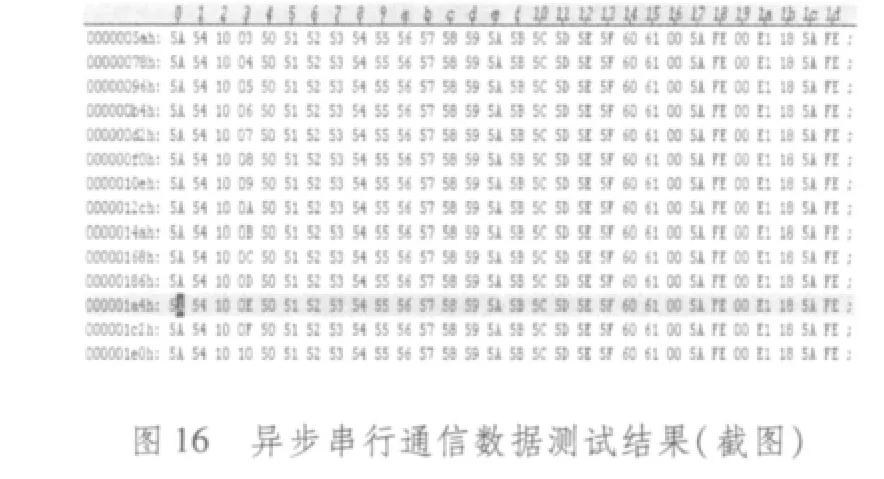

圖14為按照圖10的設(shè)置測試一路直流信號的結(jié)果;本文設(shè)計的是多路固定頻率和固定幅值的正弦信號,圖15為按照圖11測試的一路峰峰值為9 V、頻率為18 kHz的正弦信號的結(jié)果;圖16為按照圖12的設(shè)置測試了異步串行通信數(shù)據(jù)幀的結(jié)果數(shù)據(jù)(確認幀和否認幀與此類似);圖17為按照圖13的設(shè)置測試了一路幅值是28 V的100 ms時間指令脈沖信號,由此可見本文設(shè)計的等效器能很好地提供遙測設(shè)備在系統(tǒng)地面測試對外系統(tǒng)控制和測量參數(shù)的要求。

圖14 直流信號測試結(jié)果(截圖)

6 結(jié)束語

本文提出一種外系統(tǒng)等效器的設(shè)計及實現(xiàn)方案,利用模塊化工程設(shè)計思想,將整個等效器任務(wù)按照功能要求分為各個子模塊單獨實現(xiàn),在實現(xiàn)功能的基礎(chǔ)上充分保留設(shè)計裕量,以備對系統(tǒng)進行升級改進,進行彈性設(shè)計,可以很好地測試外系統(tǒng)遙測設(shè)備的可靠性和監(jiān)測功能。此方案實現(xiàn)的等效器已成功應(yīng)用于某型號航天器遙測設(shè)備的地面測試系統(tǒng)中,經(jīng)調(diào)試和測試后,該等效器工作穩(wěn)定,滿足工業(yè)現(xiàn)場的要求,達到設(shè)計目的。

[1]李娜,孟令軍.用FT245BM實現(xiàn)FPGA與PC機的數(shù)據(jù)無縫傳輸[J].重慶工學(xué)院學(xué)報:自然科學(xué)版,2009,23(5):80-83.

[2]孫立輝,劉院英,和志強.基于FT245BM和FPGA的USB接口設(shè)計[J].微計算機信息,2006(2):183-185.

[3]高世杰,竺曉山,吳志勇,等.基于USB2.0的多路異步串行系統(tǒng)設(shè)計[J].電視技術(shù),2005,29(7):91-93.

[4]陳志良,曾浩.基于DSP+FPGA視頻信號處理器的USB擴展及應(yīng)用[J]. 電視技術(shù),2011,35(23):44-47.