嵌入式UART的設計及FPGA驗證

朱 勤, 錢 敏, 楊翠軍, 朱 靜

(①蘇州大學 電子信息學院微電子系,江蘇 蘇州 215006;②蘇州工業職業技術學院,江蘇 蘇州 215104)

0 引言

目前,現場可編程門陣列(FPGA,Field-Programmable Gate Array)的應用已十分普遍,在EDA技術中擔當重要角色。基于FPGA的可編程片上系統(SOC/SOPC,System on Programmable Chip)設計功能日益強大,開發周期短、可重復編程等優點越來越明顯;軟硬件設計之間的界限由于硬件描述語言(HDL,Hardware Description Language)的出現被打破,數字系統硬件設計用軟件的方法來實現,使設計靈活、修改方便,成為推動EDA技術發展的關鍵因素[1-3]。

串行通信具有傳輸線少、成本低、可靠性高等優點,所以系統間短距離通信常采用RS-232接口方式。基于 VHDL設計的異步串行通信控制器(UART,Universal Asynchronous Receiver Transmitter)IP 核(Intellectual Property,知識產權),可靈活地移植進FPGA中,用于實現該接口。相比于UART專用芯片,此方法使電路簡化,印刷電路板面積縮小,成本降低,系統可靠性提高[4]。

1 UART原理

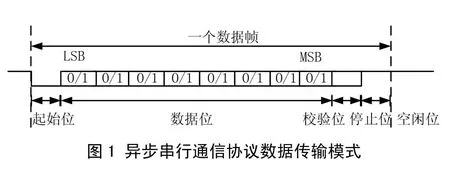

UART控制器是計算機串行通信系統中廣泛使用的接口,包含了RS-232、RS-422、RS-485等串口。其工作原理是將傳輸數據的每個字符編碼一位接著一位地傳輸,傳輸過程由波特率時鐘控制。如圖 1所示,其中各位的意義如下。

起始位:發出一個低電平信號,表示傳輸字符開始。

數據位:起始位后緊接著數據位,其位數常見的有7、8位構成一個字符,由時鐘控制從最低位開始傳送。

趙婧:現在越來越多的年輕人欣賞真實,喜歡真實記錄的東西,不喜歡演的東西。他們覺得好的內容、真實的東西可以引發自己對生活的細思細想。好的文化綜藝作品,要讓年輕人在探索世界、汲取知識的同時“遇見”自己,要讓他們看了之后更熱愛生活,這應該是今后文化綜藝進一步探索時瞄準的方向。

停止位:可以是1位、1.5位、2位的高電平,是一個數據幀的結束標志。

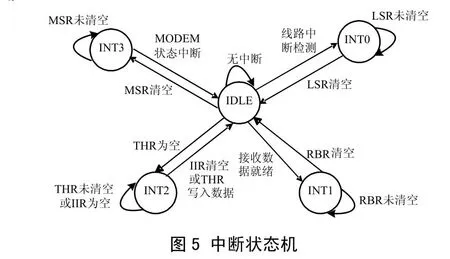

一個讀操作在 IIR上將會讀取最高優先級的中斷,而其他中斷要等待最高優先級的中斷響應之后才予以查詢。當最高優先級的中斷響應后,響應記錄也要消除,當下一次讀 IIR時就會讀到下一優先級的中斷了。中斷狀態機如圖5所示。

2 UART設計

2.1 UART設計框圖

(4)MODEM模塊

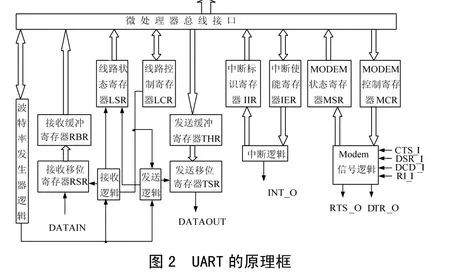

在UART中,共有10個寄存器,有8個寄存器可以被CPU訪問,需片選和地址線的配合。接收移位寄存器RSR通過DATAIN線接收數據,當RSR裝滿后,數據壓入到接收緩沖寄存器RBR,完成輸入串并轉換,然后通過 UP總線接口把數據讀取出來;發送過程是通過 UP總線接口把數據送入發送緩沖寄存器THR,一次性輸入之后,當發送移位寄存器 TSR內容為空時,把數據送入 TSR,由 TSR再通過DATAOUT線發送出去,完成輸出并串轉換;整個數據輸入輸出的過程需要一個控制波特率的時鐘來實現。幀格式通過寄存器LCR進行配置,接收和發送的狀態儲存在LSR中。

2.2 系統各模塊設計

(1)發送模塊

奇偶校驗位:數據位加上這一位后,使得“1”的位數為偶數或奇數,以此來校驗數據傳送的正確性。

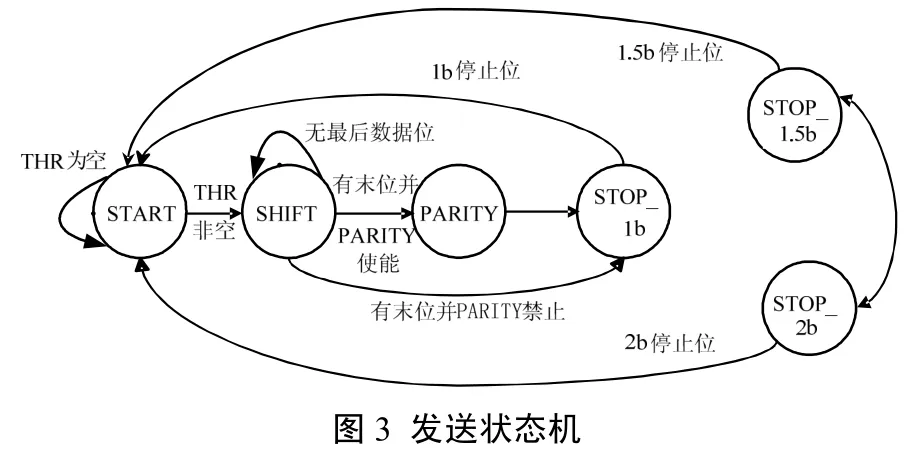

串行發送器模塊的功能是將要發送的并行數據轉換成串行數據,并且在輸出的串行數據流之前加入起始位0,之后加入奇偶校驗位1或0,最后加停止位1。組成的11位串行數據幀(起始位+數據位+奇偶校驗位+停止位)以內部時鐘CLK16X的1/16的速率送出。一個數據幀在傳送的同時THR也在寫入數據,當一幀送完后,下一幀立即開始傳送,當沒有數據傳輸時輸出端SOUT保持高電平。整個過程采用了有限狀態機來設計。發送狀態機如圖3所示。

當UART由復位管腳MR復位后,發送狀態機復位到START狀態,等待開始位的插入,這要等到THR中有數據移入,一旦開始位移出SOUT,狀態機就切換到SHIFT狀態。在SHIFT狀態下,等待有效數據位移出,當有效數據位全部移出,狀態機切換到PARITY狀態(奇偶校驗使能,否則切換到停止位狀態)。在PARITY狀態下,最后的數據位仍處在傳輸中,傳輸結束后,狀態機插入奇偶校驗位,之后,狀態機就立刻切換到停止位狀態。

自由民主的出現與自由和平等的理想聯系在一起,這些理想似乎是不言自明和不可逆轉的。但這些理想遠比我們認為的脆弱。它們在20世紀的成功取決于獨特的技術條件,而這種技術條件有可能是暫時性的。

所有試驗數據運用Microsoft Excel 2010進行分析處理;采用SPSS 18.0統計軟件中的單因素方差分析法(One-way ANOVA)比較各個處理間的差異,顯著性水平為0.05。

無論停止位是否配置為1b還是1.5b或2b,狀態機都會切換到STOP_1b狀態,等待一個波特率的時鐘周期,然后插入停止位。對停止位為1b,狀態機切換到START狀態然后等待另一幀的START位;對停止位為1.5b,狀態機切換到STOP_1.5b狀態,這個狀態是0.5b數據和1.5b長度停止位,狀態機等待半個時鐘波特率周期后再切換到START狀態;對停止位為2b,狀態機切換到STOP_2b狀態,在此狀態時第一個停止位處于傳輸狀態,等待一個時鐘周期,插入另一個停止位,切換到START狀態。

(2)接收模塊

網址:http://www.chinamet.cn E-mail:yjfx@analysis.org.cn

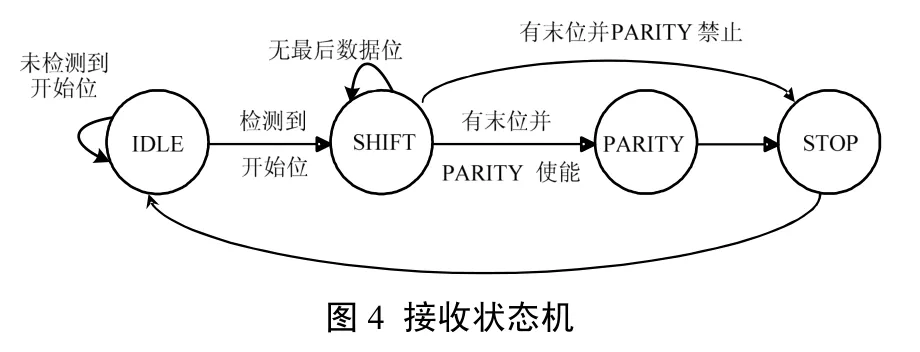

串行接收器的功能是將接收的串行數據轉換成并行數據,開始位在至少8個CLK16X時鐘內檢測到低電平,認為開始位有效。一旦一個START位在8個CLK16X時鐘內正確接收,則數據位和奇偶校驗位每 16個 CLK16X時鐘采樣一次。如果一個START位在16個CLK16X時鐘內正確接收,則后面的位在位的中間采樣。當發生任何的線路錯誤,如Overrun error, Parity error, Framing error, Break等,LSR將會顯示接收幀錯誤。接收狀態機如圖4所示。

當UART由復位管腳MR復位后,接收狀態機復位到IDLE狀態。等待SIN管腳由高到低,一旦判定是一個可用的開始位,狀態機切換到SHIFT狀態。在SHIFT狀態下,16個CLK16X時鐘讀取一位,并將它們移入RSR,當最后一位讀入后,狀態機切換到PARITY狀態。PARITY狀態中等待16個CLK16X后采樣,讀取到奇偶校驗位后狀態機轉到STOP狀態。無論停止位是1b,1.5b還是2b,狀態機都等待16個CLK16X時鐘并采樣停止位,當讀到邏輯高電平,即采到停止位,之后狀態機就自動切換到IDLE狀態。

(3)中斷仲裁模塊

當UART由復位管腳MR復位后,中斷狀態機復位到IDLE狀態。在該狀態等待使能中斷的條件,當條件匹配時,狀態機就會切換到中斷狀態的最高優先級。當最高、第二、第三、最低優先級的中斷發生時,狀態機分別依次切換到INT0、INT1、INT2、INT3狀態,直到如圖5上所示的寄存器被訪問讀取。只要IER中斷響應的使能位和中斷條件匹配,中斷就會持續發生。

空閑位:處于高電平表示當前線路上沒有數據傳送。若空閑位后出現低電平,則表示下一數據幀的起始位[5-7]。

UART將中斷申請分為4個優先級,這樣可減少外部對內部的查詢。按中斷優先級排序為:接收線路狀態;接收數據準備完備;THR清空;MODEM狀態。

接收器從 SIN(串入)端口接收異步串行數據并執行串并轉換。發送器從CPU接收8位的并行數據并執行并串轉換。為了同步異步串行數據并保證數據的完整性,采用了標準異步通信格式,且發送器和接收器共用一個 CLK16X時鐘,該時鐘是UART接口時鐘的16倍,可從外部的輸入時鐘直接得到。UART的原理框圖如圖2所示。

選取2017年1月~2017年12月期間來我院接受治療的60例心肌梗塞患者,按年齡分為年輕組(年齡≤40歲)和對照組(年齡>40歲),年輕組患者有30例,其中男22例,女8例,對照組患者有30例,其中男18例,女12例。所選患者都符合WHO公布的心肌梗塞診斷標準,并都進行了冠狀動脈造影檢查。

MODEM模塊用來和外部的UART設備通信,主要通過兩個寄存器MCR和MSR進行。外部管腳輸入信號改變MSR,通過微處理器接口讀出。MCR用來控制DTRN和RTSN的輸出,MCR的配置通過外部微處理器接口輸入。還可監視外部輸入信號DCDn、CTSn、DSRn、Rin。

傳統建筑承載了村民的居住習慣。堂屋是傳統農村建筑的核心,起居功能皆環繞堂屋發生。而新農村建設帶來的“高大建筑”“平直馬路”令傳統建筑的特色與所處環境消失殆盡。隨著農村生活條件的好轉,越來越多的自建房取代傳統的建筑。自建房多數采用城市住宅的空間構成方式,以客廳為生活中心;傳統的起居軌跡漸漸消失,年輕人開始對一些傳統的設施和用具感到莫名。

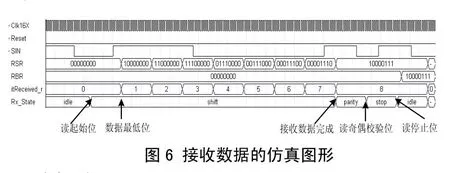

3 模塊功能仿真

系統功能和時序仿真是EDA設計的必經步驟。圖6是接收數據的仿真圖形,可以看出接收端SIN上的數據序列為“01110000101”(數據位由低到高讀取),起始位“0”后為數據位“10000111”,緊接著奇偶校驗位“0”(設置為偶校驗)和停止位“1”,數據依次串行輸入RSR中,RSR裝滿后,數據再一次性壓入到RBR中,完成輸入串并轉換的過程。

圖7是發送數據的仿真圖形,可以看到THR中待發送數據為“10000111”,將待發送數據再加上起始位、奇偶校驗位、停止位,并從最低位開始發送,則發送端SOUT的數據序列為“01110000101”(數據位由低到高排列)。數據接收和發送功能完全正確。

4 硬件實現

FPGA硬件驗證是基于IP cores的嵌入式系統設計的手段和主要目的。設計中采用2種手段進行了驗證:

2.為了使課堂教學適應現代外語教學電教化的特點和我國許多中小學已經大量使用多媒體教學的現狀,教師在本課程中要堅持使用多媒體課件和教學錄像進行教學,并使之得到推廣。

1)單端發送測試,即FPGA系統設計成發送端,通過所嵌入的UART IP core向PC系統串口發送數據,PC端超級終端軟件通過PC中的UART接收數據并在屏幕上顯示出來;UART IP接口的傳輸格式為:8 bit數據、無校驗位、1 bit停止位、波特率默認為115200bps,為簡單起見,UART只用了RX、TX,沒有使用其它控制信號,所以超級終端的數據流控制選擇“無”。PC端通過com1_115200_8n_1n.ht來打開超級終端測試。超級終端的打開方法:開始->程序->附件->通信->超級終端。在打開超級終端時會提示設置UART的屬性。經測試,數據傳輸正常。

2)回環測試,用于測試UART的RX、TX(收、發)是否正常,即PC端通過系統UART向FPGA系統發、收數據,FPGA系統通過嵌入式UART IP收、發數據。在做測試時用了收發測試軟件工具“串口大師”,傳輸波特率設為115200bps。在發送框內輸入一個測試數據(如a5),按一下發送按鈕,就會馬上在接收框看到測試數據,經測試,RX,TX都能夠正常工作。回環測試的結果如圖8所示。

專業綜合實訓實驗室是高校實驗室的一個重要組成部分,通過專業綜合實訓環節,將學生的創新能力的培養具體規范地納入實訓教學計劃之中。建立各種系統的、操作性強、特色鮮明的大學生創新能力培養的實訓體系,可以把創新能力培養貫穿于實訓教學全過程。在實訓過程中,培養學生的設計能力、創新能力、動手能力和跨專業的綜合應用能力。系統從設計到實現需要多學科的結合及團隊各成員的分工協作、共同努力,培養了學生的團隊協作精神。另外構筑開放式實訓教學新體系,還可以為大學生各類科技競賽及創新創業訓練,營造良好的科研環境、創新環境和創新氛圍。

圖8 硬件收發回環測試的軟件界面

5 結語

介紹了UART IP核在FPGA上的設計實現,并通過實際電路驗證了系統設計的正確性。該UART IP核完全采用HDL語言編寫,可以很大程度地減少電路板的使用面積,且移植性好、可重構、可編程,能很好的應用到SOC中去,具有很高的應用價值。

[1] 王成端.微機接口技術[M]. 第3版.北京:高等教育出版社,2009:164-171.

[2] 劉愛榮,王振成,曹瑞,等.EDA技術與CPLD/FPGA開發應用簡明教程[M].北京:清華大學出版社,2007:3-13.

[3] 潘松,黃繼業.EDA技術與VHDL[M].北京:清華大學出版社,2009:4-13.

[4] 趙海登,劉曉文,胡景軍,等.基于FPGA的UART IP核設計實現[J].通信技術,2009,42(05):177-179.

[5] 吳玲達,楊冰,楊征.計算機通信原理與系統[M].長沙:國防科技大學出版社,2008:1-10.

[6] 張凱,林偉.VHDL實例剖析[M].北京:國防工業出版社,2004:304-349.

[7] 徐小明,蔡燦輝.基于FPGA的數字下變頻(DDC)設計[J].通信技術,2011,44(10):19-21.