基于CPLD的LED大屏幕顯示控制系統

郭志冬

(三門峽職業技術學院 機電工程系,河南 三門峽 472000)

0 引 言

LED電子顯示屏是集微電子技術、光電子技術、計算機技術、信息處理技術以及視頻技術于一體的高科技大屏幕顯示系統。它具有色彩鮮艷、亮度高、工作電壓低、耗電量少、壽命長、驅動簡單、動態范圍廣、性能穩定等優點,廣泛應用在軍事、鐵路、民航、賓館、體育、會議廳堂、廣告宣傳、高速公路、商場、文化廣場、銀行、證券市場等多個領域[1]。

LED電子顯示屏的發光部分由LED發光二極管點陣拼裝組成的,即構成LED陣列。隨著社會發展的需要和科技的進步,LED顯示屏的超大規模要求日益突出,顯示實時性要求也越來越高。本設計將給出一種能滿足大規模要求和實時性要求的系統模型,通過CPLD的引入,實現了LED屏自動掃描的功能,大幅提高了LED屏的頻率,同時分擔了CPU的任務,提高了CPU的處理能力[2]。

1 點陣顯示原理

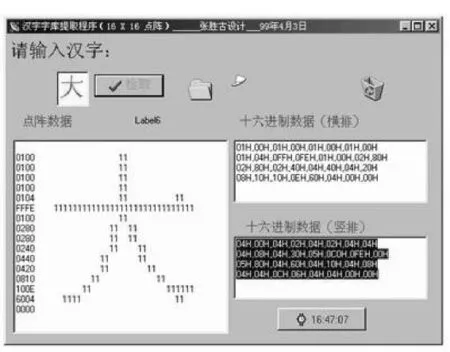

本設計采用的LED點陣模塊是由4塊點陣共16×16=256個LED發光二極管組成,可以用來顯示漢字、英文、字母及簡易圖形。若要用點陣發光二極管顯示漢字,首先要將漢字放在一個方塊內,方格塊分成16×16共256個小方格。在方塊內寫上漢字,在有筆畫下落處的小方格里填上“1”,無筆畫處填“0”。這樣就形成了一個漢字二進制數據,將若干個漢字形成的數據組按一定規律排列,并把它貯存在存儲器內,就完成了漢字庫的建立工作。不過現在有很多現成的漢字字模生成軟件,不必自己去畫表格算代碼。字模提取軟件如圖1所示。

圖1 軟件取字視圖

軟件打開后先輸入漢字,再點“檢取”,由十六進制數據組成的漢字代碼便可自動生成,我們只需把所要的豎排數據復制到程序中即可。設計者把行列總線接到單片機的I/O口,再把分析得到到的掃描代碼送入總線,裝入存儲器,便得到了顯示的漢字信息[3]。

2 設計方案確定

本設計采用串行輸出動態掃描的方法,此方法電路結構簡單,譯碼電路也容易設計,適合應用在大屏幕設計中。采用動態掃描方法,其掃描速度必須大于一個下限值才能保證信息穩定顯示。此外,顯示信息提取、緩存數據更新以及輸出數據鎖存均需要時間;特別是采用了串行數據輸出模式,數據由并行轉換為串行、移位輸出,占用了更多CPU的處理時間[4]。

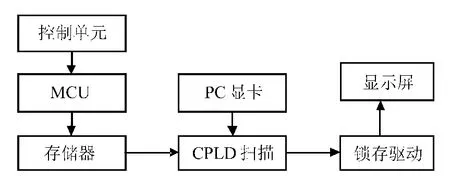

因此,大屏幕顯示引入CPLD來實現。系統核心是以CPLD構造的高速掃描電路顯示數據的提取,并行轉換為串行及掃描信號的產生都由高速的CPLD掃描電路控制。這樣就把原本由CPU軟件來完成的操作由硬件來實現,一方面提高了LED屏的頻率,另一方面分擔了CPU的工作。系統結構框圖如圖2所示。

圖2 系統結構框圖

高速的CPLD掃描電路實現的部分操作,使CPU操作得到了很大程度的簡化。CPLD具有高頻率工作特性,這就使它能高速地完成數據提取、并串轉換以及移位輸出;還能夠很好地實現掃描同步、掃描譯碼輸出。另外,此系統工作于單CPU模式,操作比較方便。

系統可分為數據產生、掃描輸出和鎖存驅動三大模塊。其中,數據產生模塊的控制單元是人機交互接口,可以是PC機,或者其它具有數據處理和通信連接的設備。MCU主要用于數據接收、存儲控制。存儲器可采用Flash存儲器,可以電擦除和編程。掃描輸出模塊利用VHDL硬件描述語言和CPLD器件的高速特性,保證了RAM數據更新及數據刷新速度。

采用Altera公司的PLD開發工具QuartusⅡ,使用邏輯電路搭建方式或者VHDL語言方式進行邏輯設計,并對所設計的邏輯進行編譯、仿真,最后將設計好的邏輯寫入Altera的可編程邏輯器件中[5]。

3 CPLD的設計

3.1 芯片的選擇

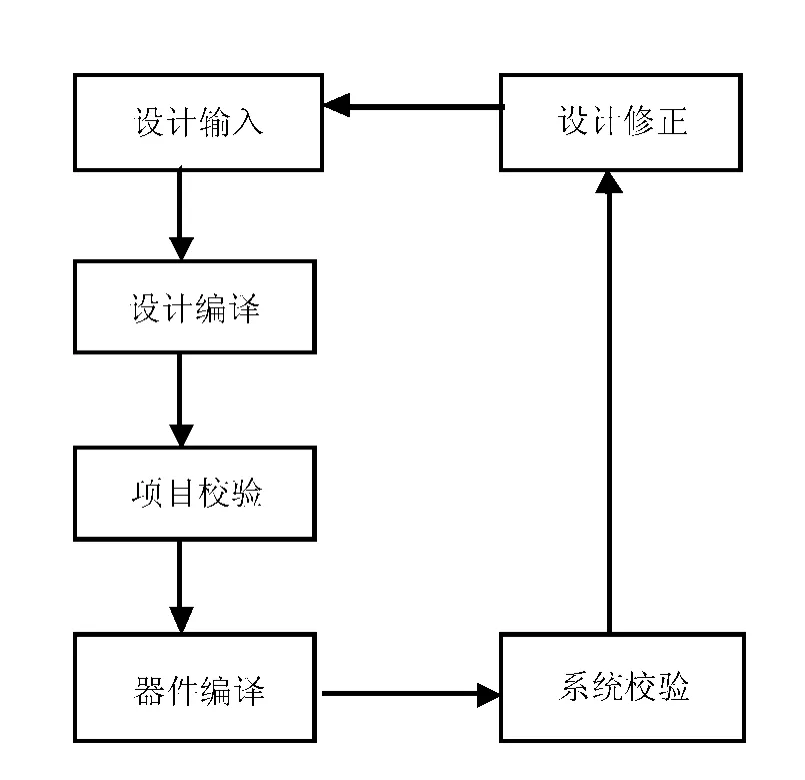

本設計使用Altera公司的FLEX10K系列可編程邏輯器件中的EPF10K10LC84-4。FLEX10K系列器件是高密度陣列嵌入式可編程邏輯器件系列。由該公司的QuartusⅡ開發系統提供軟件支持,可在PC機上運行。其結構更復雜、功能更強大。從最初的電路設計思想到QuartusⅡ的時序仿真,一般開發流程如圖3所示[6]。

圖3 開發流程圖

3.2 系統原理與設計

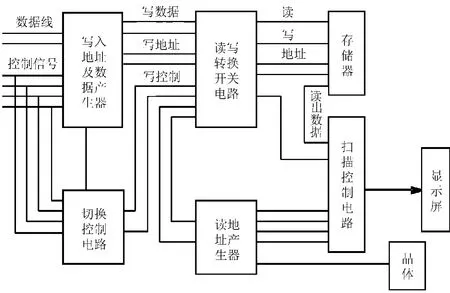

3.2.1 系統原理圖系統原理如圖4所示。

圖4 系統原理圖

首先,計算機要把顯示的信息轉換成和LED對應的點陣數據和地址,然后通過專用接口電路及單片機與CPLD接口電路把它送入掃描板的寫入地址以及數據產生器中。寫入地址及數據產生器的作用是產生要寫入存儲器的數據和地址。切換控制電路的作用是當有數據要寫入存儲器時就產生寫控制信號。讀寫轉換開關電路根據控制信號來決定完成以下兩種操作的哪一種:是把寫數據和寫地址同存儲器連接還是把讀數據和讀地址同存儲器連接。讀地址產生器產生存儲器的讀出地址。掃描控制電路把存儲器中的數據送到顯示屏上,同時產生時鐘信號、鎖存信號和行掃描信號。

以上每個功能模塊都采用VHDL語言編寫,在每個模塊編寫完之后進行編譯,編譯成功再進行功能仿真。

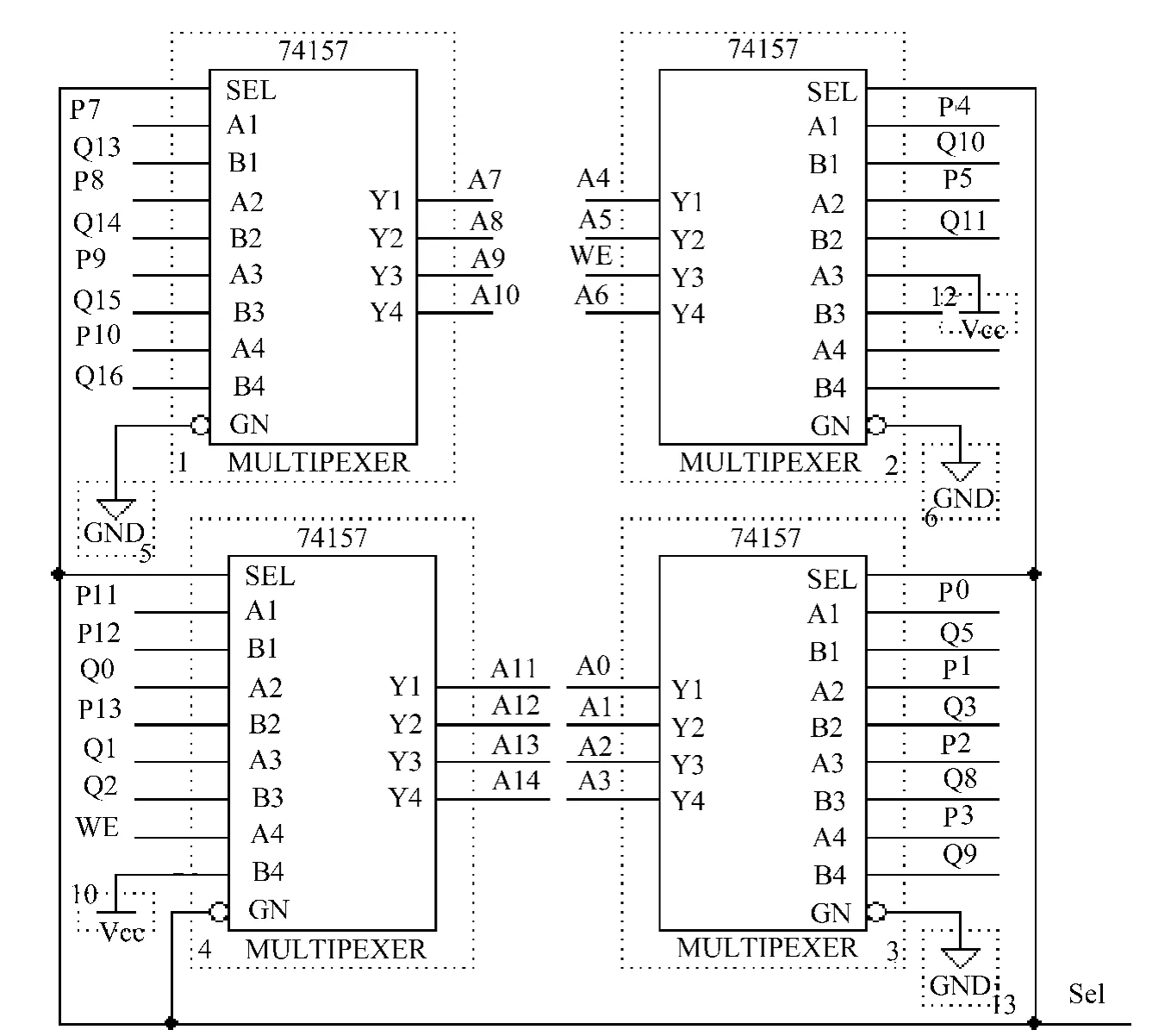

下面是采用原理圖方法實現的轉換開關電路圖,如圖5所示。

圖5 轉換開關電路原理圖

3.2.2 單片機與CPLD/FPGA接口電路

在功能上,單片機與大規模PLD有很強的互補性。單片機具有功能靈活、性價比高、人機對話易實現、數據處理能力強等特點;復雜可編程邏輯器件即CPLD則具有高速度高可靠性和開發便捷規范容易轉化為ASIC(專用集成電路)芯片等方面的優點[7]。現今,很多高性能儀器設備和智能電子產品中將會廣泛采用以CPLD和單片機兩類器件相結合的電路結構。CPLD與單片機的接口方式有兩種,即總線方式與獨立方式,本設計采用總線接口方式進行數據通信[8]。

單片機以總線方式與復雜可編程邏輯器件CPLD進行數據通信有許多優點。比如只需一條單字節指令就能完成所需的讀/寫時序。如:

MOV@DPTR,A;

MOV A,@DPTR。

CPLD與MCS-51單片機的總線接口通信的VHDL源程序編寫時要注意雙向端口RAM的VHDL語言描述。803l以總線方式工作,例如,由8031將數據5AH寫入目標器件中的第一個寄存器LATCH_OUTl的指令是:

MOV A,#5AH

MOV@DPTR,,#6FF5H

MOVX@DPTR,A

當READY為高電平時,8031從目標器件中的寄存器LATCH_INl將數據讀入的指令是:

MOV@DPTR,#9F7EH

MOVX A,@DPTR

3.2.3 系統設計

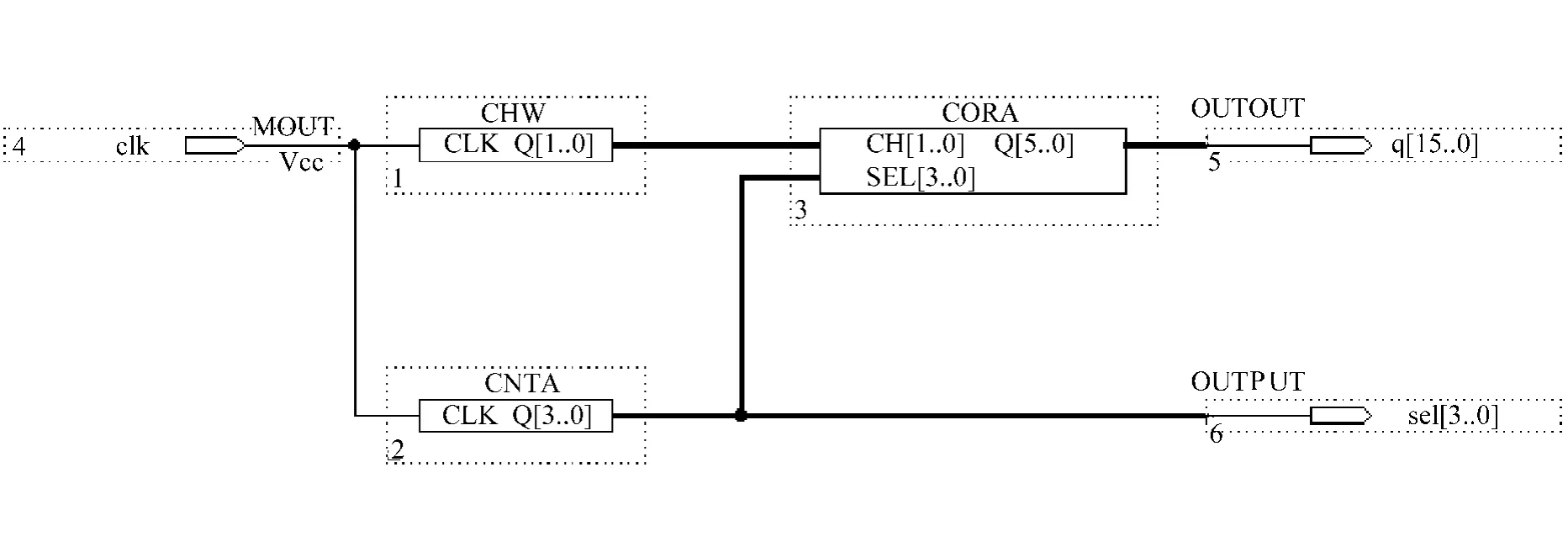

利用層次化設計方法,先組建底層設計,然后實現頂層設計。EDA工具軟件提供了良好的邏輯綜合與優化功能,它能夠將設計人員設計的邏輯級電路圖自動地轉換為可供綜合的門級電路,并生成相應的網表文件、時序分析文件及各種報表,最終生成可編程下載的文件。本系統中先將各個子模塊進行編譯,先生成子模塊符號,然后建立頂層設計文件,在頂層設計文件中調入生成的各個子模塊符號,經過恰當的連接即可得到設計頂層文件。CPLD掃描控制電路的設計頂層文件Top.gdf如圖6所示。

圖6 掃描控制電路頂層原理圖

可以使用逐列循環掃描的方式來不間斷地顯示“VHDL”這4個英文字母。CPLD掃描控制電路包括以下3個模塊:模塊CHW,此模塊控制每一個漢字或字母顯示的時間,改變常數可改變顯示時間的長短;模塊CNTA,此模塊產生列選擇信號;模塊CORA,此模塊對應列選擇信號輸出每一列對應的數據,點亮相應的燈管。

3.2.4 編譯仿真與項目校驗

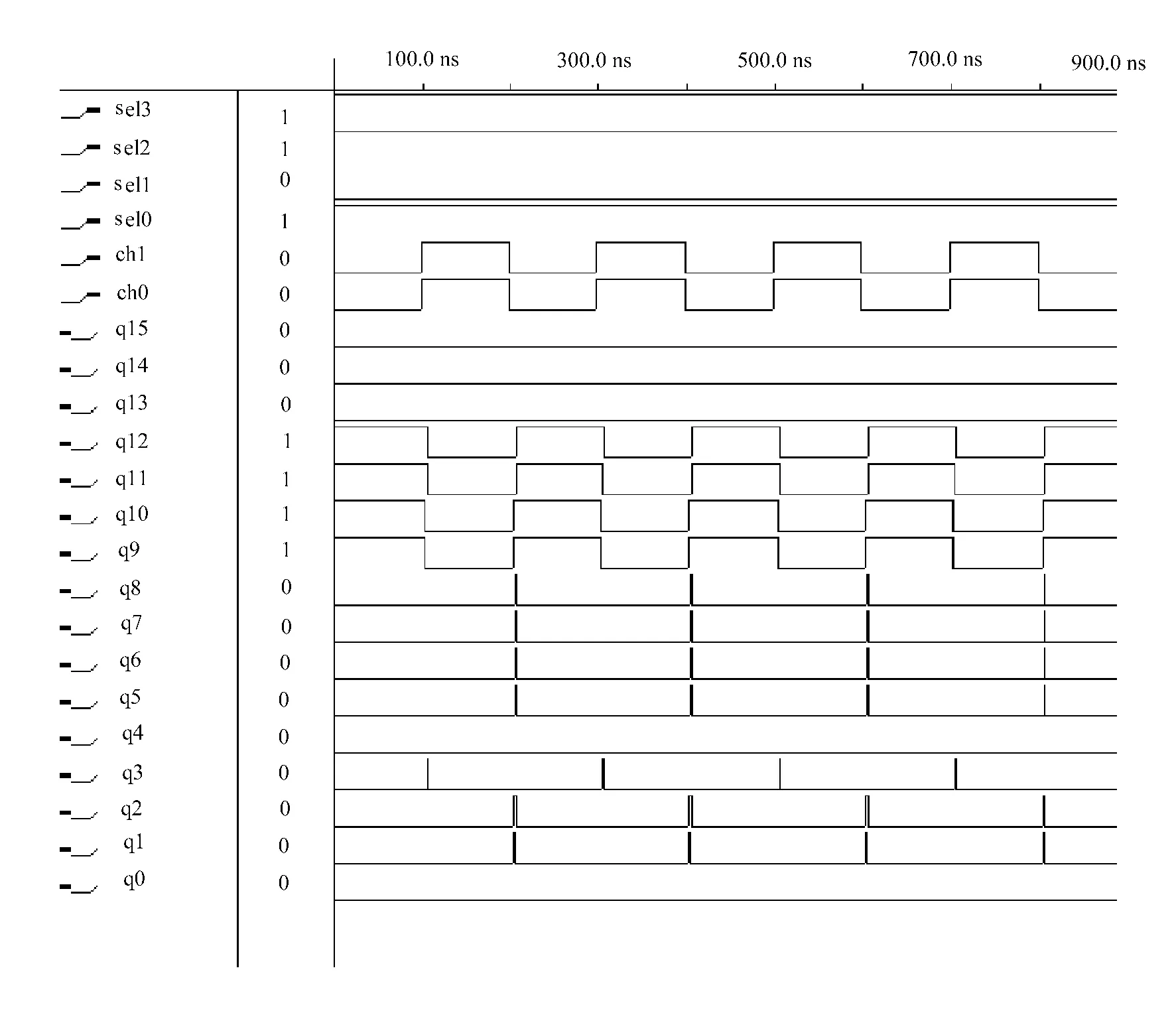

在對頂層設計文件“Top.gdf”構成的項目“Top”編譯前,先選擇目標器件,本設計使用Altera公司的FLEX10K系列可編程邏輯器件中的EPF10K10LC84-4,然后進行編譯。編譯過程中將產生一系列標準文件可進行時序模擬、適配,完成對設計的功能、時序仿真。時序仿真時進行時序分析,判斷輸入輸出時間的延遲。對掃描控制模塊進行時序仿真后得到輸出波形,通過波形圖中輸入輸出波形的對比,可以很容易看出預定項目的完成情況。本系統在設定了CLK,SEL信號的情況下,經過仿真后,設計的各信號的延遲在2 ns左右,基本符合設計指標要求。波形圖如圖7所示。

圖7 時序波形圖

4 結 語

系統采用以CPLD為核心來控制LED顯示屏的方法,此方法把本來由軟件進行的數據提取、并串轉換以及移位輸出和鎖存等復雜的操作,交由CPLD硬件實現,大大提高了系統的可靠性。引入CPLD極大地簡化了軟件的編程,并且因為CPLD器件具有高速特性,能夠使超大規模的LED顯示屏的刷新速度得以保證[8]。此外,CPLD掃描電路的核心模塊可通過PC顯示卡接口,如此就可以借助計算機平臺,將LED顯示屏很好地應用于高速實時顯示領域,滿足了現如今對LED顯示屏實時性的要求,具有非常廣泛的應用價值。

[1]曾和蘭,劉登桃.基于STC11L08的動畫顯示控制器[J].長春工業大學學報:自然科學版,2011,32(4):399-403.

[2]童星,熊文龍.基于CPLD的LED顯示控制板[J].武漢理工大學學報:交通科學與工程版,2007(1):144-147.

[3]諸昌鈴.LED顯示屏系統原理及工程技術[M].成都:電子科技大學出版社,2000:35-157.

[4]劉愛榮,王振成.EDA技術與CPLD/FPGA開發應用簡明教程[M].北京:清華大學出版社,2007:321-321.

[5]莊鎮泉,胡慶生.電子設計自動化[M].北京:科學出版社,2000:3-15.

[6]潘松,王國棟.VHDL實用教程[M].成都:電子科技大學出版社,2000:5-15.

[7]唐楊波.基于單片機和CPLD共同控制的的LED大屏幕顯示系統的設計與實現[J].科技創新導報,2009,13:24-25.

[8]馬海濤,劉玉川,莊然,等.基于CPLD的時差法在小管徑流量測量中的應用[J].長春工業大學學報:自然科學版,2007,28(3):264-266.