基于FPGA的圖像分塊實(shí)時(shí)邊緣檢測系統(tǒng)

陸小鋒,張俊豪,陸曉成,沈蘇旻

(上海大學(xué)通信與信息工程學(xué)院,上海 200072)

1 圖像邊緣檢測算法

圖像邊緣是圖像的基本特征,這些信息可以用于圖像分析、目標(biāo)識別以及圖像濾波[1]。圖像算法的處理可以用軟件或者硬件來實(shí)現(xiàn),而對于實(shí)時(shí)圖像處理來說,需要很高的速度要求,因此通常采用硬件進(jìn)行圖像處理[2]。目前,圖像處理的硬件設(shè)計(jì)有兩種技術(shù)方案,一是全定制的專用集成電路(ASIC),二是半定制的數(shù)字信號處理器(DSP)以及現(xiàn)場可編程門陣列(FPGA),二者在設(shè)計(jì)中的運(yùn)用都可以大大加快對信息的處理速度[3]。

目前邊緣檢測算法已有一系列基于微分的邊緣檢測算子,如 Roberts算子、Sobel算子、Prewitt算子、Canny算子等[4]。Sobel算子是邊緣檢測中常用的一種模板,其有3種算子,分別用于檢測水平邊緣、垂直邊緣以及對角邊緣。Sobel算子在運(yùn)算上不涉及復(fù)雜的數(shù)據(jù)運(yùn)算,適用于實(shí)時(shí)性要求高的環(huán)境。并且與Prewitt算子相比,Sobel算子對于像素的位置影響做了加權(quán),降低了邊緣的模糊程度,效果更好[5]。由于Sobel算子檢測得到的是整幅圖像的梯度值,最后還需要用圖像分割算法對圖像的梯度采取閾值處理。

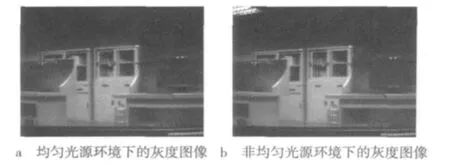

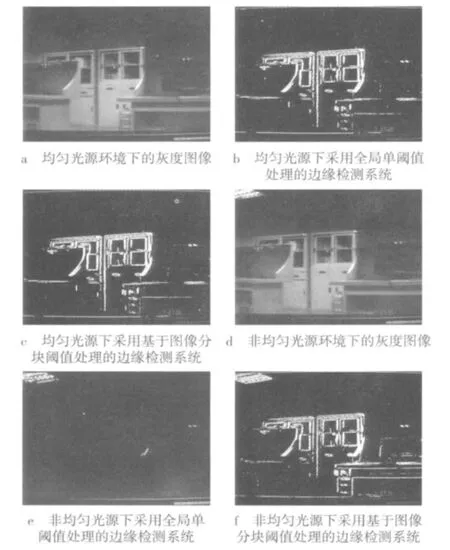

由于已經(jīng)用Sobel算子檢測得到了圖像的梯度值,在均勻光照環(huán)境下,邊緣部分和非邊緣部分的灰度直方圖間存在一個(gè)相當(dāng)清晰的波谷,因此可以采用適合于整個(gè)圖像的全局單閾值處理。但是當(dāng)圖像中存在非均勻光源部分,會使得閾值偏大,導(dǎo)致圖像中部分梯度值較小的邊緣容易被漏檢。如圖1a為均勻光源環(huán)境,圖像中各部分的光照程度近似。而圖1b為非均勻光源環(huán)境,由于圖像的左上角存在白熾燈,會造成此部分的梯度值偏大,很大程度上會影響圖像的邊緣檢測效果。

圖1 均勻光源與非均勻光源環(huán)境下的灰度圖像對比

文獻(xiàn)[8]中提到了一種簡單根據(jù)圖像的灰度值將其分成高灰度值部分和低灰度值的部分,然后對這兩部分分別進(jìn)行邊緣檢測。這種方法,在一定程度上能夠補(bǔ)償光源不均勻性。但是由于其簡單針對圖像的灰度進(jìn)行分組,效果有限。

本文改進(jìn)了這種根據(jù)圖像灰度值進(jìn)行分組的思想。對采集到的圖像進(jìn)行Sobel邊緣檢測處理后,根據(jù)圖像的梯度值進(jìn)行分組。并在全局單閾值處理算法基礎(chǔ)上,將其分別運(yùn)用分組后的子圖像中。

2 基于圖像分塊的邊緣檢測系統(tǒng)及其FPGA實(shí)現(xiàn)

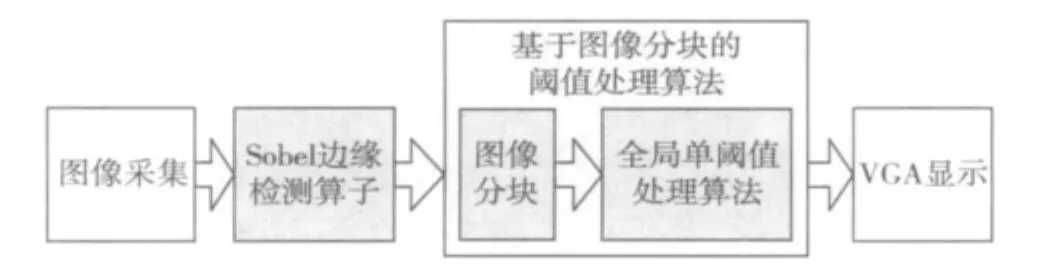

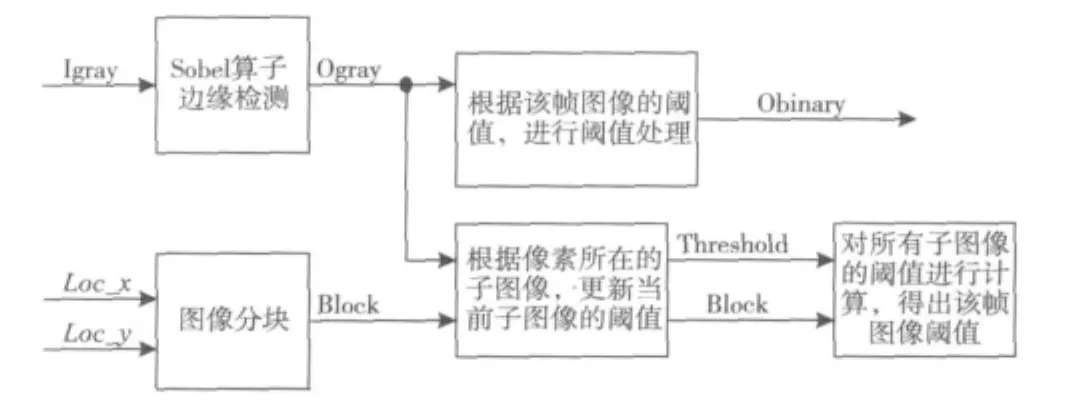

圖2為基于圖像分塊的邊緣檢測系統(tǒng)的軟件設(shè)計(jì)框圖。系統(tǒng)改進(jìn)了全局單閾值處理算法,根據(jù)圖像的梯度值進(jìn)行分組,提出了一種IEDIP(Improved Edge Detection based on Image Partition)算法。該算法先通過Sobel邊緣檢測算子對采集到的圖像進(jìn)行梯度計(jì)算,并根據(jù)圖像的梯度值將其分為若干個(gè)子圖像。然后對各個(gè)子圖像分別采用全局單閾值處理,最后將所有子圖像的閾值通過簡單的計(jì)算得出一個(gè)新的閾值,并以此作為當(dāng)前整幅圖像閾值。

圖2 基于圖像分塊的邊緣檢測系統(tǒng)的軟件設(shè)計(jì)框圖

2.1 Sobel邊緣檢測算子及其FPGA實(shí)現(xiàn)

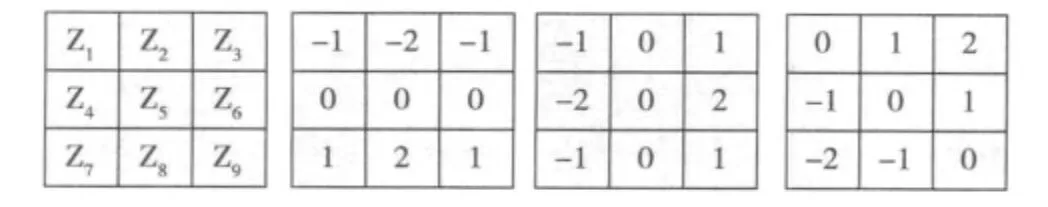

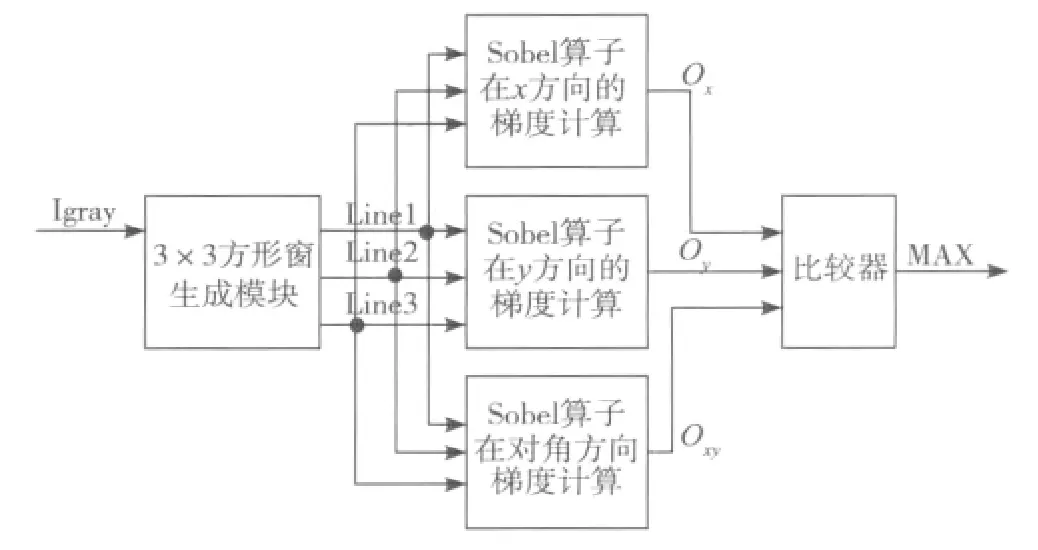

系統(tǒng)采用3×3的Sobel算子分別計(jì)算3個(gè)方向的梯度值,分別為x方向、y方向和對角線方向,通過比較3個(gè)方向的梯度值,取其中的最大值作為該點(diǎn)的梯度值,Sobel算子在3個(gè)方向的檢測模板如圖3所示[9]。

圖3 檢測3個(gè)方向邊緣的Sobel模板

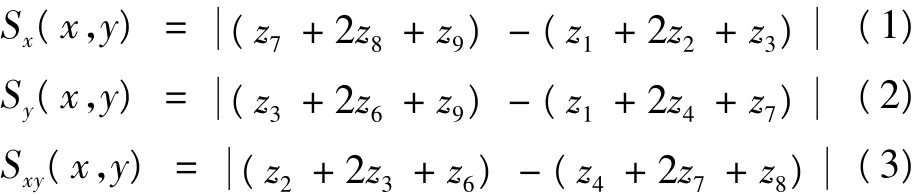

Sobel算子以檢測的像素點(diǎn)為中心,其梯度計(jì)算公式分別為

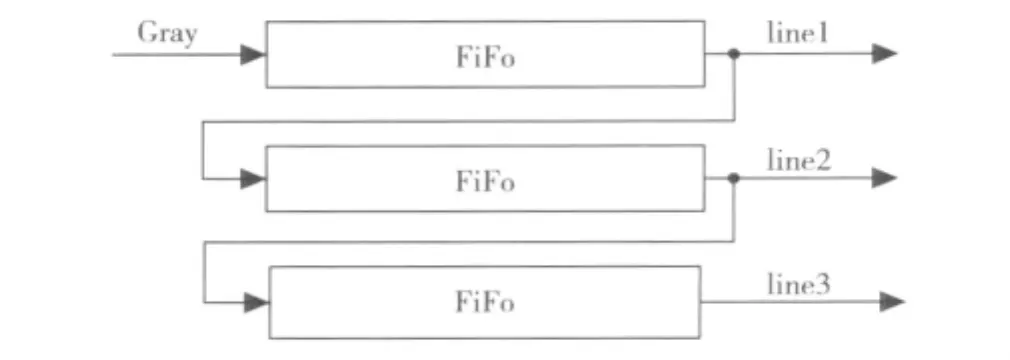

Sobel邊緣檢測算法在FPGA上實(shí)現(xiàn)需要用到3×3的方形窗,為了使窗中的3行3列共9個(gè)像素能夠在一個(gè)時(shí)刻同時(shí)輸出,便于之后的核心算法模塊進(jìn)行數(shù)據(jù)處理,在3×3方形窗的硬件設(shè)計(jì)中,本文采用3個(gè)FiFo存儲器。利用Quartus II的MegaWizard Plug-In Manager工具可以很方便地設(shè)計(jì)出符合設(shè)計(jì)需求的FiFo存儲器,設(shè)計(jì)數(shù)據(jù)位寬度8 bit,數(shù)據(jù)長度1 024,這里需要1個(gè)“almost_full”信號,在數(shù)據(jù)長度為640(VGA分辨力為640×480)的時(shí)候,表示1行像素?cái)?shù)據(jù)存儲完成,“almost_full”信號置“1”,同時(shí)FiFo開始輸出信號并將像素?cái)?shù)據(jù)發(fā)送到下一個(gè)FiFo中,具體實(shí)現(xiàn)方法如圖4所示。

圖4 3×3方形窗的FiFo實(shí)現(xiàn)結(jié)構(gòu)

在梯度計(jì)算的過程中需要對方形窗所產(chǎn)生的像素?cái)?shù)據(jù)進(jìn)行緩存,緩存數(shù)目由窗口的大小決定。每次方形窗送出像素?cái)?shù)據(jù)后,首先要將像素?cái)?shù)據(jù)緩存,然后再進(jìn)行梯度計(jì)算,輸出梯度值。通過比較器,計(jì)算3個(gè)方向的梯度,具體FPGA實(shí)現(xiàn)過程如圖5所示。

紡織品服裝類一直是我們國家貿(mào)易出口的主要產(chǎn)品,但是隨著一帶一路戰(zhàn)略的延伸,有更多的新興發(fā)展中國家,他們已經(jīng)替代我們國家最大制造生產(chǎn)國的地位,因此,雖然我們國家的服裝紡織類出口比重高于一些發(fā)達(dá)國家,高于一些工業(yè)國家,但卻低于一些后起的發(fā)展中國家。我們國家在世界紡織業(yè)的比重開始出現(xiàn)下降的趨勢。受到一些例如印度、越南新興工業(yè)制造國家的挑戰(zhàn),優(yōu)勢在喪失,因此,我們國家原有的工業(yè)基礎(chǔ)勞動力優(yōu)勢,已經(jīng)轉(zhuǎn)換為其他產(chǎn)品的出口優(yōu)勢,隨著互聯(lián)網(wǎng)經(jīng)濟(jì)的快速發(fā)展,勞動密集型的產(chǎn)業(yè)優(yōu)勢,在不斷地被沿路國家取替。

圖5 Sobel邊緣檢測算法的FPGA內(nèi)部電路原理框圖

2.2 全局單閾值處理算法及其FPGA實(shí)現(xiàn)

當(dāng)物體和背景像素的灰度分布十分明顯時(shí),可以用適合于整個(gè)圖像的全局閾值。由于已經(jīng)用Sobel算子檢測得到了圖像的梯度,邊緣部分和非邊緣部分的灰度分布十分明顯,即使全局閾值是一種合適的方法,對每一幅圖像有能力自動估計(jì)閾值的算法也是需要的[9]。下面的迭代算法可用于這一目的。

1)為全局閾值T選擇一個(gè)初始值。

2)用T分割該圖像。這將產(chǎn)生兩組像素:G1由灰度值大于T的所有像素組成;G2由所有小于等于T的像素組成。

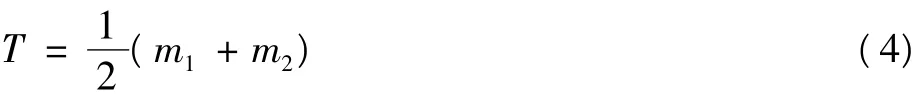

3)對G1和G2的像素分別計(jì)算平均灰度值(均值)m1和m2。

4)計(jì)算一個(gè)新的閾值,由公式為

5)重復(fù)步驟2)到步驟4),直到連續(xù)迭代中T值間的差小于一個(gè)預(yù)定的參數(shù)ΔT為止。

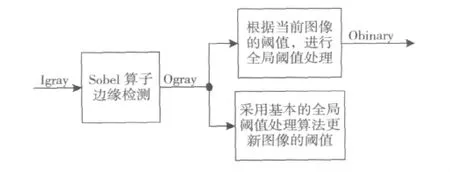

通常,ΔT越大,則算法執(zhí)行的迭代次數(shù)越少。用FPGA實(shí)現(xiàn)時(shí),采用VGA的場同步信號控制閾值計(jì)算,即每產(chǎn)生一次場同步信號,重新計(jì)算一次閾值。本設(shè)計(jì)以ΔT設(shè)定為0為例。具體FPGA實(shí)現(xiàn)過程如圖6所示,像素經(jīng)過Sobel邊緣檢測算子模塊輸出的梯度值,除了需要根據(jù)當(dāng)前閾值判斷該像素點(diǎn)為邊緣點(diǎn)或非邊緣點(diǎn)并輸出二值圖像,還要將對該像素進(jìn)行上述的全局單閾值處理算法以更新下一幀圖像的閾值。

圖6 全局單閾值處理算法的FPGA內(nèi)部電路原理框圖

值得注意的是,由于上述全局單閾值處理算法僅當(dāng)物體和背景的直方圖模式間存在一個(gè)相當(dāng)清晰的波谷時(shí),這個(gè)算法才工作得很好。但是,當(dāng)存在非均勻光源部分時(shí),由于非均勻光源部分的梯度值極大,上述算法中的G1值將顯著增大,從而導(dǎo)致閾值T的值增大,這會導(dǎo)致一些重要的邊緣像素被濾除,針對這一問題提出了下述的基于圖像分塊的閾值處理算法(EDIP算法)。

2.3 基于圖像分塊的閾值處理算法及其FPGA實(shí)現(xiàn)

IEDIP算法是將每一幀圖像分成若干個(gè)子圖像,然后針對每個(gè)子圖像分別進(jìn)行上述的全局單閾值處理,最后將所得到的各個(gè)子圖像的閾值進(jìn)行比較計(jì)算得出一個(gè)新的閾值作為下一幀圖像的閾值。由于計(jì)算得到的閾值相比非均勻光源部分子圖像的閾值明顯要小,因此能夠有效地用于補(bǔ)償光照的不均勻性,使一些重要的邊緣得以保留。

由于存在非均勻光源的子圖像經(jīng)過全局單閾值處理算法后,其閾值與其他子圖像的閾值相比較會明顯增大,從而導(dǎo)致圖像顯示的分塊。因此,最后需要對所有子圖像的閾值進(jìn)行計(jì)算,得出當(dāng)前圖像的閾值,使顯示的圖像不存在分塊的現(xiàn)象。即最后顯示的邊緣檢測圖像需要滿足兩個(gè)要求,一是顯示的圖像不存在分塊現(xiàn)象,二是能夠有效地補(bǔ)償光照現(xiàn)象,使一些重要的邊緣不被濾除。

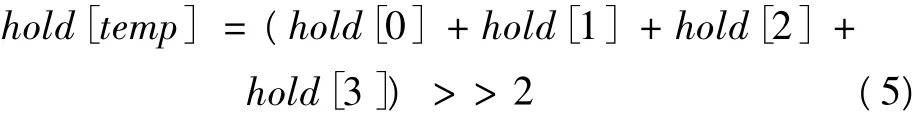

系統(tǒng)的FPGA實(shí)現(xiàn)框圖如圖7所示,首先像素需要經(jīng)過Sobel邊緣檢測算子模塊輸出得到梯度值,并且根據(jù)該像素所在的坐標(biāo)位置(Loc_x,Loc_y)將其劃分到不同的子圖像中。然后需要根據(jù)當(dāng)前這幀圖像的整體閾值判斷該像素點(diǎn)為邊緣點(diǎn)或非邊緣點(diǎn)并輸出二值圖像,并且根據(jù)該像素所在的子圖像,僅對該子圖像全局閾值處理算法以更新該圖像的閾值。最后對所有子圖像的閾值進(jìn)行計(jì)算,得出當(dāng)前圖像的閾值。由于在FPGA里面的除法很難確定需要多少個(gè)時(shí)鐘周期,視頻圖像的處理對于速度的要求相當(dāng)高。這里作了簡單地加法和移位運(yùn)算處理,即采用4塊閾值的均值代替存在非均勻光源部分的閾值,公式為

圖7 基于圖像分塊的閾值處理算法的FPGA內(nèi)部電路原理框圖

3 實(shí)驗(yàn)結(jié)果與分析

3.1 基于圖像分塊的邊緣檢測系統(tǒng)的實(shí)驗(yàn)結(jié)果

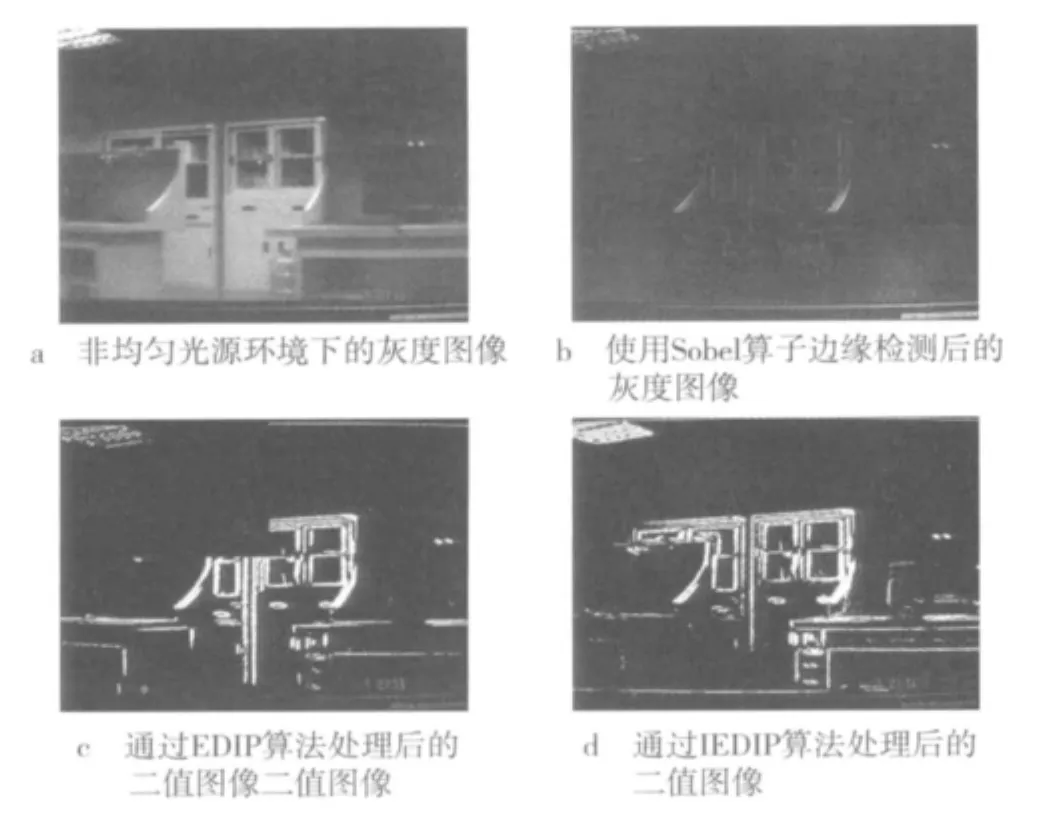

系統(tǒng)的實(shí)驗(yàn)結(jié)果如圖8所示,從圖8b可以看出,左上腳的白熾燈處的灰度值相當(dāng)大,這對于采用全局單閾值處理后的圖像相當(dāng)不利,其閾值將會向燈光的灰度靠近,即閾值變大,造成分割后的圖像邊緣信息嚴(yán)重丟失。針對此問題,采用EDIP算法將圖像進(jìn)行分塊,將白熾燈獨(dú)立在一個(gè)單獨(dú)的子圖像中,使其灰度值不影響其他3塊圖像閾值的計(jì)算,其效果如圖8c所示。但是,圖8c中可以看到明顯的分塊痕跡,這是邊緣檢測所不希望的結(jié)果,因此需要采用改進(jìn)后的IEDIP算法對4個(gè)子圖像的閾值進(jìn)行修正計(jì)算,將得出的新閾值作為此圖像的閾值,其結(jié)果如圖8d所示。

3.2 基于圖像分塊的邊緣檢測系統(tǒng)與基于全局單閾值處理的邊緣檢測系統(tǒng)的結(jié)果比較

圖8 基于圖像分塊的邊緣檢測系統(tǒng)的實(shí)驗(yàn)結(jié)果

結(jié)果比較如圖9所示,比較圖9b和圖9c可知,在均勻光源環(huán)境下采用全局單閾值處理和基于圖像分塊的閾值處理算法得出的結(jié)果基本相同,都能夠?qū)D像的主要邊緣檢測處理。由圖9e可以看出在非均勻光源的環(huán)境下采用全局單閾值處理的邊緣檢測系統(tǒng)僅將光源白熾燈的邊緣檢測出來,而且其他邊緣信息全部被濾除,這是由于左上腳的白熾燈光源處的梯度值相當(dāng)大,這樣對于采用全局單閾值處理后的圖像相當(dāng)不利,其閾值將會向燈光的灰度靠近,造成圖像的閾值偏大。由圖9f所示,在非均勻光源環(huán)境下采用基于圖像分塊的閾值處理的邊緣檢測系統(tǒng)能夠?qū)D像的主要邊緣檢測出來,和均勻光源環(huán)境下的檢測效果一樣好。相比之下,本算法對于非均勻光源環(huán)境的邊緣檢測效果明顯較好。

圖9 采用基于圖像分塊的閾值處理和全局單閾值處理的邊緣檢測算法比較

4 結(jié)束語

本文以Sobel邊緣檢測算子為基礎(chǔ),將全局單閾值處理算法進(jìn)行改進(jìn),提出了一種基于圖像分塊的閾值處理算法,先用Sobel算子計(jì)算出圖像的梯度值,然后通過將圖像分塊成若干個(gè)子圖像,針對各個(gè)子圖像分別采用全局單閾值處理,然后將所有子圖像的閾值通過簡單的計(jì)算得出一個(gè)新的閾值,并以此作為當(dāng)前圖像閾值。本算法通過FGPA得出實(shí)驗(yàn)結(jié)果,實(shí)驗(yàn)證明了該算法在非均勻光源的環(huán)境下用于實(shí)時(shí)圖像的邊緣檢測效果理想。

:

[1]GUO Z,XU W,CHAI Z.Image edge detecton based on FPGA[C]//Proc.9th International Symposium on Distributed Computing and Applications to Business Engineerng and Science(DCABES).[S.l.]:IEEE Press,2010:169-171.

[2]HOUARI K E,CHEERAD B,ZOHIR I.A software-h(huán)ardware mixed design for the FPGA implementaton of the real-time edge detection[C]//Proc.IEEE Inernational Conference on Systems Man Cybernetics(SMC).[S.l.]:IEEE Press,2010:4091-4095.

[3]甘振華,應(yīng)駿.基于FPGA的嵌入式圖像邊緣檢測系統(tǒng)設(shè)計(jì)[J].電視技術(shù),2010,34(8):43-45.

[4]QIAN X,CHAKRABARTI C,KARAM L J.A distributed Canny edge detector and its implementation on FPGA[C]//Proc.Digital Signal Processing Workshop and IEEE Signal Processing Education Workshop(DSP/SPE).[S.l.]:IEEE Press,2011:500-505.

[5]YASRI I,HAMID N H,YAP V V.Performance analysis of FPGA based Sobel edge detecton operator[C]//Proc.ICED 2008.[S.l.]:IEEE Press,2008:1-4.

[6]ZHANG J,CHEN Y,HUANG X.Edge detection of images based on improved Sobel operator and genetic algorithms[C]//Proc.IASP 2009.[S.l.]:IEEE Press,2009:31-35.

[7]GAO W,ZHANG X,YANG L,et al.An improved Sobel edge detection[C]//Proc.ICCSIT 2010.[S.l.]:IEEE Press,2010:67-71.

[8]ROUTRAY A,MOHANTY K B.A fast edge detection algorithm for road boundary extraction under non-uniform light condition[C]//Proc.ICIT 2007.[S.l.]:IEEE Press,2007:38-40.

[9]GONZALEZ R C,WOODS R E.數(shù)字圖像處理[M].3 版.北京:電子工業(yè)出版社,2011.