基于單個FFT非線性早遲窗同步系統(tǒng)設(shè)計與實現(xiàn)

蔡昆宏,趙 利,黃昌龍

(桂林電子科技大學(xué)信息與通信學(xué)院,廣西桂林 541004)

1995年美國Sanders子公司將差分跳頻應(yīng)用于其設(shè)計的相關(guān)跳頻增強型擴頻系統(tǒng)(CHESS)。與常規(guī)跳頻技術(shù)相比,差分跳頻具有以下突出優(yōu)點:差分跳頻的頻率轉(zhuǎn)移函數(shù)(G函數(shù))具備了產(chǎn)生跳頻圖案和調(diào)制解調(diào)的功能;傳輸速率高,可以實現(xiàn)高達(dá)19.2 kbit/s的數(shù)據(jù)傳輸速率;跳速極高,達(dá)到5 000跳/秒,每跳的頻率駐留時間為0.2 ms,有效提高了系統(tǒng)抗跟蹤干擾性能;采用寬帶異步接收方式,解跳不需跳頻圖案的同步。

雖然,差分跳頻解跳不需跳頻圖案的同步,但是跳沿同步性能影響著整個系統(tǒng)的頻率序列檢測性能和系統(tǒng)抗干擾性能。跳沿檢測模塊與滑動早遲窗模塊協(xié)調(diào)處理,實現(xiàn)跳沿同步。在接收端每次對一跳時間內(nèi)的信號進(jìn)行處理,相當(dāng)于對接收信號進(jìn)行了加窗,這個窗就稱為跳信號窗口[1-2]。如果差分跳頻系統(tǒng)的跳信號窗口已經(jīng)同步,則接收到的一跳信號為一個單頻信號。若跳信號窗口跟接收信號的起始時刻不對齊,進(jìn)入窗口的將有兩個信號,此時進(jìn)行判決將可能發(fā)生誤判。跳沿同步就是使跳信號窗口的起始時刻盡可能接近接收信號的起始時刻,提高判決的準(zhǔn)確度[3]。

但現(xiàn)有差分跳頻早遲窗同步系統(tǒng)采用多個FFT來識別早遲窗的頻譜能量信號,在實際應(yīng)用中消耗大量資源,特別是當(dāng)同步系統(tǒng)精度要求比較高時,F(xiàn)FT點數(shù)較大,此時快速傅里葉變換會占用大量的乘法器和加法器。因此,必須減少FFT個數(shù)達(dá)到最小以適應(yīng)實際需求。現(xiàn)有差分跳頻早遲窗同步系統(tǒng)另一個缺點是大多采用線性移動窗口來達(dá)到跳沿同步,同步鎖定時間和同步精度不能同時滿足,實際應(yīng)用缺乏靈活性,因此如果采用非線性移動窗,能同時縮短同步鎖定時間和提高跳沿同步精度。

針對現(xiàn)有差分跳頻早遲窗同步的缺點,本文通過采用單個FFT來簡化同步實現(xiàn)的復(fù)雜度,同時采用非線性移動早遲窗來減少同步鎖定時間。通過引入軟件無線電設(shè)計思想[4],在節(jié)省硬件資源的基礎(chǔ)上,全部用軟件編程的模式實現(xiàn)其硬件功能。采用Xilinx公司的System Generator工具進(jìn)行建模設(shè)計仿真,驗證系統(tǒng)設(shè)計的正確性。

1 設(shè)計原理

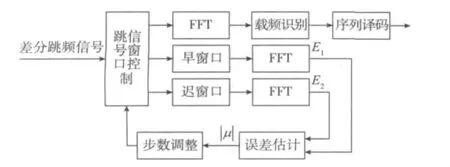

1.1 單個FFT譯碼接收原理

傳統(tǒng)DFH同步跟蹤系統(tǒng)是基于FFT信號檢測早遲窗跟蹤方法,將采樣信號分為前后兩段,通常把前段采樣點稱為早門,后段采樣點稱為遲門,分別對早門信號和遲門信號做快速傅里葉變換運算,比較前后兩段頻譜能量值計算出誤差估計,即可判斷出是否同步、超前或者滯后[5-6]。然后根據(jù)早門和遲門能量的差別量調(diào)整步數(shù),改變跳信號窗口,直至能量差小于判決門限,即完成了跳沿同步,如圖1所示。

圖1 基于多個FFT的早遲窗同步方法原理框圖

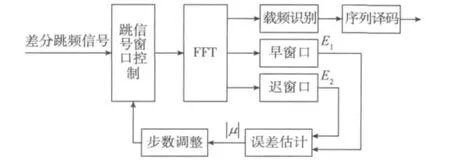

但是FFT在實際工程中占用很大的硬件資源,特別是當(dāng)系統(tǒng)要求同步精度很高的時候,F(xiàn)FT需要提高點數(shù)來提高精度,從而導(dǎo)致硬件乘法器和加法器成倍增加。如圖1所示,傳統(tǒng)差分跳頻采用了3個FFT,其中早窗口和遲窗口后各采用1個FFT來計算早遲窗能量值,最后1個FFT計算出的頻譜能量值直接送到載頻識別器來進(jìn)行頻率序列譯碼。如果能夠把3個FFT結(jié)合成1個FFT,則能有效地節(jié)省硬件資源。因此核心是把早遲窗移到FFT變換后的頻域里進(jìn)行加窗處理,通過FFT變換后加窗提取早遲窗,如圖2所示。

圖2 基于單個FFT的早遲窗同步方法原理框圖

圖2采用把FFT前移到跳信號窗口控制后,其中FFT采用N點,就是每隔N個采樣點進(jìn)行一個FFT變換,取得頻譜信息后,分成3路。前2路根據(jù)FFT輸出標(biāo)號xk_index和對應(yīng)的頻譜能量值E,把早窗口和遲窗口頻譜信息分別提取出來,最后送入誤差估計來調(diào)整步數(shù)控制跳信號窗口移動。第3路把頻譜信息送入載頻識別,進(jìn)行維特比譯碼。這樣就能只采用一個FFT運算來完成早遲窗同步,有效地節(jié)省硬件資源。

1.2 非線性早遲窗同步鎖定原理

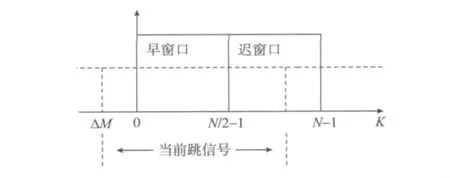

早遲窗計算方法為基本的DFH同步鎖定方法,利用連續(xù)若干跳的早窗口FFT能量、遲窗口FFT能量來計算窗口誤差,通過和最小門限δ比較,來控制跳信號窗口控制器來移動跳信號控制窗口。

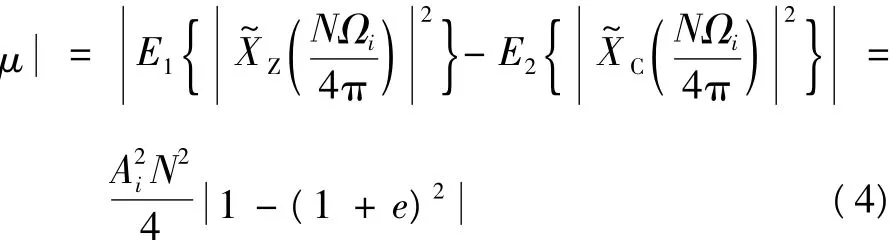

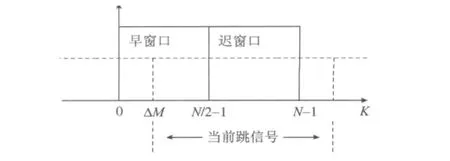

圖3為跳信號控制窗口遲于當(dāng)前跳情況。實線是長度各為N/2個采樣點的早窗和遲窗,其中一跳的長度為N個采樣點。

圖3 檢測跳窗口遲于當(dāng)前跳

圖3中,ΔM為檢測窗口和當(dāng)前跳的時間誤差,通過求N/2點FFT,得出能量差值。歸一化時間誤差為

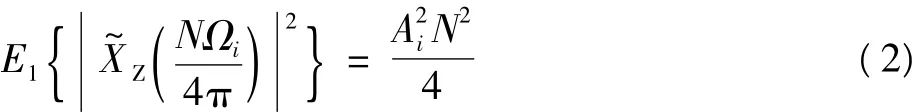

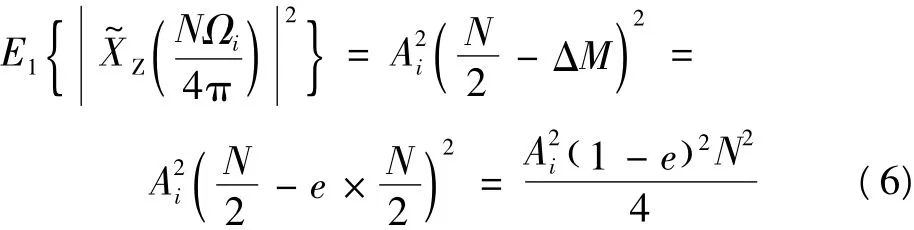

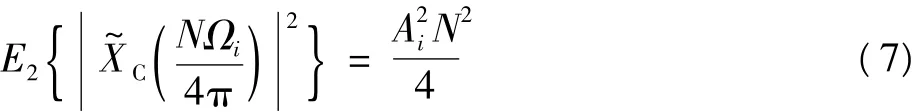

對于早窗口,N/2點FFT后的能量值為

式中,Ai為當(dāng)前跳信號的能量幅度。

對于遲窗口,N/2點FFT后的能量值為

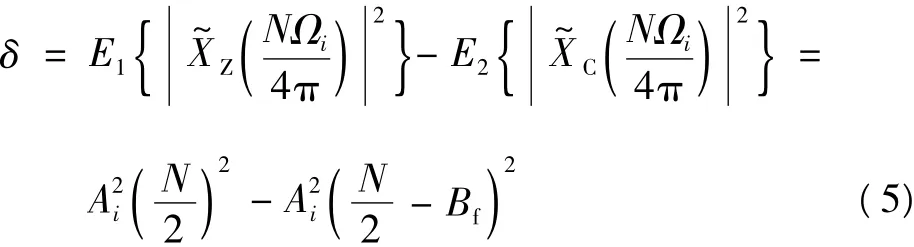

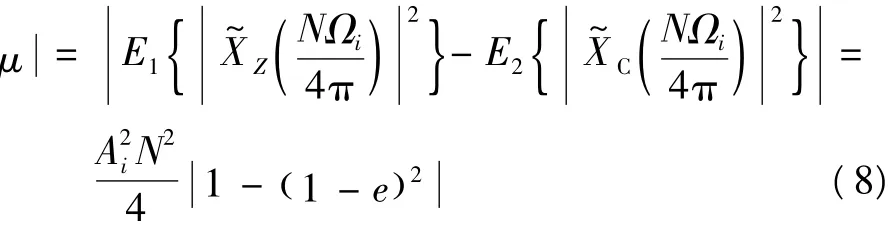

即早窗和遲窗能量差值為

當(dāng)調(diào)整最小步數(shù)為Bf=16時,設(shè)最小門限δ為

即早遲窗的精度為Bf=16,誤差為跳沿前后16個采樣點以內(nèi)。當(dāng)然Bf越小,同步精度越高。

圖4為跳信號控制窗口早于當(dāng)前跳情況。實線是長度各為N/2個采樣點的早窗和遲窗,其中一跳的長度為N個采樣點。

圖4 檢測跳窗口早于當(dāng)前跳

對于早窗口,N/2點FFT后的能量值為

式中,Ai為當(dāng)前跳信號的幅度。

對于遲窗口,N/2點FFT后的能量值為

即早窗和遲窗能量差值為

同理當(dāng)調(diào)整最小步數(shù)為Bf=16時,設(shè)最小門限δ為

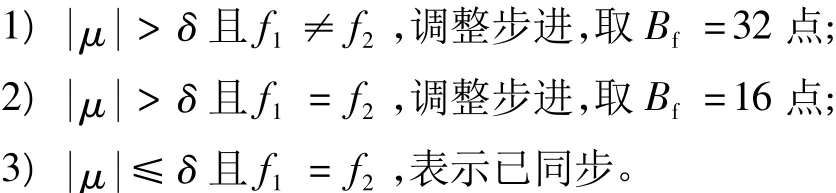

根據(jù)式(1)~(9)的分析,本文FFT點數(shù)N=1 024,粗調(diào)移動32點,細(xì)調(diào)移動16點,跳沿誤差不超過1.5%。同時采用非線性跳沿調(diào)整,當(dāng)早遲窗跟當(dāng)前跳沿時間誤差相差過大時,采用粗調(diào),當(dāng)時間誤差縮小時改用細(xì)調(diào)。f1,f2分別表示早遲窗FFT識別的跳頻頻率序列,判斷情況如下所示:

2 建模設(shè)計與仿真驗證

通過采用Xilinx公司的System Generator工具進(jìn)行建模設(shè)計仿真,仿真無誤后,生成相應(yīng)的Verilog代碼,在Spartan6開發(fā)板完成實際跳頻通信。

2.1 快速傅里葉變換(FFT)建模與仿真

System Generator函數(shù)庫里提供了現(xiàn)成的FFT模型可供調(diào)用,如圖5所示。采用512點FFT,其start腳表征FFT變換的起始時刻,上升沿有效,若此沿與接收跳頻信號的起始時刻一致,則表明跳信號窗口已同步,同步正是根據(jù)跳沿時刻起始位置一致來判斷。此外,本文差分跳頻子系統(tǒng)的采樣率為7.68 Msample/s(兆采樣/秒),碼元速率為2.5 kbit/s,即一個碼元寬度采樣點數(shù)為7.68×1 000/2.5=3 072。則一個碼元寬度做6次FFT變換,頻率分辨率為7.68×1 000/512=15 kHz,而信道間隔為45 kHz,引入30 kHz的冗余,即便信號有較小的頻偏,系統(tǒng)也能做出正確的判決。

圖5 快速傅里葉變換(FFT)建模(截圖)

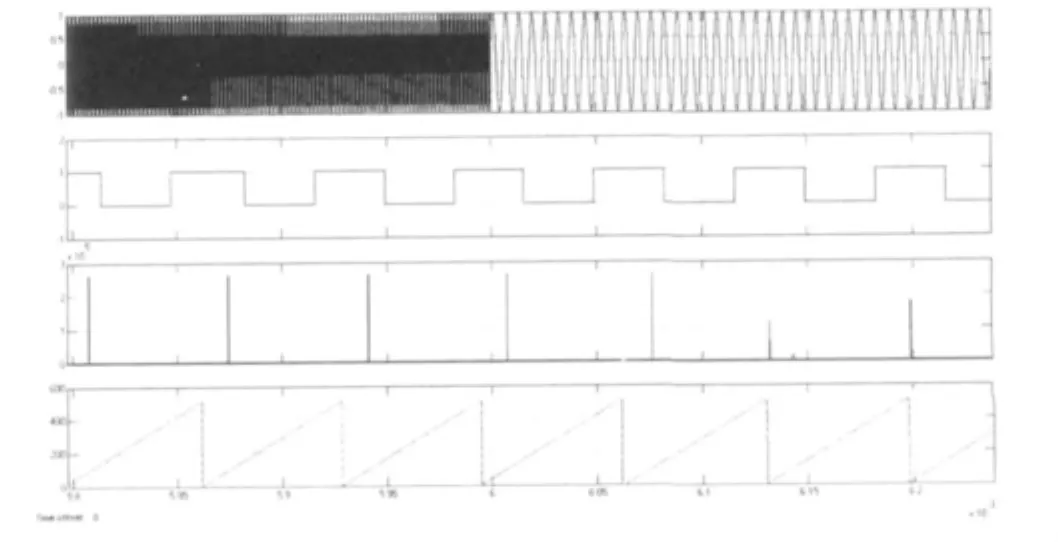

如圖6所示仿真結(jié)果,自上向下第1路信號為差分跳頻發(fā)射信號;第2路為FFT的start腳同步信號;第3路為FFT輸出的經(jīng)過mode模塊實部虛部平方求和得到的頻譜能量值;第4路為輸出能量與之對應(yīng)的頻率標(biāo)號xk_index。第3路和第4路合起來就是輸入信號的頻譜分析圖。差分跳頻接收機正是通過FFT分析輸入信號頻譜找出每一跳的頻率成分,從而解跳出原始信息。另外從圖中可以看出,F(xiàn)FT的start腳并沒有跳沿同步,從而導(dǎo)致頻譜能量出現(xiàn)兩個能量值,且能量幅度大大減少,嚴(yán)重影響后續(xù)載頻識別。

圖6 快速傅里葉變換(FFT)仿真波形(截圖)

2.2 早遲窗提取建模與仿真

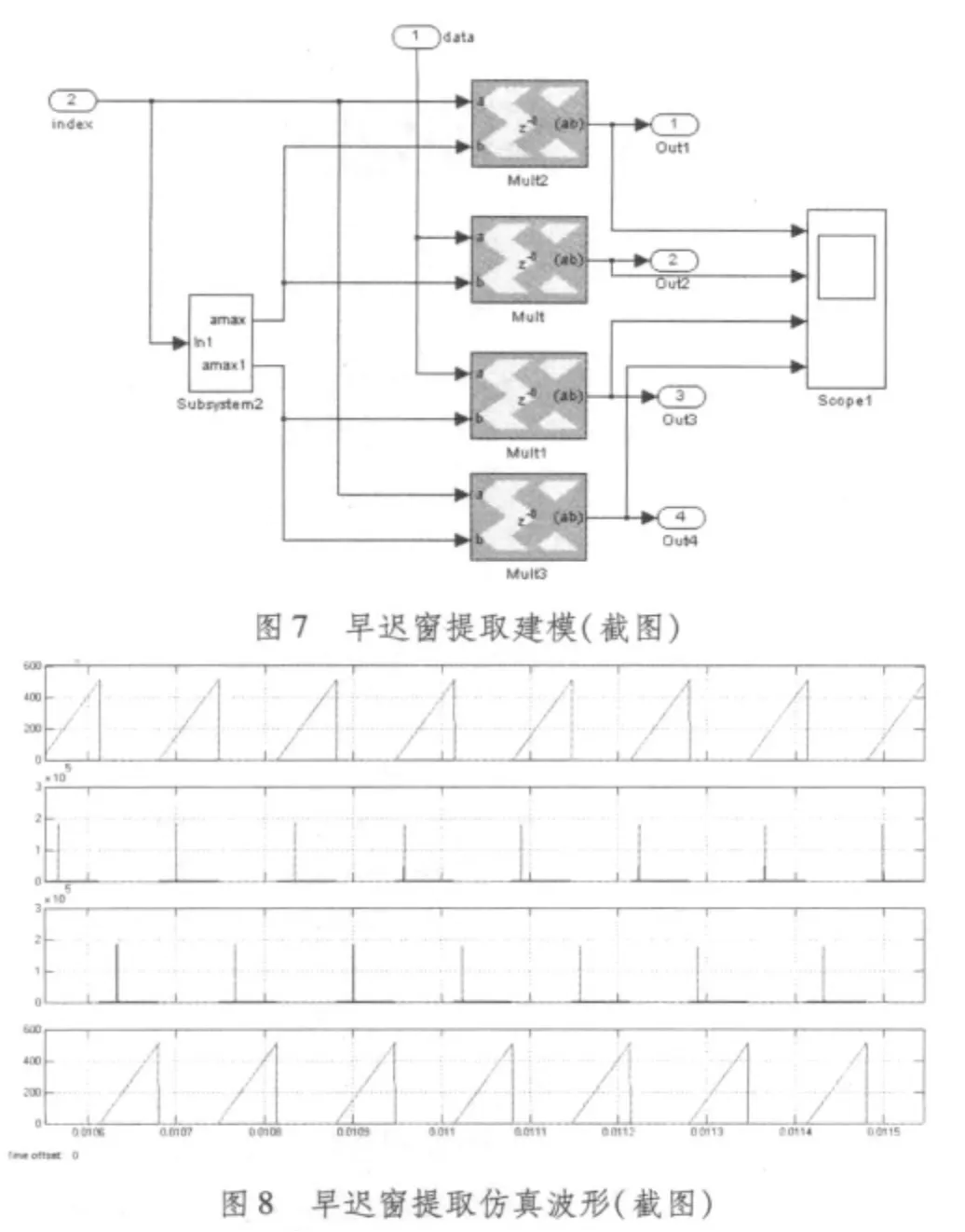

此模塊功能是通過對FFT的輸出xk_index標(biāo)號(圖6第4路)提取前后早遲窗的能量值和標(biāo)號值。由于一個碼元寬度做6次FFT變換,即一個碼元寬度可分別提取3個早窗口和3個遲窗口。如圖7所示。

如圖8所示仿真結(jié)果,自上向下第1路信號為早窗輸出xk_index標(biāo)號;第2路為早窗輸出能量值;第3路為遲窗輸出xk_index標(biāo)號;第4路為遲窗輸出能量值。采用1個FFT模塊,大大降低了資源消耗。

2.3 單個FFT非線性早遲窗同步整體建模與仿真

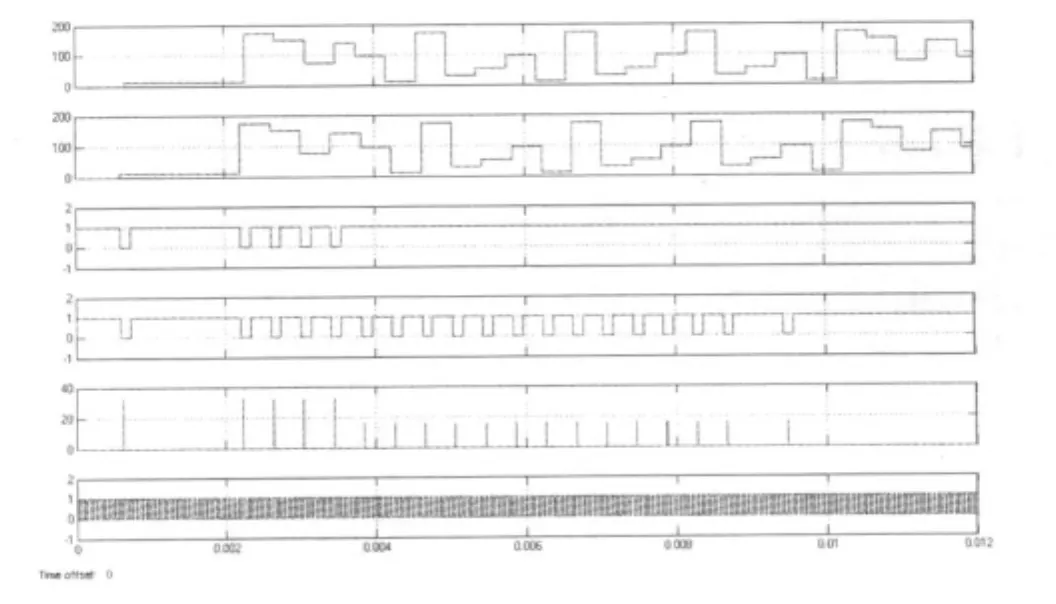

早遲窗同步的整體模型如圖9所示,工作流程為:早遲窗同步電路接收下變頻后的兩路正交信號,步數(shù)調(diào)整模塊內(nèi)部方波信號送入FFT模塊的start腳,將512點FFT分別提取出來作為早窗和遲窗。搜索模塊根據(jù)運算值搜尋出早窗和遲窗信號的最大能量值及對應(yīng)的頻率號后,誤差估計模塊根據(jù)這些值做出判斷,輸出步數(shù)調(diào)整信號,步數(shù)調(diào)整模塊接收步數(shù)調(diào)整信號,調(diào)整內(nèi)部方波前后調(diào)整,直到跳沿對齊。

圖9 早遲窗同步整體建模(截圖)

圖10 早遲窗同步整體仿真波形(截圖)

3 小結(jié)

本文采用軟件無線電結(jié)構(gòu),針對現(xiàn)有差分跳頻早遲窗的缺點,采用基于單個FFT的非線性早遲窗同步系統(tǒng),大大降低了資源消耗,同時滿足同步系統(tǒng)鎖定時間和鎖定精度,更加適應(yīng)實際應(yīng)用。通過仿真驗證了同步系統(tǒng)的性能。由于整個系統(tǒng)采用FPGA軟件可編程技術(shù),能夠根據(jù)實際情況靈活地調(diào)整參數(shù),以適應(yīng)各種復(fù)雜干擾環(huán)境。

:

[1]宋培林,沈保鎖.差分跳頻的解調(diào)窗口同步算法[J].電子技術(shù)應(yīng)用,2004(9):43-45.

[2]陳智.差分跳頻通信系統(tǒng)的性能分析[D].成都:電子科技大學(xué),2006.

[3]李勇,姚富強.基于FFT的DFH系統(tǒng)跳信號窗口同步方法研究[C]//2006軍事電子信息學(xué)術(shù)會議論文集.武漢:中國電子學(xué)會,2006:462-465.

[4]楊小牛,樓才義,徐建良.軟件無線電原理與應(yīng)用[M].北京:電子工業(yè)出版社,2001.

[5]李少謙,董彬虹,陳智.差分跳頻通信原理及應(yīng)用[M].成都:電子科技大學(xué)出版社,2007.

[6]潘武,周世東,姚彥.差分跳頻通信系統(tǒng)性能分析[J].電子學(xué)報,1999(S1):102-104.