一種基于FPGA的DDS信號發生器的設計*

龔光松

(咸寧職業技術學院,湖北 咸寧 437100)

一種基于FPGA的DDS信號發生器的設計*

龔光松

(咸寧職業技術學院,湖北 咸寧 437100)

隨著可編程邏輯器件的不斷發展,利用DDS技術原理在FPGA平臺上開發高性能的多種波形信號發生器與基于DDS芯片的信號發生器相比,具有成本低、在線更新、硬件開發軟件化、操作靈活等優點.本文介紹了一種基于FPGA的DDS函數信號發生器設計,實現了輸出100Hz~1MHz的正弦波、方波、三角波,頻率設置等功能,具有一定的實用價值.

FPGA;DDS;Quartus II 9.0

1 DDS基本原理

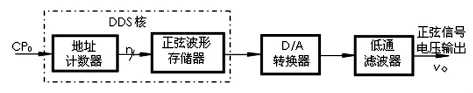

DDS技術產生波形的過程是:基于奈奎斯特(Nyquist)抽樣定理對需要產生的波形進行采樣,經量化后存入存儲器(例如,ROM)中作為待產生信號波形的數據表;在需要輸出波形時,從數據表中依次讀出數據,產生數字化的信號,這個信號再通過D/A轉換器和濾波器后就變成了所需的模擬信號波形.如果改變數據表中的內容,就可以得到不同的信號波形.

DDS技術產生波形的原理框圖

2 DDS的FPGA實現方案

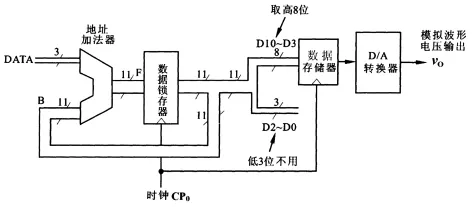

以FPGA平臺為核心,將各波形的幅值/相位量化數據存儲在ROM內,按照設定頻率,以相應頻率控制字DATA為步進,對相位進行累加,以累加相位值作為地址碼讀取存放在存儲器內的波形數據,經D/A轉換和幅度控制、濾波即可得到所需波形.系統總體設計方框圖如圖所示.

DDS實現框圖

在FPGA中,地址計數器由地址加法器和并行數據鎖存器組成.加法器有兩個數據輸入端:一個輸入端B與數據鎖存器的輸出相連;另一個輸入端為相位增量DATA,又因為DATA是決定DDS輸出頻率的參量,因而又被稱為頻率控制字,存放DATA的寄存器被稱為頻率控制寄存器.電路工作原理如下:在頻率數據DATA的控制下,地址加法器的輸出結果為DATA+B,因此,在時鐘CP0的作用下,數據鎖存器的輸出數據D10~D0每次將增加DA TA.也就是說,DATA控制了地址加法器輸出的遞增速率.此例中,DA TA最小值為1,最大為值7(23-1).在時鐘CP0不變的情況下,DATA的大小控制著D10~D0從最小值變到最大值所用的時間.DATA大,每次相加運算得到的結果就大,即數據存儲器的地址增長快,地址循環一周(從D10~D0最小值0到最大值211-1)所需時間就短.由于數據存儲器每經過一個循環就會輸出一個離散的正弦波數據,所以經過D/A轉換器后,輸出的波形頻率就高,反之則頻率就越低.為保證輸出數據的精度,將數據D10~D0分為兩部分:高8位D10~D3與波形數據存儲器相連,低3位 D2~D0不用,這樣,D10~D3的數據不會大于1,從而能夠順序地從數據存儲器讀取數據.

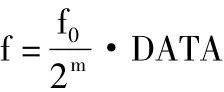

改變DATA的值就能改變輸出信號的頻率,數據存儲器中的全部數據被讀出一次的頻率為:

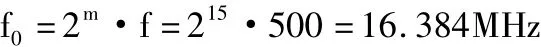

輸出信號頻率與頻率控制字成正比.根據采樣定理,所產生的信號頻率不能超過系統時鐘頻率的1/2.為了保證信號的輸出質量,輸出信號的頻率不能高于時鐘頻率的33%.例如,在地址加法器數據位寬為m=15的情況下,欲得到一個步長為500Hz的波形,則時鐘頻率f0為:

3 系統設計

3.1 系統參數設計

要輸出比較好的正弦波形,理論上正弦波ROM里的一個周期點的數量越多越好.經過時序仿真,ROM中128或少于128個點仿真出來的波形都不太好.這里假設在ROM里取256個點.根據頻率計算公式,要得到1MHz的波形,為了讓ROM中每一個點都被讀到,則n=8,所以f0/256=1MHz,由此系統時鐘f0要大于等于256MHz.過高的頻率可能會使電路板工作不穩定.因此,選擇DE2能穩定工作的150MHz時鐘作為系統時鐘.又要達到步長小于等于100Hz,所以m大于等于21,取m=32.由于達不到256MHz以上,因此ROM中不可避免的有一些點沒有讀到,此時應盡量將ROM中的點數取大.經過仿真測試,1 024個點時得到的波形最好.綜上,取系統時鐘為150MHz,m=32,DATA為25位,ROM中點為1 024個.

3.2 各模塊設計

3.2.1 建立正弦波形存儲器ROM

在使用QuartusII進行開發時,正弦波形存儲器可以調用LPM_ROM模塊來實現.為了對ROM模塊內的數據進行加載首先應建立相應的*mif(Memory Initial File)文件.它可以用C語言(或者Matlab)編寫源程序,描述正弦方程式,然后生成.mif文件.

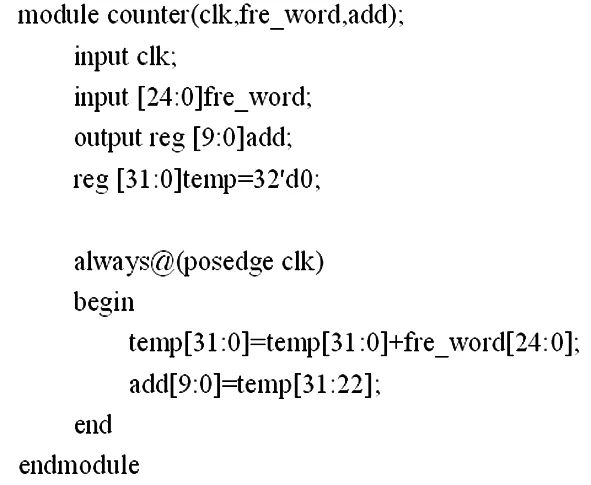

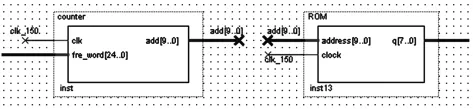

3.2.2 相位累加器和數據鎖存器設計

相位累加器是DDS系統設計的核心,它決定著頻率的范圍和分辨率.本設計采用的是32位的二進制累加器和寄存器,其中累加器與寄存器在同一個模塊中,并去鎖存數據的高十位作為查表的地址值.Clk為系統時鐘,fre_word為輸入32位的頻率控制字,address為輸出后取十位的地址值.

相位累加器和正弦波模塊如下:

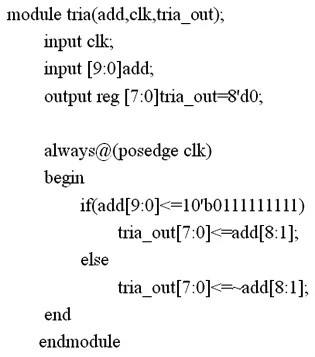

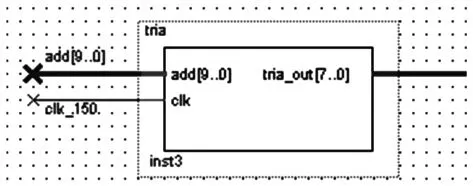

3.2.3 三角波的設計

三角波的生成原理,對輸入地址address的值進行判斷,當其最高位為0時,取地址的中間八位為輸出值,當其最高位為1時,將中間八位取反后輸入.

三角波模塊如下:

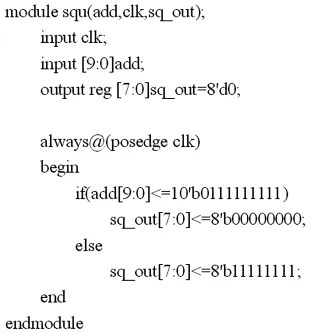

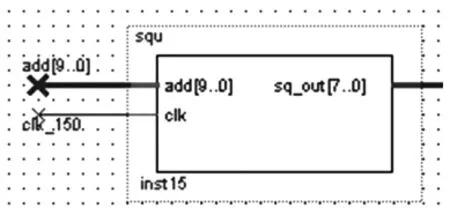

3.2.4 方波的設計

其原理如下,當地址數據的最高位為0時,輸出為最大幅值為255.當地址數據的最高位為1時,輸出為最低幅值0.

方波模塊如下:

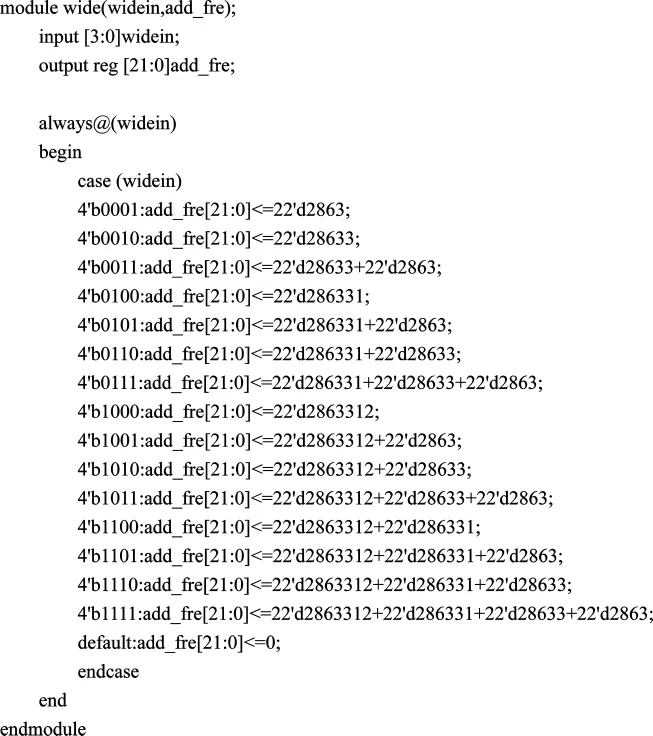

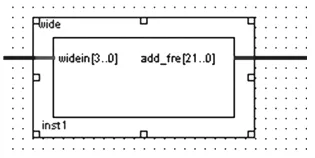

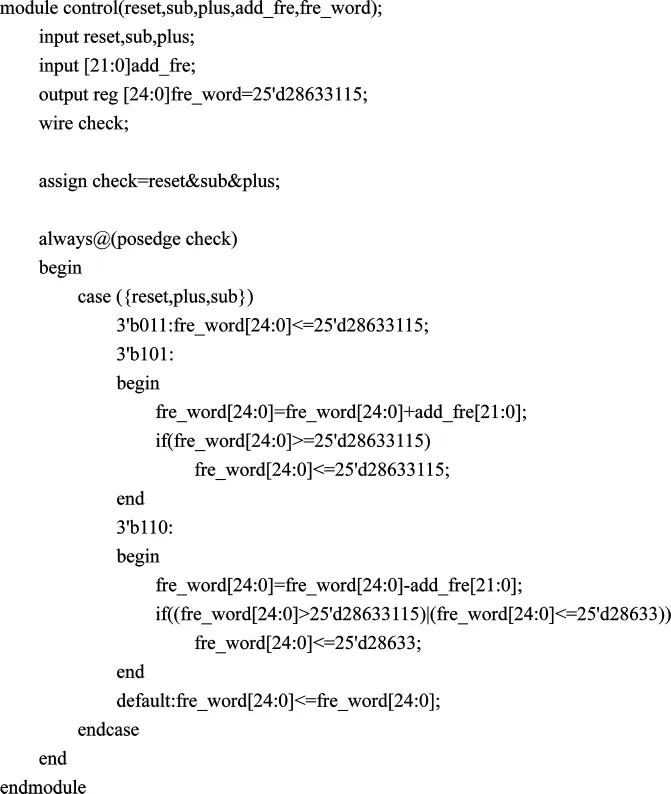

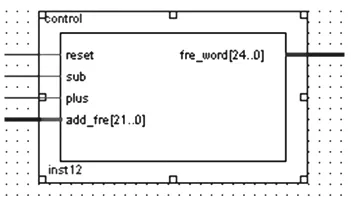

3.2.5 調整頻率模塊設計

更改頻率實質上就是改變頻率控制字的值.設計中采用四個撥碼開關控制調整頻率的檔位,另三個按鍵分別控制reset(頻率回到初始狀態的1MHZ),plus(加頻率),sub(減頻率).采用兩個模塊設計,頻率檔位模塊和頻率調整模塊.根據頻率計算公式,步進值為100Hz、1KHz、10KHz、100KHz時頻率控制字的改變量分別為 2 863、28 633、286 331、2 863 312,初始1MHz時頻率控制字為28 633 115檔位模塊設計如下:

頻率調整模塊設計如下:

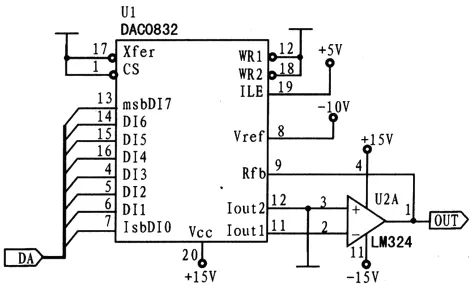

3.2.6 D/A 轉換電路

數據轉換器輸出的數據是數字形式的電壓值,為實現數字電壓值與模擬電壓值之間的轉換,系統還專門設計D/A轉換電路,其D/A轉換電路原理圖如圖所示.

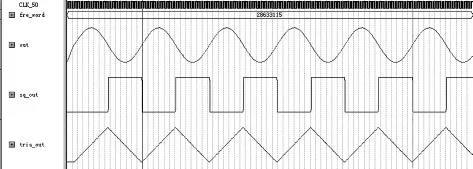

4 結果驗證

仿真結果:

用示波器觀察波形,在200KHz觀察到的各種波形沒有明顯失真,能夠正常通過按鍵切換波形和調整頻率.觀察結果表明,該系統輸出的各種波形穩定,與設計要求一致.

5總結

本文在DDS工作原理的基礎上,介紹基于FPGA實現DDS的設計方案,從測試結果可看出,該系統工作穩定,并具有一定的實用價值.

[1]Van Putten,Middeiheok S.Integrated silicon anemometer[J].Eiectronic Letters,1974,(10).

[2]閻石.數字電子技術基礎(第四版)[M].北京:高等教育出版社,1998.

[3]田良.綜合電子設計與實踐[M].南京:東南大學出版社,2002.

[4]毛敏,鄭珍,周渭.基于DDS的低通濾波器的設計與實現[J].電子技術,2006,(3):17 ~20.

TP33

A

1006-5342(2012)06-0037-03

2012-03-05