基于可編程邏輯器件的彈載存儲測試儀

王永芳,范錦彪,王 燕

(1.中北大學電子測試技術國家重點實驗室,山西 太原 030051;2.儀器科學與動態測試教育部重點實驗室,山西 太原 030051)

0 引言

彈載存儲測試是在被測裝置體內置微型存儲測試儀,對被測裝置無影響或影響在允許范圍的條件下,現場實時完成信息采集與存儲,事后回收測試,由計算機處理和再現被測信息的一種動態測試技術[1]。

高性能火炮發射時的高膛壓、高初速使記錄儀中電路模塊的抗沖擊能力成為測試能否成功的關鍵,而慣性短時飛行的特點要求信號采樣頻率高,記錄時間短。雖然各種測試裝置經過處理后均能滿足抗高過載的要求,但是因為單片機容易跑飛[2],很難實現對被測信號的高速采樣與存儲;專用集成芯片ASIC功能固定,需添加電路模塊,進而會造成硬件體積偏大,增大整個系統的體積[3]。為此,本文提出了基于CPLD的可編程彈載姿態存儲測試儀。

1 基于單片機的存儲測試儀與CPLD

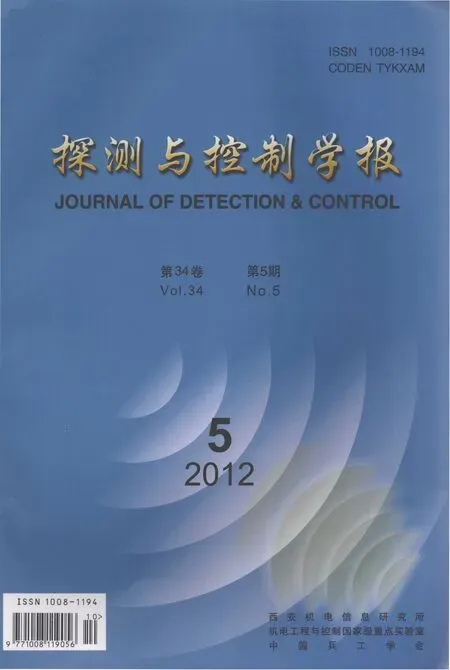

測試儀的區別主要在于主控芯片實現上的不同,主控芯片的功能是對整個電路的電源管理及電路各個模塊的時序控制和與計算機通信模塊。主控芯片目前主要有單片機、ASIC和CPLD。但本實驗室自主研發的專用集成芯片HB0202,開發周期長,成本高,功能固定,不能更改,應用時經常需要額外增加電路部分,會增加系統體積,并且由于國內制作工藝的問題,有時會出現功能不穩定的情況。基于單片機的存儲測試儀的軟件流程圖如圖1所示。

圖1 單片機存儲測試儀軟件流程圖Fig.1 Software flow chart of MCU memory tester

單片機作用在有較強電磁干擾或惡劣的環境下,雖然在設計時可能針對特定環境采取了一些保護措施,諸如外殼屏蔽、電磁隔離等方法,但還是較難徹底解決程序運行中可能產生的跑飛現象,達不到要求。并且,單片機因為外設所限,一般幾個到十幾個脈沖輸出口,往往需要多片單片機來實現。

單片機是執行代碼的器件,代碼只能逐句運行,限制其最大采樣頻率的“瓶頸”在于寫數據到FLASH中的速度,在數據轉換、傳輸和寫入的采樣過程中,寫入占據了大部分的采樣時間。

目前的存儲測試儀主要為單次性單變采樣,功能固定,難以擴展,不能適應多條件的測試要求。CPLD芯片具有集成度高、速度快、可自定義其功能及其可重復編程和反復擦寫等優點[4]。并且彈載存儲測試在不同條件下,尤其是在研發階段需要測試裝置在不同采樣頻率下的數據。而CPLD芯片為復雜可編程邏輯器件,集成度高,可反復擦寫上千次,使用靈活。CPLD是邏輯陣列,I/O口均可以作為脈沖輸出口,里面有很多基本的邏輯單元可以方便地實現計數、分頻等功能,且芯片性能穩定,具有很高的抗沖擊性能,并且與沖擊方向無關[5]。同時CPLD管腳之間的延遲時間為納秒級,且內部程序為并行執行,相對于程序順序執行的單片機來說,在處理速度上有絕對的優勢,可處理高達幾十兆赫茲的采樣信號。因此,CPLD芯片應用于彈載存儲測試具有明顯的優勢。

2 基于CPLD的存儲測試儀

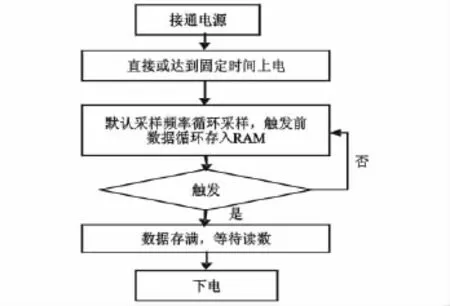

本文提出的彈載存儲測試儀增加了上電前的編程設計,通過計算機發送編程指令到裝置,編程軟件為Visual Basic6.0,界面如圖2所示。測試儀可以根據實際情況設定信號采樣頻率和存儲器容量,同時增加了是否防誤上電及負延遲時間選擇,還可根據實際情況設置默認值,通過設計CPLD芯片的邏輯設定常用的值為默認值,省去每次測試編程的步驟。

圖2 測試儀編程界面Fig.2 Programming interface of the test

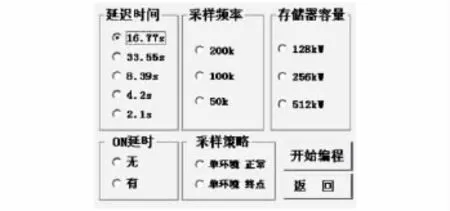

本文實現的CPLD存儲測試儀可以實現高達200kHz的采樣頻率,同時還具有防誤上電、采樣頻率可選、負延遲容量可選的功能,整體流程圖如圖3所示。

2.1 防誤上電原理

CPLD的龐大的邏輯陣列可以輕松地實現計數器和觸發器,可以通過編程設定上電延遲時間,外部一上電觸發計數器根據外部提供的時鐘信號開始計時,若上電持續時間達到設定時間則完成上電操作,否則系統仍然處于休眠狀態。本測試儀針對不同的實驗環境,防誤上電時間設計了5種:2.1s、4.2s、8.4s、16.77s、33.55s。

圖3 CPLD存儲測試儀軟件流程圖Fig.3 Software flow chart of CPLD memory tester

2.2 采樣頻率選擇原理

測試儀的AD轉換芯片采用的是Analog Devices公司的芯片AD7472,轉換精度為12bit,信噪比高,轉換時間為880ns,處理能力為1.5MSPS,AD7472在CONVST的時鐘的下降沿開始轉換,因此AD的轉換頻率是由CONVST決定的。而CPLD內部的程序都是并行運行的,運行時間為納秒級,因此可以輕松實現高速率采樣。只要通過CPLD編程設定內部計數器和觸發器的觸發條件即可將提供的時鐘信號進行分頻得到相應頻率的CONVST信號。因被測炮彈在空中飛行的時間為十幾秒,故測試儀根據精度的不同信號采樣頻率有三種:50kHz、100kHz和200kHz。

2.3 負延遲容量選擇原理

測試儀的存儲總容量512K×12bit,存儲器的存儲數據的地址信號是由CPLD產生的,因此若要實現不同的負延遲容量只要改變內部程序中的觸發后產生的地址信號個數即可。測試儀上電開始采樣后,存儲器將采樣數據循環存入存儲器中,地址信號隨著數據的存入依次加1,當觸發信號到來時,測試電路觸發,進入負延遲工作狀態,即計數器計數達到設定個數后停止采樣,最后一位地址信號存入地址計數器,等待數據讀出,隨后計算機讀出測試數據,地址信號依次加1,當計算機讀完規定長度的數據后,地址計數器又回到凝固態。根據有效數據在前或在后,信號的采樣策略分為兩種:一種負延遲為128K×12bit(有效數據在后),一種為負延遲為384K×12bit(有效數據在前)。

3 實驗驗證

主控芯片采用可抗高過載的芯片XCR3064XL,經實驗證明可以承受30 000 g的過載。根據應用場合的設備承受的沖擊過載范圍,用環氧樹脂對裝置進行真空灌封處理,設計了抗沖擊機械殼體,將電路固結在保護殼中以抗高過載。經過上述處理,測試儀能夠承受高達10 000 g的過載。測試儀尺寸小,僅為Φ30×60mm。

本存儲測試儀功耗低,休眠狀態電流為0.2 μA,待觸發態電流為5.6mA,觸發后電流變為12 mA,采樣完畢后電流僅為0.42mA。

為了驗證該測試儀的性能和精度,進行了大量的實驗室靜態測試。將測試儀在三維無磁性轉臺上進行飛行體運動的模擬實驗,試驗結束后將轉臺閃存數據與測試儀的數據進行比較,計算出測量誤差,進而驗證測試儀的可靠性。

考核所使用的無磁性轉臺全部由木質和鋁質材料改造而成,可實現自轉、俯仰、偏航的三維運動,模擬彈體飛行。頻率調節范圍:0~60Hz。俯仰角度、偏航角度范圍±180°。轉臺使用靈敏度高的脈沖碼盤,對俯仰、偏航的輸出角度值將精確到0.1°,縮小了因轉臺精度低引起的誤差,提高了測量精度[6]。

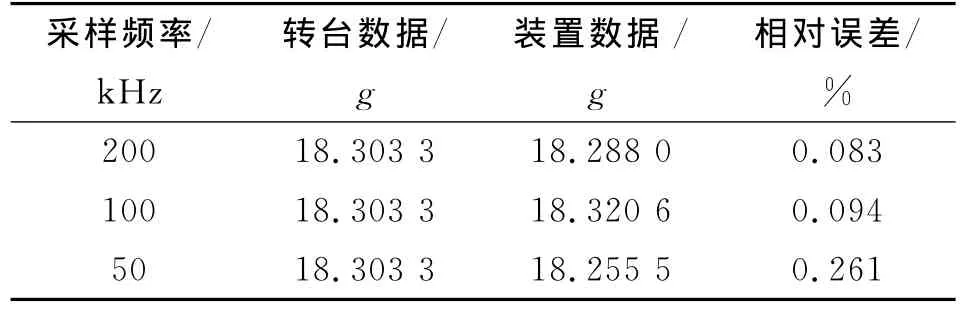

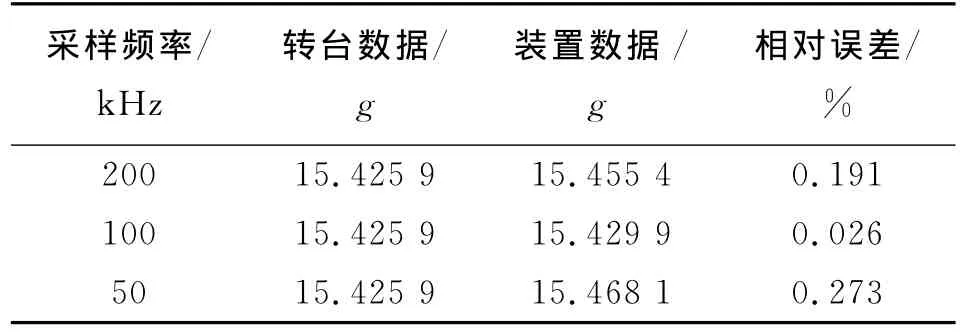

加速度考核方法采用離心加速度的方法,先測量好裝置安裝半徑r,然后設定轉速,設定裝置采樣頻率,實驗結束后將轉臺測試結果根據a=w2×r,計算出加速度值與測試儀的數據進行比較。測試結果如表1和表2所示。

表1 X軸加速度精度考核數據表Tab.1 X-axis acceleration data accuracy assessment table

表2 Y軸加速度精度考核數據表Tab.2 Y -axis acceleration data accuracy assessment table

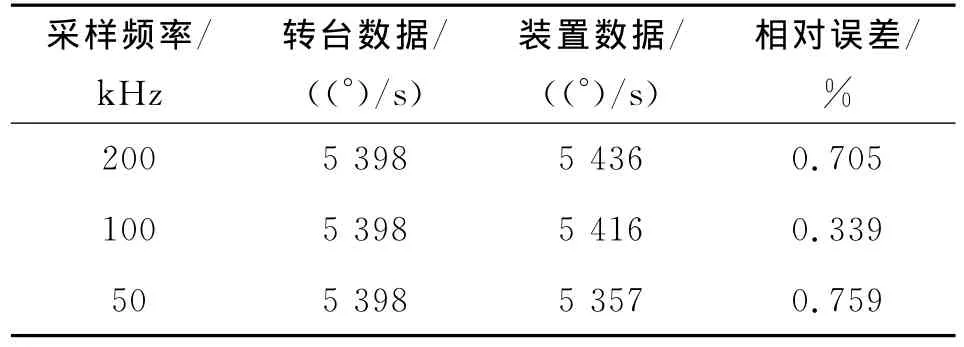

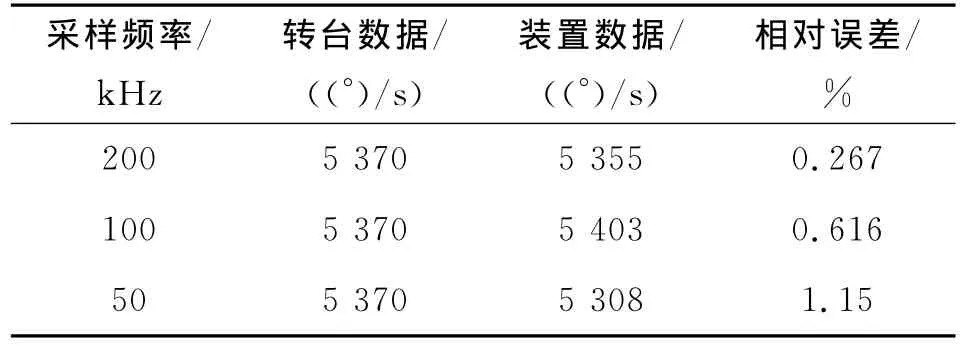

角速度考核方法為預先設定轉臺轉速,裝置預先編程設定不同的采樣頻率,測試結束后根據讀數軟件讀出值,與轉臺閃存讀出數據進行比較。測試結果如表3和表4所示。

表3 Y軸角速度精度考核表Tab.3 Y -axis angular velocity accuracy assessment table

表4 Z軸角速度考核精度表Tab.4 Z-axis angular velocity accuracy assessment table

經計算不同采樣頻率下測試結果基本一致,角速度絕對誤差最大值為1.15%,誤差主要來源于測量誤差。加速度絕對誤差最大值為0.27%,誤差主要來源于為測量誤差,誤差大小達到測試要求,測試結果與轉臺數據得到很好的吻合。

4 結論

本文提出了基于復雜可編程器件的彈載存儲測試儀。測試儀采用可反復擦寫的CPLD芯片作為主控芯片,利用其內部豐富的邏輯單元實現了可高速采樣且使用靈活的存儲測試方案,設計通過休眠防止誤上電;通過并行實現高速率采樣,通過分頻實現50kHz、100kHz和200kHz三種頻率可選;通過計數實現8K×12bit、448K×12bit負延遲可選。測試儀具有抗高過載,穩定可靠,低功耗,尺寸小,成本低等優點,適用于彈載存儲測試。同時測試儀的電路部分使用靈活,適用性好,還可應用于其他短時間的動態測試。

[1]李紅旗,李東光,李世義.基于CPLD的彈載高速存儲測試系統關鍵技術研究[J].彈箭與制導學報,2007(1):360-362.LI Hongqi,LI Dongguang,LI Shiyi.The key technology study based on the high-speed storage measurement and test system attached to bullets[J].Journal of Projectiles,Rockets,Missiles and Guidance,2007(1):360-362.

[2]李海燕.單片機測控系統的抗干擾技術[J].船電技術,2005(6):30-33.LI Haiyan.Anti-interference technology of measurement and control system within single-chip computer[J].Marine Electric & Electronic Engineering,2005(6):30-33.

[3]朱仕永,祖靜,范錦彪.基于CPLD的彈載加速度存儲測試儀[J].探測與控制學報,2009,31(3):43-45 ZHU Shiyong,ZU Jing,FAN Jinbiao.Missile-borne storage measurement and test instrument of acceleration based on CPLD[J].Journal of detection &control,2009,31(3):43-45.

[4]郭紅英,祖靜.存儲測試專用集成電路成測試研究[D].太原:中北大學,2007.

[5]徐鵬,祖靜,李樂.CPLD芯片抗高g值沖擊性能分析[J].振動與沖擊,2007,26(1):148-150.XU Peng,ZU Jing,LI Le.Performance analysis of the impact of resistance to high gvalue of the CPLD chip[J].Journal of Vibration and Shock,2007,26(1):148-150.

[6]段精婧,馬鐵華,范錦彪.基于無陀螺捷聯慣導系統的四元數算法[J].探測與控制學報.2010,32(1):15-18.DUAN Jingjing,MA Tiehua,FAN Jinbiao.Quaternion arithmetic of projectile based on GFIMU[J].Journal of detection &control,2010,32(1):15-18.