艦載雷達(dá)環(huán)境下CFAR模塊的設(shè)計(jì)與實(shí)現(xiàn)

劉 魁 顏學(xué)龍 楊龍平 高希光 趙志強(qiáng)

(桂林電子科技大學(xué)電子工程學(xué)院1,廣西 桂林 541004;桂林長(zhǎng)海發(fā)展有限公司技術(shù)中心2,廣西 桂林 541001)

0 引言

艦載雷達(dá)主要面臨海雜波、云雨等氣象雜波以及港口、錨地、船只等強(qiáng)反射體的復(fù)雜環(huán)境。此環(huán)境嚴(yán)重干擾雷達(dá)的正常工作,使得雷達(dá)在作戰(zhàn)中長(zhǎng)期受到制約[1]。對(duì)寬動(dòng)態(tài)范圍非高斯分布的海雜波和海上氣象雜波進(jìn)行對(duì)消處理后會(huì)出現(xiàn)剩余雜波,從而降低了動(dòng)目標(biāo)顯示(moving target indication,MTI)等處理的性能[2]。因此,為降低虛警率,減少對(duì)自動(dòng)檢測(cè)的影響,在系統(tǒng)設(shè)計(jì)時(shí),必須設(shè)法提高海環(huán)境下目標(biāo)的信噪比、降低海環(huán)境下檢測(cè)的虛警率。

恒虛警處理(constant false alarm rate,CFAR)是一種用來(lái)保持恒定虛警概率的數(shù)字信號(hào)處理算法,它可以避免噪聲背景雜波和干擾變化帶來(lái)的影響。因此,從實(shí)際工程需求出發(fā),對(duì)非高斯雜波背景下CFAR檢測(cè)方法進(jìn)行了研究,給出了該方法研究的分析過(guò)程,同時(shí)對(duì)研究的結(jié)果進(jìn)行了仿真與工程驗(yàn)證。

1 CFAR算法模型

由于同一個(gè)單元的干擾功率電平是變化的,因此,為設(shè)定檢測(cè)單元所需的門(mén)限電平,必須通過(guò)鄰近單元的數(shù)據(jù)估計(jì)來(lái)得到待檢單元的干擾雜波統(tǒng)計(jì)特性。此方法基于均勻干擾或僅存在干擾噪聲的假設(shè)條件,可以利用周圍鄰近單元的數(shù)據(jù)值,對(duì)待檢單元平均干擾功率進(jìn)行估算,從而實(shí)現(xiàn)CFAR處理。

CFAR檢測(cè)閾值主要由以下四部分組成[3-4]:①固定閾值、②外部干擾的平均幅度、③干擾統(tǒng)計(jì)分布部分先驗(yàn)信息形成閾值、④無(wú)干擾統(tǒng)計(jì)分布部分(先驗(yàn)信息統(tǒng)計(jì)假設(shè)下檢測(cè)形成閾值)。其中:①為固定閾值檢測(cè),②和③為自適應(yīng)閾值的CFAR檢測(cè),④為非參量CFAR檢測(cè)。

屬于自動(dòng)檢測(cè)范疇的CFAR檢測(cè)的雜波背景可歸納為均勻雜波背景、雜波邊緣和多目標(biāo)背景三種典型情況。瑞利分布(Rayleigh distribution)適用于一般雜波的描述,利用均值類CFAR檢測(cè)技術(shù)可以較好地實(shí)現(xiàn)虛警率的恒定。均值類CFAR適用于在空間上統(tǒng)計(jì)平穩(wěn)的背景,它在檢測(cè)單元前后沿各有一個(gè)覆蓋若干距離單元的滑動(dòng)窗,利用滑動(dòng)窗中參考采樣的均值,形成前后沿局部估計(jì),再對(duì)局部估計(jì)進(jìn)行平均、選大、選小或加權(quán)平均,即可確定檢測(cè)單元的背景雜波平均功率估計(jì)[5-6]。

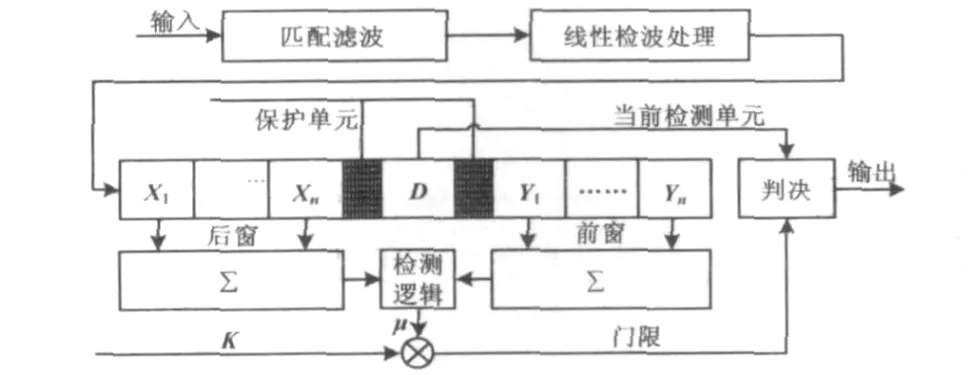

鑒于信號(hào)可能會(huì)跨越到前后鄰近單元中,檢測(cè)單元及其鄰近前后距離單元一般不包括在平均窗內(nèi),若檢測(cè)單元中信號(hào)幅度大于距離單元滑動(dòng)窗內(nèi)均值的K倍,則認(rèn)為檢測(cè)到的是目標(biāo)信號(hào)。CFAR算法模型如圖1所示。

圖1 CFAR算法模型Fig.1 Algorithm model for CFAR

回波序列送入傳輸延時(shí)線,延時(shí)線中央單元D為當(dāng)前檢測(cè)單元,其相鄰兩側(cè)各有一個(gè)保護(hù)單元(黑實(shí)線),左邊X1,…,Xn個(gè)單元組成后窗,右邊 Y1,…,Yn個(gè)單元組成前窗。前后窗分別求和后送往檢測(cè)邏輯,若檢測(cè)邏輯輸出μ為前后窗和的平均值,則為均值恒虛警(CA-CFAR);若μ為前后窗和的選小值,則為平均選小恒虛警(SO-CFAR);若μ為前后窗和的選大值,則為平均選大恒虛警(greatest-of constant false alarm rate,GO-CFAR)。

當(dāng)一種檢測(cè)器在干擾環(huán)境下的檢測(cè)性能獲得改善時(shí),它在邊緣雜波環(huán)境下的虛警控制能力往往會(huì)變差,這是由CFAR檢測(cè)方式本身的特點(diǎn)所決定的。CACFAR檢測(cè)器在雜波邊緣會(huì)導(dǎo)致虛警率的上升,而在多目標(biāo)環(huán)境中將導(dǎo)致檢測(cè)性能下降。在干擾目標(biāo)位于前沿或后沿滑窗之一的多目標(biāo)情況下,SO-CFAR方法能分辨出主目標(biāo),它緩解了由于多個(gè)空間鄰近干擾目標(biāo)引起的CA-CFAR檢測(cè)器檢測(cè)性能下降的問(wèn)題,其取兩個(gè)局部估計(jì)的較小者作為總的雜波功率水平估計(jì)。為了對(duì)抗雜波邊緣,GO-CFAR取兩個(gè)局部估計(jì)的較大者為總的雜波功率水平估計(jì)。GO-CFAR在雜波邊緣環(huán)境中能保持較好的控制虛警性能。

對(duì)于不大可能出現(xiàn)緊臨目標(biāo)且雜波嚴(yán)重不均勻的場(chǎng)合,通常更關(guān)注雜波邊緣的虛警[7-8]。考慮到單元平均選大(GO-CFAR)可以在雜波邊緣成功避免虛警,易于硬件實(shí)現(xiàn)。因此,該設(shè)計(jì)采用 GO-CFAR方法實(shí)現(xiàn)。

2 FPGA設(shè)計(jì)難點(diǎn)

由于在艦載雷達(dá)工作環(huán)境中,云、雨、氣旋、湍流、海雜波等都會(huì)導(dǎo)致雷達(dá)接收回波呈現(xiàn)非高斯特性,為了克服CFAR設(shè)計(jì)方法在這些非均勻的雜波環(huán)境中出現(xiàn)明顯弱化的問(wèn)題,工程實(shí)現(xiàn)中應(yīng)用普遍的是單元平均選大恒虛警率處理方法。FPGA實(shí)現(xiàn)恒虛警處理功能框圖如圖2所示。

圖2 FPGA實(shí)現(xiàn)恒虛警處理功能框圖Fig.2 Block diagram of FPGA implementing CFAR

在算法控制結(jié)構(gòu)、尋址方式和通信性能方面,通用DSP具有明顯優(yōu)點(diǎn)。但傳統(tǒng)DSP芯片結(jié)構(gòu)本質(zhì)上是串行的,它在大數(shù)據(jù)量、高速、運(yùn)算結(jié)構(gòu)相對(duì)簡(jiǎn)單的底層信號(hào)處理算法方面較FPGA硬件差。

在單元平均選大恒虛警率(GO-CFAR)設(shè)計(jì)過(guò)程中,當(dāng)值較大時(shí)排序的計(jì)算量很大。為便于DSP的串行處理,需要大量空間存儲(chǔ)數(shù)據(jù)和足夠的比較時(shí)間;而采用基于FPGA的流水FIFO處理,不僅節(jié)省存儲(chǔ)量而且提高了實(shí)時(shí)性。

設(shè)計(jì)實(shí)現(xiàn)時(shí)需要對(duì)平均選大模塊(GO-CFAR)的輸出μ乘以比例因子K(K取3~5)。通過(guò)分析圖2中前后窗各單元的情況可知,通過(guò)一個(gè)三輸入比較器即可完成兩次比較功能。當(dāng)輸出的檢測(cè)單元為最大值時(shí),即確認(rèn)有目標(biāo),從而完成對(duì)比較器的改進(jìn)。該改進(jìn)方法大大減少了資源的使用,避免了門(mén)級(jí)延時(shí)與線延時(shí)。圖2中虛線框代表的潛伏單元可通過(guò)多位D觸發(fā)器的級(jí)聯(lián)來(lái)實(shí)現(xiàn),但當(dāng)潛伏單元較多時(shí),這種方法顯得極為不便,而采用Xilinx提供的IP Core:RAM 2 based Shift Register,只需改變輸出地址即可實(shí)現(xiàn)不同周期的潛伏。

在CFAR的工程實(shí)現(xiàn)中,由于主脈沖周期和量化段的長(zhǎng)度是變化的。因此,不可能在一個(gè)主脈沖周期內(nèi)總是存在完整的量化段組。為防止對(duì)未處理完的量化段組丟失數(shù)據(jù)而造成過(guò)大的誤差損失,使得在遠(yuǎn)程部分的處理不能很好地抑制噪聲與雜波,需要在主脈沖來(lái)臨后,在下一個(gè)主脈沖時(shí)間內(nèi)處理新數(shù)據(jù)的同時(shí),接著處理好原來(lái)未完成的處理部分。

具體解決措施是在主脈沖到來(lái)時(shí),保持原來(lái)的處理狀態(tài)不變,同時(shí)保存所有下一步所需要的數(shù)據(jù),但計(jì)數(shù)器與累加器內(nèi)部所有數(shù)據(jù)清零。對(duì)于剛好中斷到累加器減計(jì)數(shù)部分時(shí),則重新加載原來(lái)的求和部分?jǐn)?shù)據(jù),并接著上一步的處理進(jìn)行。處理過(guò)程中的所有狀態(tài)均未改變,而是接著原來(lái)的部分進(jìn)行處理,所有的控制時(shí)序都是動(dòng)態(tài)的。

由以上分析可知,如果對(duì)N個(gè)數(shù)據(jù)進(jìn)行排序,則需要(N-1)×(N/2)個(gè)比較器和N2個(gè)寄存器。從排序延遲角度分析,N個(gè)數(shù)據(jù)排序需要N級(jí)流水操作。當(dāng)系統(tǒng)采用平均選大恒虛警后,數(shù)據(jù)傳輸延遲小、實(shí)時(shí)性較高。

3 實(shí)現(xiàn)與分析

利用Matlab軟件產(chǎn)生瑞利分布雜波與熱噪聲相疊加的目標(biāo)回波如圖3所示。

圖3 疊加回波Fig.3 Lapped echoes

將產(chǎn)生的雷達(dá)回波數(shù)據(jù)寫(xiě)入文件,然后通過(guò)C語(yǔ)言將浮點(diǎn)數(shù)轉(zhuǎn)換成適用于硬件處理的整數(shù)。在對(duì)硬件進(jìn)行仿真時(shí),將所產(chǎn)生的數(shù)據(jù)作為輸入信號(hào)進(jìn)行處理,從而得到快門(mén)限恒虛警仿真波形如圖4所示。

圖4 仿真波形Fig.4 Simulation curves

由Matlab軟件產(chǎn)生的目標(biāo)回波驗(yàn)證可以看出,整個(gè)回波只有一個(gè)目標(biāo)存在;而通過(guò)FPGA仿真全圖也可以得出相同的結(jié)論。當(dāng)整個(gè)仿真過(guò)程只出現(xiàn)高電平時(shí),即表明系統(tǒng)只檢測(cè)出一個(gè)目標(biāo),這正好與上面軟件產(chǎn)生的驗(yàn)證一致;數(shù)據(jù)測(cè)試可以正確地檢測(cè)出目標(biāo),而且在目標(biāo)周圍存在雜波干擾時(shí),也沒(méi)有出現(xiàn)虛警目標(biāo)的情況。因此,該設(shè)計(jì)基本上達(dá)到了檢測(cè)目的。

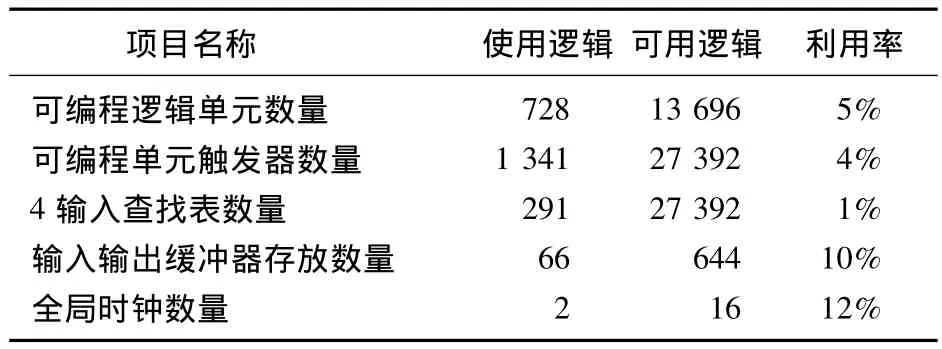

假設(shè)數(shù)據(jù)位寬為32位,保護(hù)單元為1,參考單元為16,F(xiàn)PGA芯片為 Xilinx Virtex 5 SX50T,使用Synplify Pro9.6.2,實(shí)現(xiàn)軟件為 ISE12.2,則實(shí)現(xiàn) GOCFAR的資源耗費(fèi)情況如表1所示。該GO-CFAR設(shè)計(jì)資源利用率報(bào)告的最高時(shí)鐘頻率為160 MHz。

表1 資源耗費(fèi)情況Tab.1 Consumptions of resources

衡量FPGA設(shè)計(jì)的兩個(gè)重要指標(biāo)是資源和速度,對(duì)具有16個(gè)參考單元的GO-CFAR,其最高工作頻率為160 MHz,可滿足實(shí)時(shí)性要求,使用量遠(yuǎn)小于所選芯片容量。

4 結(jié)束語(yǔ)

在各種噪聲和雜波的雷達(dá)回波中提取有用信號(hào)是CFAR處理設(shè)計(jì)的根本目的,在艦載雷達(dá)綜合抗雜波處理中對(duì)CFAR進(jìn)行處理是一項(xiàng)重要措施,其設(shè)計(jì)的好壞直接關(guān)系到后端數(shù)據(jù)處理的壓力,同時(shí)也會(huì)附帶處理?yè)p失。

本文針對(duì)實(shí)際使用環(huán)境,選擇抗多目標(biāo)干擾能力優(yōu)良的GO-CFAR處理方式,通過(guò)數(shù)據(jù)分析、采樣流水處理排序、數(shù)據(jù)流調(diào)節(jié)等措施,節(jié)省了存儲(chǔ)量,提高了實(shí)時(shí)性,減少了運(yùn)算量;而利用VHDL語(yǔ)言,采用自頂向下的設(shè)計(jì)方法實(shí)現(xiàn)GO-CFAR處理,縮短了開(kāi)發(fā)周期,提高了系統(tǒng)的處理速度,且在后端處理和處理?yè)p失之間取得了有效折衷。

[1]杜鵬飛,王永良.海雜波背景中的一種恒虛警率檢測(cè)方法[J].國(guó)防科技大學(xué)學(xué)報(bào):自然科學(xué)版,2005,27(3):54-57.

[2]鄭琦,陳棟,王其沖.艦載雷達(dá)復(fù)雜環(huán)境下的CFAR選擇[J].現(xiàn)代雷達(dá),2009,31(4):15 -18.

[3]何友,關(guān)鍵,彭應(yīng)寧,等.雷達(dá)自動(dòng)檢測(cè)與恒虛警處理[M].北京:清華大學(xué)出版社,1999.

[4]Rohling H.Radar CFAR thresholding in clutter and multiple target situations[J].IEEE Transaction on Aerospace and Electronic System,1983,19(4):608 -621.

[5]高亞軍,張冠杰,陳矛.基于FPGA的CFAR設(shè)計(jì)與實(shí)現(xiàn)[J].火控雷達(dá)技術(shù),2006,35(9):64 -68.

[6]羅成全.幾種恒虛警檢測(cè)器的應(yīng)用研究[D].南京:東南大學(xué),2007.

[7]楊大磊,陳璽,趙潤(rùn)山,等.基于FPGA的自適應(yīng)恒虛警檢測(cè)器研究[J].艦船電子工程,2008,170(8):95 -97.

[8]Zaimbashi A,Taban M R.Weighted order statistic and fuzzy rules CFAR detect or for weibull clutter[J].Signal Processing,2008,88(3):558-570.