快速鎖相無源三階環路濾波器的設計與檢測

王東虎

(湖北廣興通信科技有限公司,湖北 荊州 434007)

0 引言

在現代的無線通信設備中,鎖相環電路是很重要的組成部分。如何設計好高速、穩定的鎖相環電路是很多無線通信研發人員面臨的一個重要課題。鎖相環中的鑒相和分頻器均有集成芯片,壓控振蕩器也可訂做,而環路濾波器必須要經過仿真或設計計算。本文將探討2種快速鎖相的三階無源環路的濾波器的設計和3種環路鎖定時間的檢測手段。

1 鎖相環電路的組成及環路濾波器的作用

1.1 鎖相環電路的組成

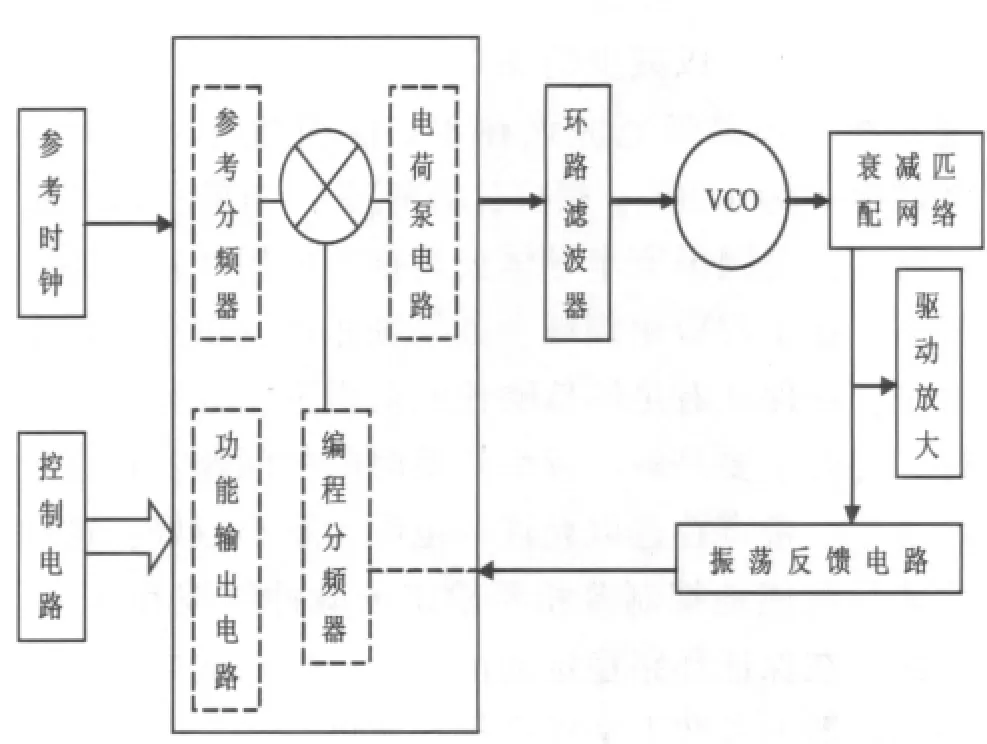

圖1所示為基本的鎖相環電路的組成。由參考時鐘、控制電路、集成鎖相芯片和環路濾波器、壓控振蕩器 (簡稱VCO)、衰減匹配網絡、振蕩反饋電路和驅動放大電路共同組成。其中環路濾波器的作用在鎖相環電路中尤為突出。

圖1 基本的鎖相環電路的組成

1.2 環路濾波器的作用

環路濾波器可濾除鑒相器輸出的誤差電壓和噪聲,它將鑒相器輸出的、含有紋波的直流信號平均化,并將此變換為交流成分少的、直流信號的低通濾波器。它除了濾出紋波外,還決定能否穩定地進行鎖相環控制的傳輸特性。三階環路濾波器比二階能更好地濾除參考源的邊帶頻率。在三階無源環路濾波器的基礎上,通過增加適當的硬件電路即可修改為快速鎖相的環路濾波器。

2 三階環路濾波的快速鎖相設計方法

2.1 三階環路濾波器設計參數對鎖相速度的影響

在實際的現代通信設備的應用中,在頻率波道切換時往往需要快速地鎖定鎖相環,特別是涉及到軟件信令的溝通和傳送,對鎖相時間的要求就特別苛刻。一般在不考慮電源與分布電容和共模噪音對VCO影響的情況下:時間常數越小,相位噪聲電平越小,截止頻率越高,鎖相速度越快,環路對鑒相器輸出脈沖的紋波抑制越弱,相位比較頻率中的頻率變化急劇;時間常數越大,截止頻率越小,對紋波抑制越好,相位噪聲越大,鎖相速度越慢。相位裕量越高,鎖相環的穩定性也越高,但鎖相時間變慢。相位裕量一般選擇45°,就是為了讓環路的穩定性和環路響應之間有一個好的折衷。相位比較的頻率越高,環路的相位噪聲就越小。環路帶寬應該盡可能地窄以減少偽噪聲,但是這會降低開關速度。通常環路帶寬應該在1 kHz和20 kHz,但是必須至少為1/20fCOM相位比較頻率;如果不在乎鎖定時間,美國國家半導體公司推薦使用2 kHz環路帶寬。在工程應用領域,如果鎖相環應用在跳頻系統中,在保證有足夠信噪比的前提下,帶寬越大越好,此時主要是解決頻率轉換時間的問題;在定頻系統中,帶寬在選取允許的范圍內越小越好,這樣才能盡可能地抑制鑒相器輸出的脈沖紋波和噪聲。因此,在保證環路穩定的前提下,可從選取設計環路濾波器的參數上來提高鎖相速度:

1)環路的帶寬盡可能地寬;

2)相位裕量 (也稱相位容限)盡可能地低。

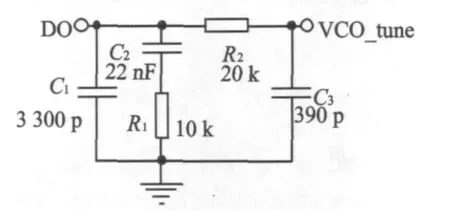

綜合上述討論,我們以中心頻率fVCO=465 MHz為例,VCO的增益靈敏度KVCO=2 MHz/V,電荷泵增益 KΦ=1.25 mA/2 π, 比較頻率 fCOM=200 kHz, 濾波器的環路帶寬fC=2 kHz,相位容限φ=45°,參考時鐘頻率fREF=12.8 MHz,衰減20 dB,電阻R2=20 kΩ,經計算或仿真得三階無源環路濾波器的參數,如圖2所示。

圖2 某三階無源環路濾波器的參數

2.2 增加三階環路濾波器硬件電路對鎖相速度的影響

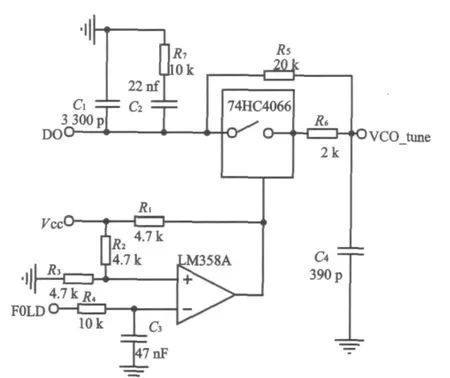

a)方法1:下面在圖2電路的基礎上,通過增加硬件比較電路和模擬開關,使環路的鎖相速度得到進一步的提高,電路改進后如圖3所示。

圖3 增加了硬件比較電路和模擬開關的改進電路

當鎖相環中的參考信號頻率和比較頻率有相位移狀態時,鎖相芯片中的F0LD管腳就變為低電平,無相位移時為高電平。將該管腳輸出的脈沖平均化,用低電平表示失鎖狀態,這時,比較器輸出高電平,模擬開關74HC4066接通,時間常數變小,鎖相速度加快。一旦環路鎖定,此時F0LD管腳就會輸出高電平,比較器LM358輸出低電平,模擬開關斷開,對環路濾波的時間常數切換變大,這時又可對相位比較頻率成分得到足夠大的衰減,輸出波形的寄生特性也不會變壞,改善了鎖相速度而使其變快。

用同樣的方式我們也可以對R7阻值進行模擬切換,若同時也將R5的阻值切換為適當值,則可以期待獲得更快的鎖相速度。

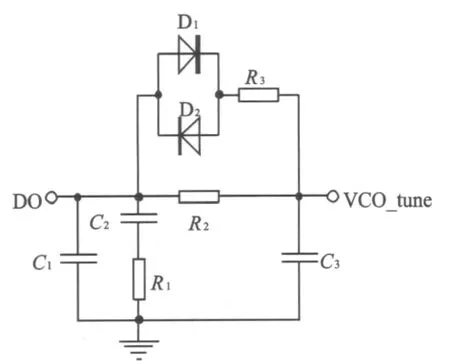

b)方法2:同樣可以用增加兩只極性相反的二極管并聯后再串聯一只電阻的方式以最少的元器件來提高鎖相的速度。改進后的電路如圖4所示。我們假設R3=2 kΩ,R2=20 kΩ。

圖4 增加了兩只極性相反的二極管的改進電路

根據圖4,頻率偏離大而失鎖時,鑒相器輸出大量的脈沖使D1和D2導通,環路濾波器的時間常數變小,環路快速鎖定。當鎖定時,鑒相器又無輸出脈沖。R3兩端幾乎等電位,D1和D2截止,環路濾波器的時間常數變大,又有利于降低寄生成分和抑制紋波噪聲。上述電路可大大提高鎖相速度,但鎖相后輸出頻率的寄生成分有一定的惡化。這是由于環路鎖定后,為了補償電容的漏電流與VCO的頻率飄移,鑒相器輸出窄脈沖,該窄脈沖使D1和D2導通,比較頻率成分的衰減量減小的緣故。

結合圖3和圖4,利用一個50 Ω衰減為3 dB網絡,通過訂做或自行設計一個中心頻率為465 MHz的壓控振蕩器VCO,加上SPF5043Z管子構成的驅動放大器,共同組成了完整的頻率鎖相環電路,通過該鎖相環電路可檢測驗證環路的鎖定時間。

3 鎖定時間的檢測驗證

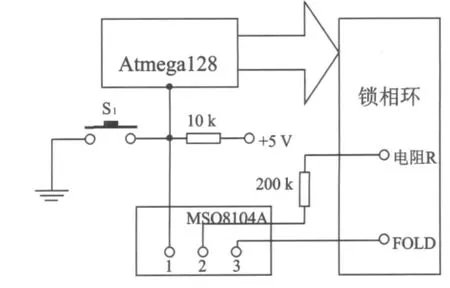

圖5所示為測試鎖相環電路的簡易框圖。其中測試按鍵S1分別連接基于Atmega128單片機為核心的測試夾具的中斷管腳上。同時又連接到數字示波器MSO8104A的IN1端口上。IN2端口串接200 kΩ電阻連接到鎖相環路濾波器上,具體連接到圖4中的R2和C3交叉點上或圖3中的R5和C4的交叉點上。IN3端口連接到鎖相芯片的鎖定管腳FOLD上。

圖5 測試鎖相環電路的簡易框圖

方法1:按照上述圖5連好線后,所有的設備裝置加電,選取IN1和IN2通道有效,MSO8104A設置IN1通道為下降沿觸發。當S1的中斷按鍵按下切換波道送頻和數據時,該點既是測試鎖相環時間觸發的起點又是送頻和數據的開始點,之所以選擇中斷按鍵就是為了讓單片機以最小誤差的方式實時修改鎖相環需要的可編程分頻數據。當環路鎖定時,此時環路濾波器輸出一穩定的直流電平,可從示波器上讀出從觸發點到穩定電平的時間差,該時間差即為鎖定時間。

方法2:按照上述圖5連好線后,所有的設備裝置加電,選取IN1和IN3通道有效,MSO8104A設置IN1通道為下降沿觸發。不同點就在于示波器的IN3端口接鎖相環芯片的鎖定管腳FOLD上。

a)當ATmega128單片機的初始化程序無頻和數據送出,但設置一旦鎖定時,FOLD管腳就為高電平。此時上電穩定后環路一直不鎖定,但按下中斷按鍵,程序送出頻和數據時,環路未鎖定時,FOLD輸出低電平;一旦鎖定,FOLD就輸出高電平。同樣可通過該按鍵觸發狀態的起始點和FOLD輸出高電平的時間差來測試鎖相環路穩定時的鎖相時間。

b)當ATmega128單片機的初始化程序有頻率和數據送出,同樣設置環路鎖定時FOLD管腳為高電平。通過此方法可以以最小誤差的方式測試出兩個頻道切換時鎖相環轉換時的鎖相時間。

方法3:用調制磁疇分析儀的測量儀器(HP53310A)進行測量,同樣用外部中斷按鍵S1觸發信號測量瞬態響應特性的結果。該儀器是測試鎖相環電路時常用的、非常重要的測量儀器。由于在屏幕上顯示測量壓控振蕩器的輸出信號的頻率,橫軸為時間,由于不受測量探頭的影響,因此,可以正確地進行高分辨率的測量。

4 結束語

本文在無源三階環路濾波器的基礎上,在鎖相環各種指標折衷穩定的前提下,要提高環路的鎖相速度,除了適當地增加濾波器中環路帶寬和降低相位裕量參數外,還可在三階環路濾波器的基礎上增加硬件電路來改善,并且通過3種技術手段來檢測驗證具體的鎖相時間。

[1]遠坂俊昭 [日].鎖相環 (PLL)電路設計與應用 [M].第1版.北京:科學出版社出版,2006:1-238.

[2]SAYRE C W[美].無線通信設備與系統設計大全 [M].第1版.北京:人民郵電出版社,2004:204-218.

[3]韓庫.淺議頻率合成器中環路濾波器的設計 [J].電子元器件應用,2005,7 (1):35-36.

[4]陳冬云.ATmega128單片機原理與開發指導 [M].第1版.北京:機械工業出版社,2005:64-67