基于FPGA 和Qt的圖像處理系統(tǒng)設計

王炳松,李汶洲,莊圣賢

(西南交通大學信息科學與技術(shù)學院,成都 610031)

1 引言

CIS 圖像采集處理系統(tǒng)存在數(shù)據(jù)量大,圖像質(zhì)量要求高,同時對便攜性、體積、功耗、成本也有極高的要求,因此在設計時必須綜合考慮這些因素,提出合理的設計方案。通常的方案是以FPGA 作為主處理器,先將采集到的數(shù)據(jù)全部存到外部緩存,然后從緩存中讀出數(shù)據(jù)處理,后經(jīng)D/A 轉(zhuǎn)換送至PC 端顯示[1]。這種系統(tǒng)雖很穩(wěn)定也不會出現(xiàn)掉數(shù)據(jù)的情況,但由于FPGA的硬件電路特性,只能做一些簡單的圖像處理,同時時效性、功耗、靈活性也會很差,不能滿足CIS 圖像處理的要求。另一種方案是,將采集到的數(shù)據(jù)在FPGA 內(nèi)部緩存預處理之后送DSP 做后續(xù)復雜處理[2],但有時我們只要實時獲取很好的圖像質(zhì)量,后續(xù)處理不是必須或特定的,并且對速度要求也不高(如便攜式掃描儀系統(tǒng)),采用FPGA +DSP 會加大復雜度和浪費資源。所以本設計提出一種既能滿足實時獲取圖像,又能做后續(xù)復雜處理的低成本方案。

2 系統(tǒng)結(jié)構(gòu)設計

CIS 圖像采集與處理系統(tǒng)主要由CIS 圖像獲取模塊、實時圖像濾波模塊、通信模塊、Qt 顯示與處理模塊以及相應的外圍電路組成,各個模塊的功能介紹如下:

圖像獲取模塊:將CIS 輸出的模擬信號,經(jīng)隔直、放大后,在FPGA的控制下完成A/D 轉(zhuǎn)換,將模擬信號轉(zhuǎn)換成數(shù)字信號,并將數(shù)字信號送圖像濾波模塊。

數(shù)字濾波模塊:該模塊的主要功能是:①在FPGA內(nèi)部,對進入該模塊的數(shù)字信號完成濾波;②將濾波后的數(shù)據(jù)寫入外部緩存器,并在濾波算法間隙將外部緩存中的數(shù)據(jù)讀出發(fā)往USB 傳輸模塊。數(shù)字濾波模塊是整個設計能否成功的關鍵部分。

通信模塊:配置好USB 固件后,在FPGA 控制下,圖像數(shù)據(jù)通過USB 傳送到PC 端。同時,USB 也可以接收PC 端的命令,并把命令讀出給FPGA,F(xiàn)PGA譯碼出命令后執(zhí)行相應的操作。

PC 端顯示與處理模塊:一方面,PC 端軟件接收到數(shù)據(jù)后,把數(shù)據(jù)編碼成圖像顯示出來。另一方面,用戶還可以在Qt 軟件上通過操作界面控制硬件工作,或?qū)D像做復雜的后續(xù)處理。

CIS 采集處理系統(tǒng)框圖如下圖1 所示。

圖1 CIS 采集處理系統(tǒng)結(jié)構(gòu)框圖

3 系統(tǒng)的具體實現(xiàn)方案

明確了各模塊的功能后,現(xiàn)在要解決的問題是:如何把這些模塊組合起來,讓它易于實現(xiàn),并保持長時間的穩(wěn)定性;同時尋求可靠的改進方法,讓圖像質(zhì)量更好。下面將詳細介紹各模塊的實現(xiàn)方式。

3.1 CIS 圖像獲取模塊

為擴展系統(tǒng)應用,該設計可選如下采樣模式:按接觸面大小有A4、A5、A6、A7 和任意幅面五種模式,按需求顏色有彩色、黑白、二值三種選擇,按分辨率有300DPI 和600DPI 兩種模式。可根據(jù)需要在PC 端選擇好,然后再開始采樣。由于CIS是行采集器件,所以必須要計算好行頻、每行的有效點數(shù)以及采樣的行數(shù),讓采樣出來的數(shù)據(jù)和PC 端設置的工作模式相對應,同時為了圖像色彩更加真實,必須調(diào)節(jié)好曝光時間。再者CIS的輸出是模擬信號,在進入FPGA之前,必須把它轉(zhuǎn)換成數(shù)字信號,而要獲得我們需要的數(shù)字信號必須先對A/D 內(nèi)部寄存器進行正確的配置。當然,為防止外部信號的干擾,數(shù)字信號在進入FPGA 之前會加隔離芯片對干擾信號隔離。

3.2 實時圖像濾波模塊

由于電子電路噪聲和低照明度或高溫帶來的傳感器噪聲大體上呈現(xiàn)高斯分布,為了消除這些噪聲而獲得較好的圖像質(zhì)量,本模塊采用高斯平滑濾波器。實現(xiàn)高斯濾波,常選用的高斯核有:3 ×3,5 ×5,7 ×7。更大的高斯核需要更多的緩存,也即意味著所需的FPGA 價格也就更高。綜合性價比,本設計選擇高性價比FPGA EP4CE10F17C8,此芯片內(nèi)部有46KB RAM,最高工作頻率可達200MHz,能滿足設計要求。

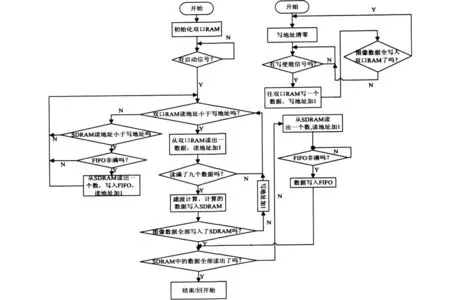

進入到FPGA 中的數(shù)字信號,實時寫入雙口RAM 緩存,同時從緩存中讀出所需的圖像數(shù)據(jù)構(gòu)成3 ×3的高斯核,然后進行高斯濾波算法,把計算出的值寫入SDRAM,去檢測是否可以從雙口RAM 中讀出數(shù)據(jù),如若能,繼續(xù)讀出數(shù)據(jù)計算,否則把SDRAM 中的數(shù)據(jù)讀出來寫入FIFO 中,以備下一個模塊使用。此過程圖像數(shù)據(jù)依次流入:實例化雙口RAM、SDRAM、實例化FIFO,具體的操作流程如下圖2 所示。

3.3 通信模塊

圖像傳輸采用外部FPGA 主控Slave FIFO 方式來實現(xiàn),因此USB 通信模塊由三部分組成。

(1)FPGA 主控部分

控制濾波后的數(shù)據(jù)有效地寫入已激活的USB大端點FIFO。在USB 固件中配置好端點后,F(xiàn)PGA中完成的只是檢測端點數(shù)據(jù)包非滿后,從上一模塊的FIFO 中讀出數(shù)據(jù),寫入有效的端點FIFO,直到圖像的數(shù)據(jù)全部寫完,回到初始狀態(tài)。

(2)USB 固件配置部分

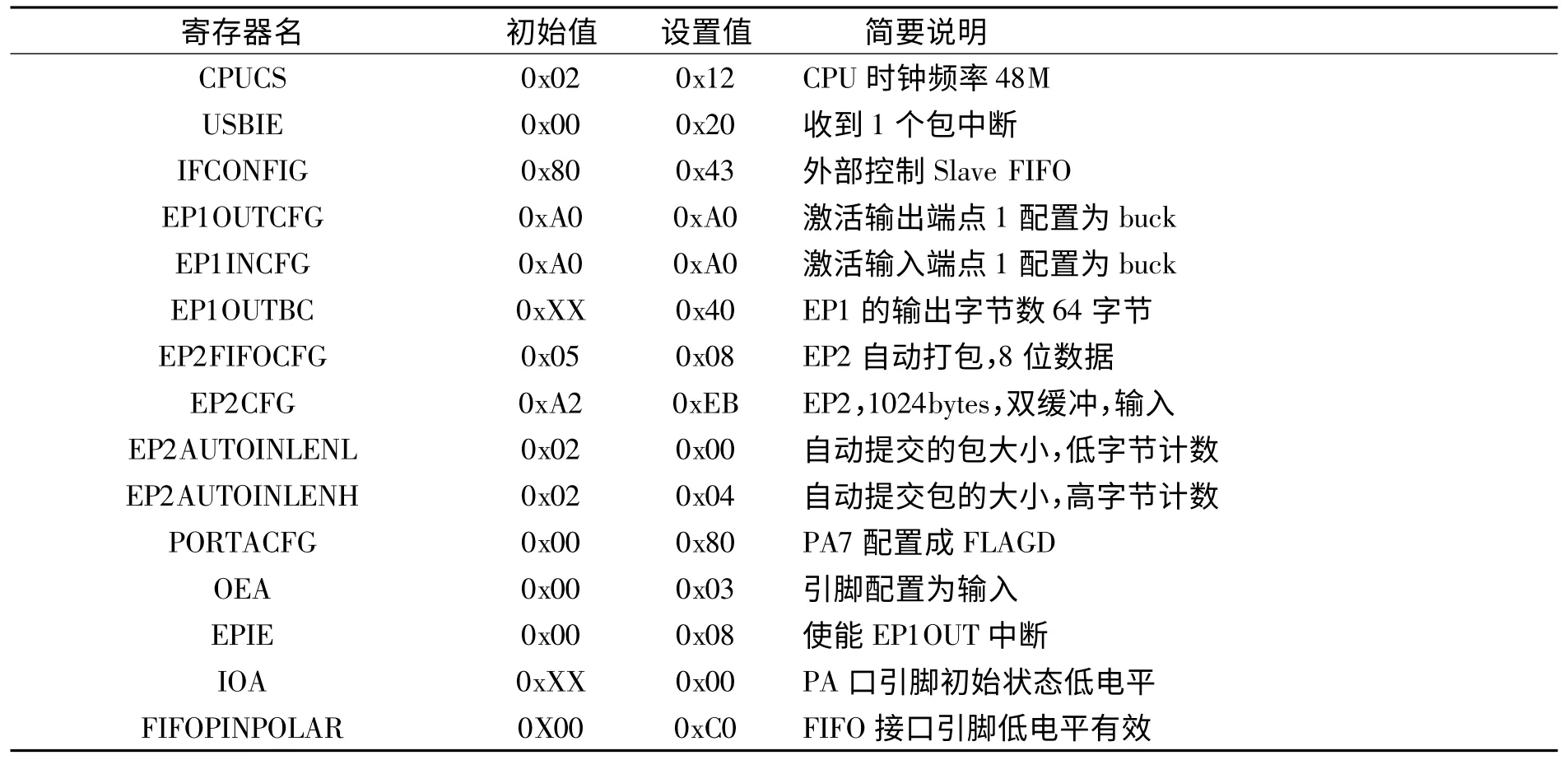

Cypress的安裝程序中提供了一些固件配置例程,通常的應用只要根據(jù)需要修改相應的程序即可,本設計是通過修改例程Bulkloop 中的bulkllop.c 完成的,其它的文件,包括端點配置或協(xié)議文件等,如非必要,盡量不要動。bulkllop.c 已經(jīng)為用戶搭好了架構(gòu),用戶只需在對應的函數(shù)中添加代碼即可。此處要完成USB 大小端點的配置、檢測啟動掃描信號及PC 與FPGA 間的通信。端點配置在TD_Init()函數(shù)中完成,需配置的寄存器如下表1 所示。

圖2 圖像濾波算法流程圖

表1 USB 固件配置的寄存器

檢測啟動信號在TD_Poll(void)函數(shù)中實現(xiàn),此函數(shù)會在USB 空閑時反復調(diào)用。PC 與FPGA的通信會在ISR_Ep1out(void)interrupt 0 函數(shù)中完成,當EP1OUT 中有數(shù)據(jù)時就會觸發(fā)中斷,接收PC 端發(fā)來的命令,驗證后把它傳遞給FPGA 中的編譯碼部分。

FPGA 編譯碼部分,譯碼USB 發(fā)送的指令,并控制FPGA 執(zhí)行相應的操作,同時也可編碼FPGA的狀態(tài)通過USB 告知PC 端。

3.4 PC 端顯示及處理模塊

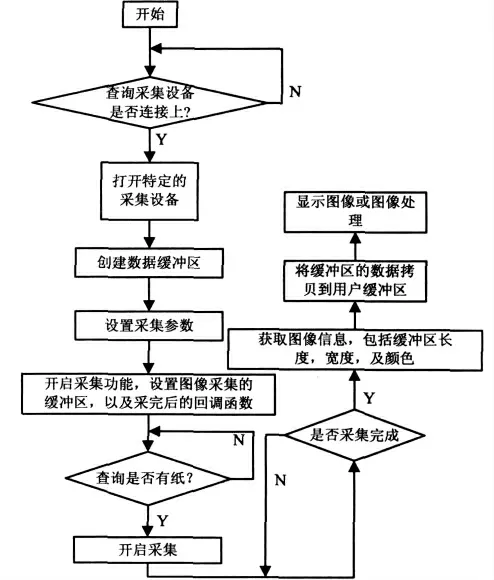

設計中存在USB 芯片與應用程序之間的通信,而應用程序和硬件交互信息要借助API 接口,所以本例調(diào)用了Cypress的CyAPI 庫接收USB的端點數(shù)據(jù)并應用Qt 庫函數(shù)將RGB 數(shù)據(jù)轉(zhuǎn)換成圖像顯示在Qt 軟件上。接收圖像數(shù)據(jù)流程如圖3 所示。

圖像顯示出來后,隨即可以利用Qt 庫函數(shù)或手寫算法完成圖像的后續(xù)處理。本設計調(diào)用QMtrix庫函數(shù)實現(xiàn)了圖像的放大、縮小、旋轉(zhuǎn)、鏡像,手寫算法完成了圖像的銳化、對比度飽和度校正、伽馬值矯正、自動裁剪、手動裁剪等操作,如有需要還可簡便地添加其它圖像處理算法。

下面僅對在Qt 界面中加入縮小動作做介紹,其它以此類推。因為Qt是利用信號槽機制完成界面操作的響應,信號會在某個特定情況下被觸發(fā),槽是等同于接收并處理信號的函數(shù)。所以首先在工具欄中加入縮小動作按鈕,然后給這個動作配上相應的槽函數(shù),當點擊縮小圖標時,信號被觸發(fā),槽函數(shù)響應事件并實現(xiàn)圖像的縮小算法,處理完成后,調(diào)用Qt的相關庫函數(shù)顯示圖像。圖4,圖5 分別是原圖與縮略圖。

圖3 Qt 軟件接收圖像數(shù)據(jù)流程圖

圖4 原始圖像

4 結(jié)束語

根據(jù)上面提到的設計思路完成了CIS 圖像采集處理系統(tǒng)的設計,并在軟硬件平臺上得到了驗證。實驗結(jié)果表明:CIS 采集完成后界面上可立即出現(xiàn)圖像,延時不超過1s。顯示效果如圖(5)所示,從圖中可看出已采集到了完整的圖像,但是由于PCB 板布線及抗干擾措施并沒做的很好,以及后期調(diào)試時間有限,所以后續(xù)圖像質(zhì)量改善的空間很大。

在設計中,數(shù)據(jù)傳輸用到的是Cypress 超低功耗芯片CY7C68013A,它的工作電壓為3.3V,容限輸入為5V,而采集板上的最高電壓是CIS的供電電壓5V,所以可以借助USB 供電,滿足即插即用。

Qt 軟件是微軟旗下的開源跨平臺界面軟件,利用它可以方便的完成很多圖像處理操作,代碼不用重寫就可以再移植到其它操作平臺上,給后續(xù)的升級擴展帶來了很大方便。現(xiàn)在圖像處理應用非常廣泛,以此設計為基礎,只要稍加改動就能應用到許多軟硬件相結(jié)合的圖像處理系統(tǒng)中。

圖5 縮略圖像

[1]伍乾永,陳彬.基于FPGA的實時圖像數(shù)據(jù)采集模塊設計[J].微電子學,2010(3):453-456.

[2]羅戈亮,魯新平,李吉成.基于FPGA +DSP的實時圖像處理系統(tǒng)設計與實現(xiàn)[J].微處理機,2010(2):108-110.

[3]WaleWasfy,Hong Zheng.General Structure Design for fast Image Processing algorithms based upon FPGA DSP slice[R].IEEE ISEC 2010 國際計算通信控制管理研討會,2010:726-729.

[4]王誠,蔡海寧,吳繼華.Altera FPGA/CPLD 設計[M].北京:人民郵電出版社,2011.

[5]錢峰.EZ- USB FX2 單片機原理、編程及開發(fā)應用[M].北京:北京航空航天大學出版社,2006.

[6]譚安菊,龔彬.USB2.0 控制器CY7C68013 與FPGA 接口的Verilog HDL 實現(xiàn)[J].電子工程師,2007(7):52-54.

[7]鄭阿奇.Qt4 開發(fā)實踐[M].北京:電子工業(yè)出版社,2011.

[8][英]Mark Summerfield.Qt 高級編程[M].白建平,王軍鋒,閆鋒欣,白凈,譯.北京:電子工業(yè)出版社,2011.

[9]詹紅霞.Visual C ++6.0 程序設計[M].西安:西安電子科技大學出版社,2009.

[10]求是科技.Visual C++圖像處理典型算法[M].北京:人民名郵電出版社,2006.